如何创建一个high-level和object-oriented的模型

描述

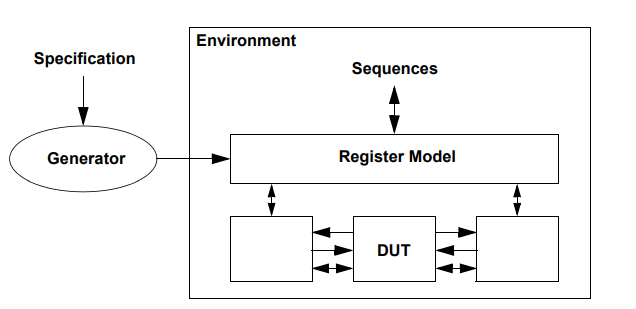

UVM register layer classes用于为DUV中的memory-mapped寄存器和内存的read/write操作创建一个high-level和object-oriented的模型。

这种抽象机制允许验证环境和测试用例从模块级迁移到系统级,而无需进行任何修改。寄存器模型还可以在寄存器之间移动唯一命名的字段,而不需要在验证环境或测试用例中进行修改(因为寄存器模型是按照字符串索引操作的,而不是按照字段offset操作的)。

UVM还提供了一个寄存器测试sequence库,你可以用来验证DUV中registers和memories的功能。

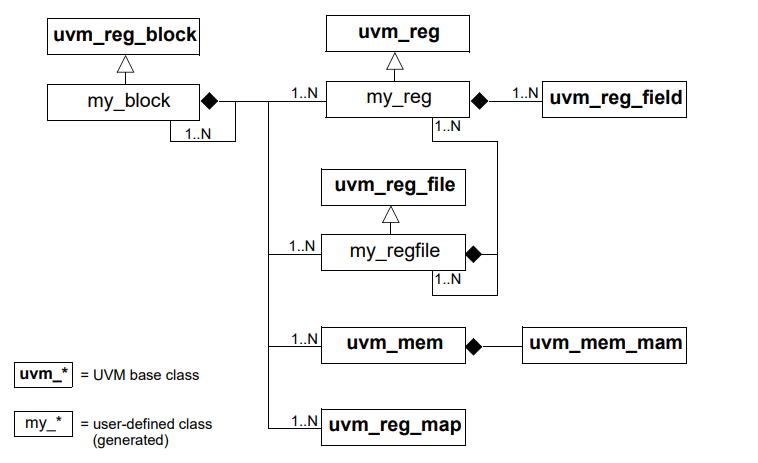

register model通常也是层次结构的。Blocks可以包含registers、register files和memories,以及其他Blocks。

register layer classes支持front-door a和back-door访问。

由于register layer classes涉及众多的细节,所以通常是由model generator从设计中的registers和memories的规格生成的。

register model 是一个register block的实例,它可以包含任意数量的registers、register files、memories和其他blocks。一个block通常对应于一个设计,它有自己的处理器接口,地址解码以及memory-mapped registers和memories。每个register file包含任意数量的registers和其他register files。每个寄存器包含任意数量的字段(fields),它们反映(mirror)了硬件中相应域段的值。

如果一个memories作为设计模块地址空间的一部分通过寄存器模型进行访问,那么该memories被认为是寄存器模型的一部分。

所有的数据域段都被建模为fields。fields代表一组连续的比特,完全包含在一个register中。

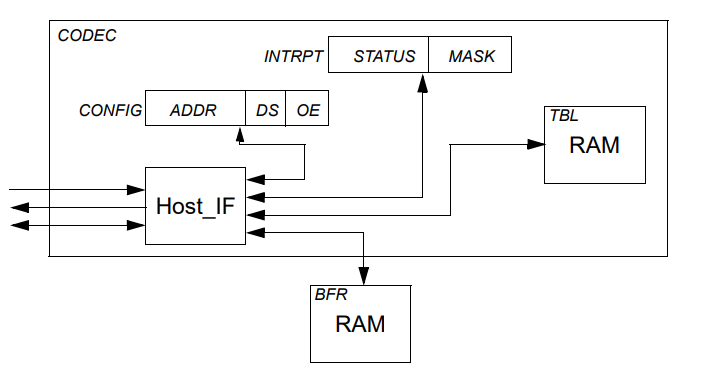

一个register可以横跨多个地址,重复的结构可以被建模为register arrays, register file arrays或者block arrays。下图显示了一个包含两个寄存器(分别有2个和3个字段)、一个内部存储器和一个外部存储器的设计。

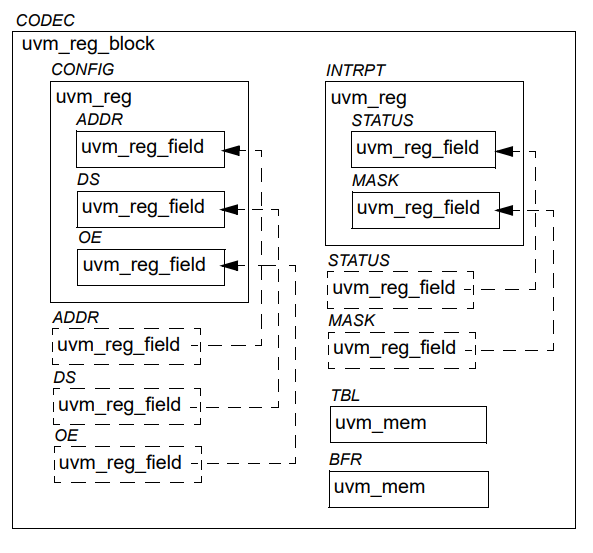

相应的寄存器模型如下:

当使用 register model时,fields、registers和memory是通过其相应的抽象类中的读写方法(不通过地址,而是通过字符串名称)来访问的。寄存器模型通过适当的总线驱动将这些抽象的访问变成特定地址的实际读写。

例 如,上图所示的CONFIG寄存器中的字段ADDR可以通过CODEC.CONFIG.ADDR.read() 方 法 访 问 。同 样 , BFR 存 储 器 中 的 位 置“7”可以用CODEC.BFR.write(7,value)方法访问。

-

Object-Oriented Python入門编程(一):认识类别2020-12-07 0

-

Object-Oriented Programming in2009-03-02 369

-

High-Level Modeling and Synthe2009-07-23 516

-

high-level protocol for CAN-bu2009-09-15 912

-

TPS65192,pdf(9 Channel Level S2010-11-03 1251

-

High-Performance Level-Shifter2009-02-02 1347

-

什么是CHILL (CCITT High Level Lan2010-02-22 615

-

Getting Started with Vivado High-Level Synthesis2018-06-04 3738

-

如何在HIGH LEVEL SYNTHESIS之前查找代码问题的资料说明2019-05-21 762

-

高层次综合技术(High-level synthesis)的概念2022-02-08 8266

全部0条评论

快来发表一下你的评论吧 !