接口中的modport连接模块都能看见什么

电子说

描述

在构建测试平台时,经常会用到interface用来简化模块和测试平台或者模块之间的连接,可以将一堆相关的信号封装在其中,为硬件模块的端口提供了一种标准化的封装方式,其中的modport(module port)结构对interface中的相关信号进行分组并指定方向,这样会使接口的定义条理更加清晰,明确了站在不一样的角度相关信号的输入输出方向。

例如在monitor中,信号大部分都是输入的,所以此时modport分组时将相关信号的方向都指定为输入,并且可以在具体模块定义的时候通过interface名直接使用modport名,那么此时就会有个问题:既然模块定义的时候直接了使用modport名,那么模块在例化的时候与interface的实例如何进行连接呢?本文将通过示例对此进行说明。

为了方便说明,文中相关模块的实现为“empty”,但是不影响其端口对于信号的可见性。

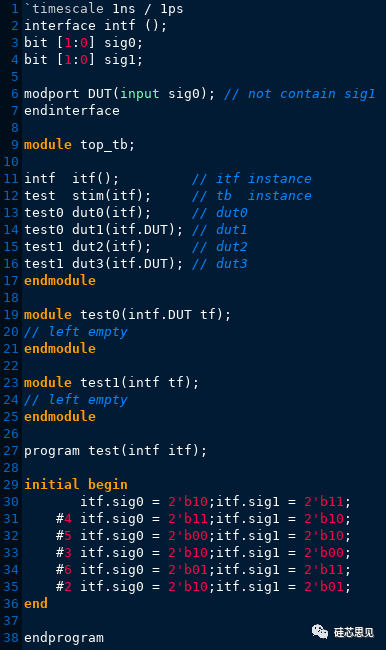

【示例】

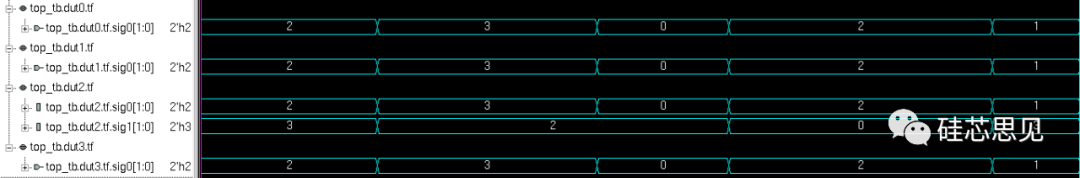

【仿真结果】

示例中,接口定义时指定了modport,其中只包含了sig0这一个变量,sig1并没有包含在内。test0定义端口列表采用“接口名.modport名”方式声明了接口变量,而test1定义端口列表采用“接口名”方式声明了接口变量。在模块例化时,dut0与“接口实例名”直接连接;dut1与“接口实例名.modport名”直接连接;dut2与“接口实例名”直接连接;dut3与“接口实例名.modport名”直接连接;

通过仿真结果可以看到,test0的两个实例,不管实例与接口采用何种方式进行连接,此时在实例中仅能观测到接口中modport分组中的变量sig0,其实主要原因在于test0在定义时其端口列表就已经限定了仅访问接口分组DUT中的变量。所有的实例中只有dut2中可以观测到接口中所有变量,这是因为首先test1在定义时其端口列表采用了“接口名”方式,其次例化连接接口时也是直接与接口例化名直接相连,而dut3因为在与接口连接时,限制了仅与接口中的modport分组TB进行连接,所以在dut3中观测不到sig1的变化。

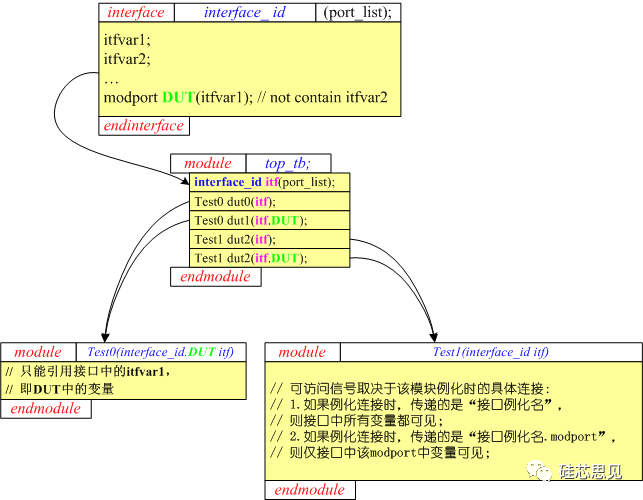

为此,可以将上例进行简化汇总之间关系如下图所示,即如果模块定义时指定的端口采用了“接口名.modport名 接口变量”的方式,那么不管这个模块在实例化时与接口实例如何连接,模块实例对于接口仅可观测到对应modport分组中的变量。而如果模块定义时指定的端口采用了“接口名 接口变量”方式,那么模块实例具体能够观测到接口哪些变量,则取决于实例化连接时与接口实例的连接方式。

审核编辑:刘清

- 相关推荐

- DUT

-

请问这个william hill官网 中如何插入图片,让别人看见我的帖子直接就能看见图片,而不需要下载图片看2016-01-13 0

-

DIY只有你能看见内容的显示器2016-06-08 0

-

使用SystemVerilog来简化FPGA中接口的连接方式2021-01-08 0

-

草履虫都能看得明白的FOC 入门教程2023-05-29 0

-

脑机接口中基于VxWorks的ARM嵌入式系统2009-03-29 477

-

隔离技术在嵌入式系统接口中的应用2010-01-26 721

-

如何将MPO接口光模块与LC接口光模块进行连接?2018-11-07 11728

-

智能机器人已经得到了广泛普及和应用 各行各业中都能看见它们的身影2019-01-09 3394

-

接口在Vivado Synthesis中使用时连接逻辑的用处2019-03-30 2202

-

dfrobotIIC接口模块专用连接线简介2019-12-02 1381

-

简单了解APP接口中的版本控制2020-11-03 2671

-

ADC时钟接口中的最小抖动2021-05-09 551

-

对于不同接口的光模块,该如何连接传输2021-09-07 8166

-

为什么要在串行通信接口中设置地线呢2022-02-02 3290

-

数字硬件建模SystemVerilog之Interface和modport介绍2023-04-28 4078

全部0条评论

快来发表一下你的评论吧 !