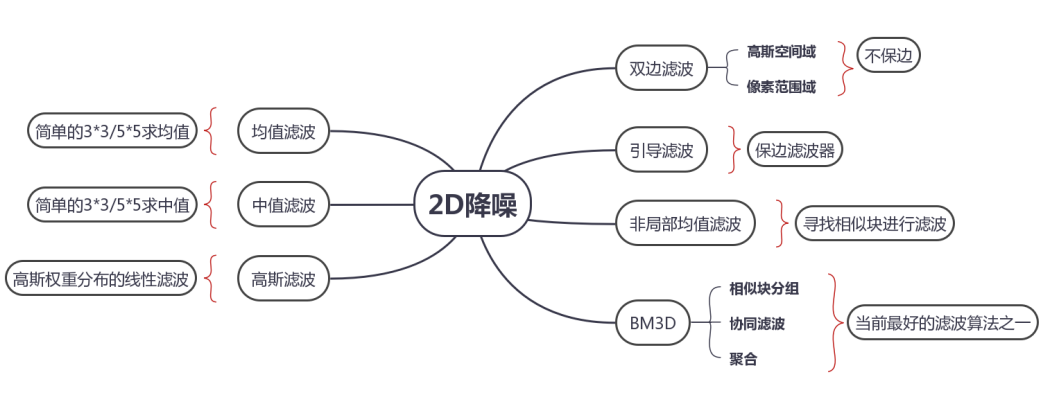

使用高级综合HLS,开发 2D 中值滤波器算法 (HLS) 。

概述

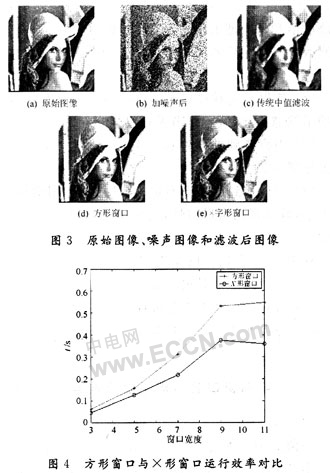

该项目包含使用高级综合 (HLS) 的 2D 中值滤波器算法的实现。该项目的目标是在不到 3 ms的时间内对测试图像进行去噪,同时消耗不到 25% 的可用 PL 资源。特征如下:

- 包含具有任意精度数据类型的高效数据类型管理。

- 采用 HLS 编译指示来确保最佳系统性能。

- 通过多个测试用例进行验证。

内容

该项目包含以下内容:

- 2D中值滤波器算法的源代码文件

- C 仿真文件

- 协同仿真文件

- 综合文件

- 包含干净和有噪声的图像数据的 CSV 文件

- 仿真和综合过程的屏幕截图

设置和安装

该项目已在 Vivado HLS 中设计和测试。要设置并运行项目:

- 克隆此仓库:git clone

- 打开 Vivado HLS 软件并导入项目。

- 加载包含图像数据的 CSV 文件。

- 运行 C 仿真以确保算法正常运行。

- 进行综合和协同仿真。

用法

将项目导入 Vivado HLS 后:

- 运行 C 仿真以验证中值滤波器的功能。

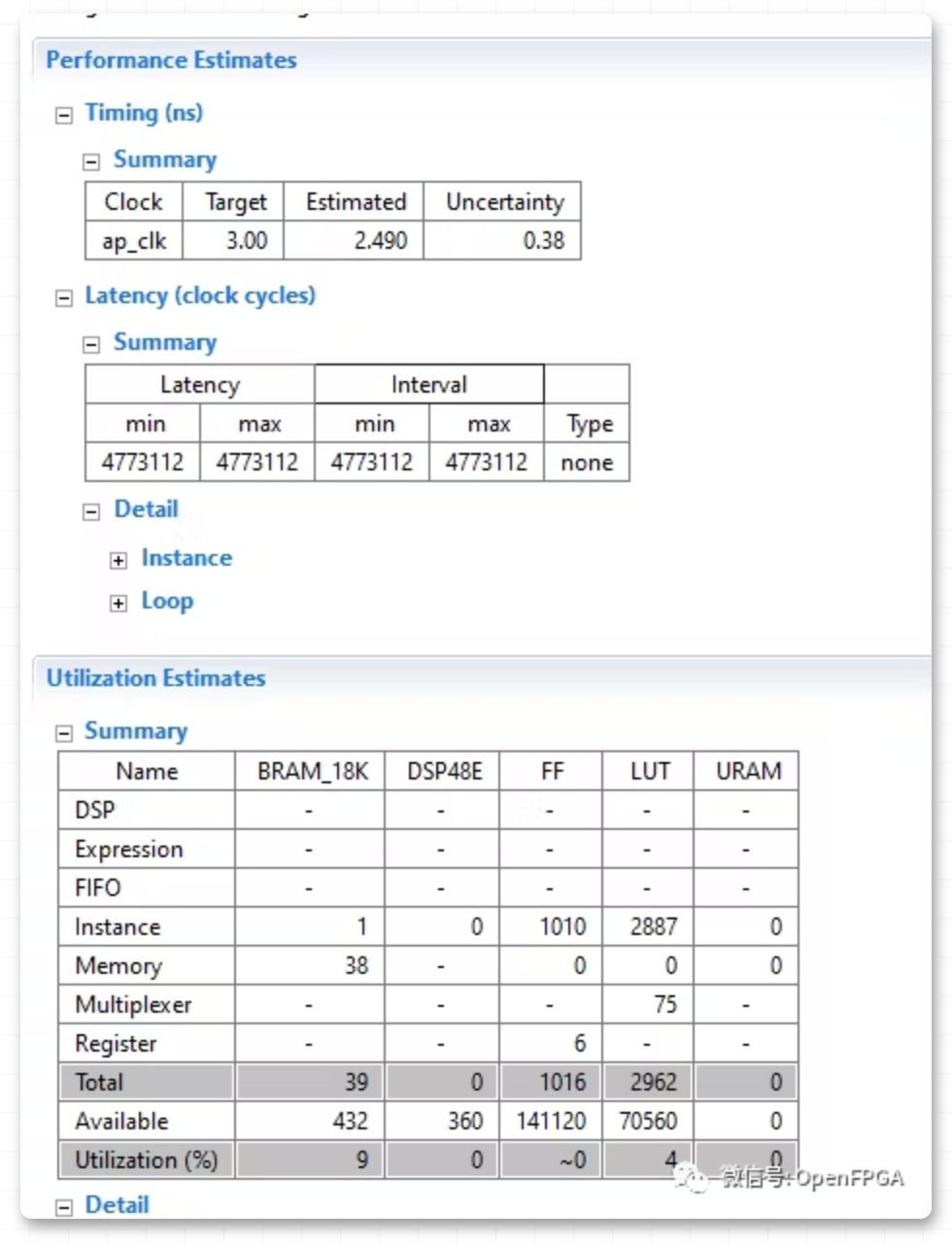

- 执行综合过程以查看资源利用率报告并进行必要的调整。

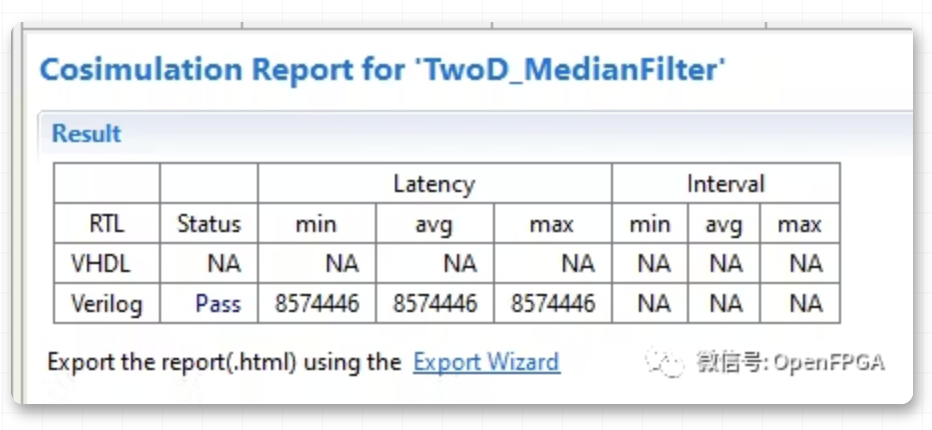

- 执行协同仿真以确保综合设计的行为符合预期。

请注意:可能需要根据所使用的 FPGA 板调整代码中的 HLS 编译指示以获得最佳性能。

最终设计应用于测试数据时,在不到 12 ms的时间内实现了去噪,总体 PL 资源利用率约为 13%。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

滤波器

+关注

关注

161文章

7839浏览量

178318 -

FPGA开发板

+关注

关注

10文章

122浏览量

31530 -

HLS

+关注

关注

1文章

129浏览量

24136

发布评论请先 登录

相关推荐

基于FPGA的中值滤波算法实现

` 本帖最后由 ninghechuan 于 2017-9-1 07:04 编辑

在这一篇开篇之前,我需要解决一个问题,上一篇我们实现了基于FPGA的均值滤波算法的实现,最后的显示效

发表于 09-01 07:04

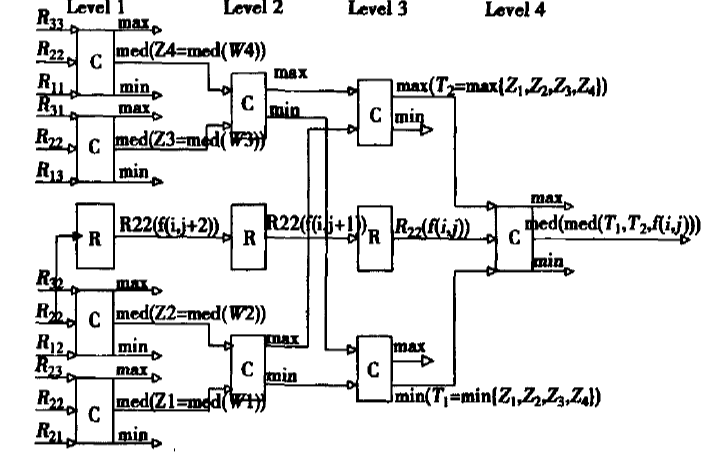

快速中值滤波的FPGA实现

中值滤波: 算法说明: 系统获取的图像在形成、传输、接收和处理的过程中,不可避免地存在着外部干扰和内部干扰。各种噪声随之而来,如图像传感器、信道传输、A/D转换等所产生

发表于 03-25 15:10

•234次下载

测井图像的多级中值滤波算法及其FPGA实现

微电阻率成像测井仪传输上来的地层信息数据需要滤波处理后才能真实地反映出地层中油层的信息,而中值滤波是图像预处理中常用的技术。本文介绍了标准中值滤波

发表于 12-31 09:20

•8次下载

2D中值滤波算法的设计实现

2D中值滤波算法的设计实现

评论