RQS_CLOCK-12时钟设置建议

描述

在本篇博文中,我们来聊聊“RQS_CLOCK-12”时钟设置建议以及它如何帮助达成时序收敛。

要求:

掌握如何生成和应用 report_qor_suggestions。

基本掌握 CLOCK_LOW_FANOUT 约束。

RQS_CLOCK-12:

RQS_CLOCK-12 建议属于专为 UltraScale 和 UltraScale+ 器件生成的自动增量式友好建议。

它使用“CLOCK_LOW_FANOUT”属性,并将该属性分配给时钟信号线或者一组寄存器,由全局时钟缓冲器根据其负载数目来驱动。

将该属性应用于时钟信号线时,全局时钟缓冲器的负载将被约束并放置到单个时钟区域内。

将该属性应用于一组寄存器时,在 opt_design 期间创建的现有全局时钟缓冲器的基础上,还会并行复制一个全新的全局时钟缓冲器。新全局时钟缓冲器的负载仅适用于该属性应用到的各组寄存器,并约束到单个时钟区域。

现在我们来看看 RQS_CLOCK-12 建议如何应用 CLOCK_LOW_FANOUT 来降低时钟偏差,进而帮助设计达成时序收敛。

假设已布线的设计中存在如下两个场景,其中存在错误的时钟偏差,导致从寄存器到全局缓冲器的控制管脚 (CE/CLR) 的路径上存在时序违例。

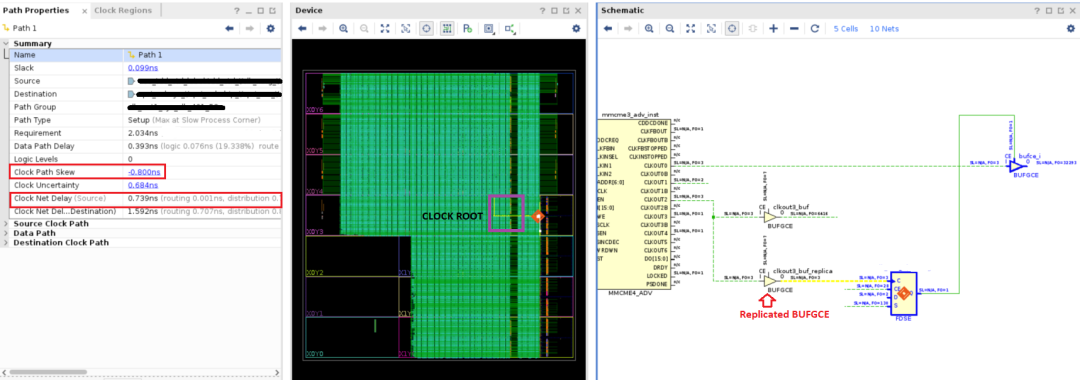

场景 1:

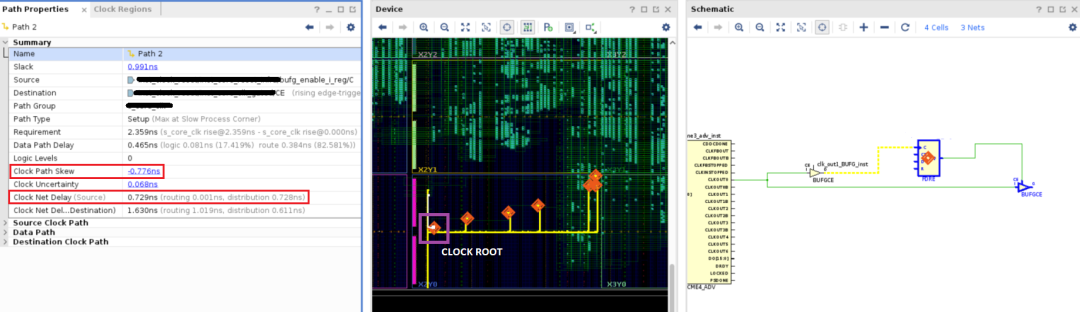

在这条时序收敛失败的路径中,时钟缓冲器 BUFGCE1 (clockout3_buf)、寄存器及其驱动程序 BUFGCE2 (bufce_i) 全都布局在同一个时钟区域内。驱动寄存器的 BUFGCE1 存在高扇出 (6419),且负载导致其时钟信号线遍布整个器件,如图高亮所示。

该工具所选的 CLOCK_ROOT 位置远离驱动它的全局时钟缓冲器,导致时钟信号线延迟过高且时钟偏差过高。

场景 1 的解决办法:

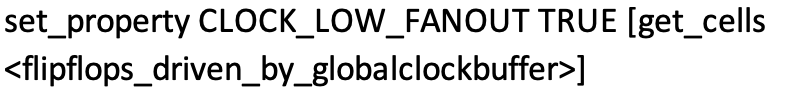

对寄存器应用 CLOCK_LOW_FANOUT,这样即可复制 opt_design 期间创建的原始 BUFGCE1 以创建新的 BUFGCE (clkout3_buf_replica),且仅将其用于驱动此关键寄存器。这样将把信号线约束到单个时钟区域内,从而减少时钟信号线延迟。

并且,由于时钟源和负载都位于相同时钟区域内,CLOCK_LOW_FANOUT 会强制将 clock root(时钟根)包含在相同时钟区域内,从而帮助降低时钟偏差。

对关键寄存器应用 CLOCK_LOW_FANOUT 后的板级原理图:

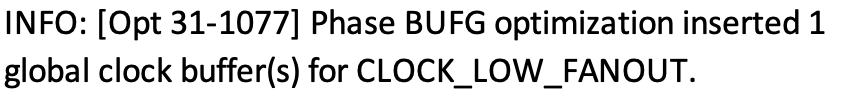

在 opt_design 的 BUFG 最优化阶段,在为 CLOCK_LOW_FANOUT 属性创建的全局时钟缓冲器上应该会显示一条消息。

例如:

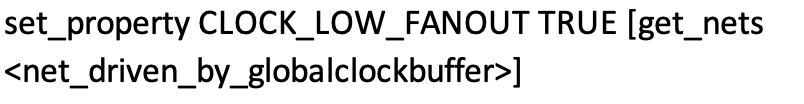

语法:

场景 2:

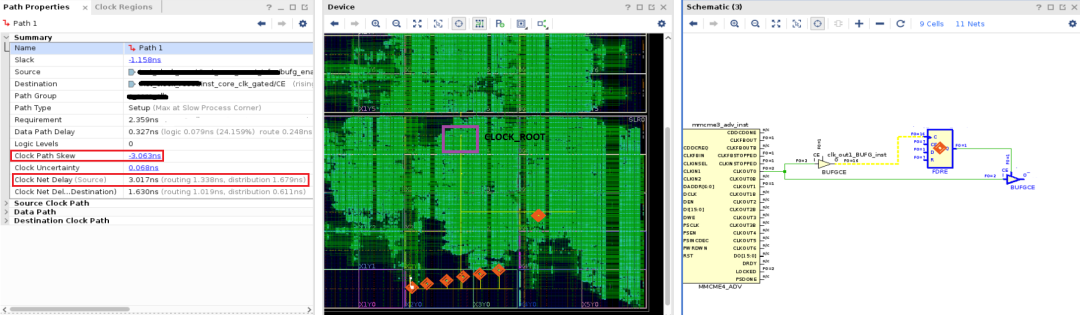

在这条时序收敛失败的路径中,时钟缓冲器 BUFGCE1 (clkout1_BUFG_inst)、寄存器及其驱动程序 BUFGCE2 同样全都布局在同一个时钟区域内。BUFGCE1 驱动寄存器的扇出较低 (16),但负载分布于多个时钟区域(以红色标记)。由此导致该工具所选的 CLOCK_ROOT 不同于驱动它的全局时钟缓冲器,进而导致时钟信号线延迟过高且时钟偏差过高。

场景 2 的解决办法:

当 BUFGCE1 扇出较低 (<2000) 但时钟负载遍布多个时钟区域时,对 BUFGCE1 直接驱动的时钟信号线应用 CLOCK_LOW_FANOUT 即可将其所有负载的布局都约束到单个时钟区域内。这将减少时钟信号线延迟。

现在,时钟源和负载都位于相同时钟区域内,因此 CLOCK_LOW_FANOUT 会强制将 clock root 包含在相同时钟区域内,从而帮助降低时钟偏差。

对时钟信号线应用 CLOCK_LOW_FANOUT 后的板级原理图:

语法:

总结:

在本篇博文中,我们学习了 2 个设计示例,其中演示了如何生成 RQS_CLOCK-12 建议以将 CLOCK_LOW_FANOUT 属性应用于由全局时钟缓冲器直接驱动的寄存器或时钟信号线。

审核编辑:汤梓红

-

msp430如何设置时钟及ad模块学习2017-11-17 6186

-

Logos系列FPGA时钟资源(Clock)用户指南2022-09-26 559

-

RQS设计收敛建议ID RQS_CLOCK-122023-07-12 556

-

CLOCK_DEDICATED_ROUTE约束应用2020-09-15 0

-

三个命令生成的报告中均可显示Clock Skew的具体数值2018-11-07 4849

-

如何在实现流程中将RQA与RQS结合使用的设计示例2020-09-29 3999

-

51单片机定时器时钟闪烁设置2021-11-11 681

-

STC12C5A60S2系列单片机PCA时钟源设置2021-11-18 702

-

DIY UTC时钟及设置PC时钟的选项2022-07-27 821

-

Gowin时钟资源(Clock)用户指南2022-09-14 324

-

Compact系列CPLD时钟资源(Clock/PLL)用户指南2022-09-26 556

-

怎样通过设置clock group来确认各个时钟之间的关系?2023-07-03 1593

-

时钟子系统中clock驱动实例2023-09-27 804

-

电源管理之clock驱动构架设计解决方案2023-11-29 944

-

时序约束一主时钟与生成时钟2024-11-29 355

全部0条评论

快来发表一下你的评论吧 !