ARM Cortex-M内核MCU的三重中断控制设计

电子说

描述

我们知道在 MCU 裸机中程序代码之所以能完成多任务并行实时处理功能,其实主要是靠中断来调度的,没有中断,CPU 就只能按顺序"呆板"地执行代码。很多人都说是中断能力赋予了 MCU 真正的灵魂,能正确认识和熟练使用 MCU 中断,基本上就算玩熟了这颗 MCU。

之前写过一篇 《中断处理函数(IRQHandler)的标准流程》,里面详细讲了中断处理函数里的标准代码流程与写法,这篇文章可让大家对 MCU 里的中断用法有个初步认识。今天以 ARM Cortex-M 内核 MCU 为例再来介绍下业界标准的三重中断控制设计:

一、外设事件中断控制

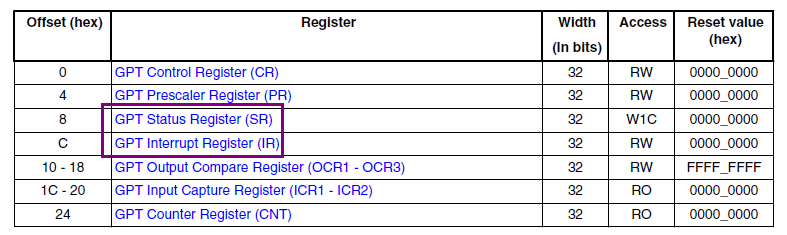

MCU 中最底层的中断控制针对的是外设里某个具体的事件,这个控制来自于外设模块本身,以恩智浦 i.MXRT 系列 MCU 的 GPT 定时器模块为例。如下是 GPT 模块寄存器列表,你可以发现其中有经典的 IR 和 SR 寄存器,SR 是事件状态寄存器,IR 是中断事件控制寄存器:

GPT 定时器一旦被使能,其运行状态(一共支持 6 个事件:超时、输入捕获 x 2ch、比较输出 x 3ch)都会实时记录在 SR 寄存器中,如果不在 IR 寄存器中将事件中断开启(默认是关闭的),那么就需要用户在代码里手动去查询 SR 寄存器置起的事件标志位以处理对应事件。

Note:SR 寄存器中置起的事件标志位需要在事件处理前手动清除掉。如果标志位不及时清除,可能会遗漏下一次事件的处理(比如先处理当前事件,后清除事件标志位,那么处理事件期间再次发生的事件就会被漏掉)。如果标志位忘了清除,同一次事件就会被处理两次及以上。

当然在实际应用中,为了节省 CPU 带宽,我们都是要开启外设事件中断的,MCU 厂商 SDK 包里一般都会提供相应接口函数(取自 fsl_gpt.h):

typedef enum _gpt_interrupt_enable

{

kGPT_OutputCompare1InterruptEnable = GPT_IR_OF1IE_MASK,

kGPT_OutputCompare2InterruptEnable = GPT_IR_OF2IE_MASK,

kGPT_OutputCompare3InterruptEnable = GPT_IR_OF3IE_MASK,

kGPT_InputCapture1InterruptEnable = GPT_IR_IF1IE_MASK,

kGPT_InputCapture2InterruptEnable = GPT_IR_IF2IE_MASK,

kGPT_RollOverFlagInterruptEnable = GPT_IR_ROVIE_MASK,

} gpt_interrupt_enable_t;

// 开启 GPTx 的 xx 事件中断

static inline void GPT_EnableInterrupts(GPT_Type *base, uint32_t mask)

{

base->IR |= mask;

}

// 关闭 GPTx 的 xx 事件中断

static inline void GPT_DisableInterrupts(GPT_Type *base, uint32_t mask)

{

base->IR &= ~mask;

}

使能 GPT1 的超时事件中断代码示例如下:

void periph_int_config(void)

{

// 初始化 GPT1...

GPT_Init(GPT1, &gptConfig);

// ...

// 开启 GPT1 的超时事件中断

GPT_EnableInterrupts(GPT1, kGPT_RollOverFlagInterruptEnable);

}

二、外设全局中断控制

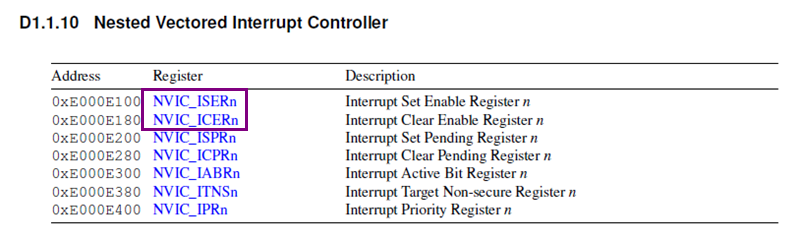

MCU 中第二层的中断控制针对的是整个外设,这个控制来自于 Cortex-M 内核的 NVIC 模块。如下是 NVIC 模块寄存器列表(取自 ARMv8-M 手册,除了 IABRn 和 ITNSn 寄存器组外,其余寄存器适用全部的 Cortex-M 家族),其中跟中断开关相关的是 ISER 和 ICER 寄存器:

当 MCU 中某外设(比如上一节里的 GPT)被使能后,即使其内部事件中断已被开启,也不意味着系统中断一定会被触发,因为 NVIC 里对于这个外设的全局中断开关(同一外设中所有事件共享一个系统中断资源,即一个中断号)还没有开启。ARM CMSIS 包里提供了外设全局中断控制函数(取自 core_cm7.h 文件):

#define NVIC_EnableIRQ __NVIC_EnableIRQ

#define NVIC_DisableIRQ __NVIC_DisableIRQ

// 开启 xx 外设的全局中断

__STATIC_INLINE void __NVIC_EnableIRQ(IRQn_Type IRQn)

{

if ((int32_t)(IRQn) >= 0)

{

__COMPILER_BARRIER();

NVIC->ISER[(((uint32_t)IRQn) >> 5UL)] = (uint32_t)(1UL << (((uint32_t)IRQn) & 0x1FUL));

__COMPILER_BARRIER();

}

}

// 关闭 xx 外设的全局中断

__STATIC_INLINE void __NVIC_DisableIRQ(IRQn_Type IRQn)

{

if ((int32_t)(IRQn) >= 0)

{

NVIC->ICER[(((uint32_t)IRQn) >> 5UL)] = (uint32_t)(1UL << (((uint32_t)IRQn) & 0x1FUL));

__DSB();

__ISB();

}

}

增加了使能 GPT1 的全局中断代码示例如下,其中 GPT1_IRQn 和 GPT1_IRQHandler 是固定名字,在 MCU 厂商提供的头文件(MIMXRT1176_cm7.h)和启动文件(startup_MIMXRT1176_cm7.s)里有定义。

void periph_int_config(void)

{

// 初始化 GPT1...

GPT_Init(GPT1, &gptConfig);

// ...

// 开启 GPT1 的超时事件中断

GPT_EnableInterrupts(GPT1, kGPT_RollOverFlagInterruptEnable);

// 开启 GPT1 的全局中断

NVIC_EnableIRQ(GPT1_IRQn);

}

// GPT1 的中断响应函数

void GPT1_IRQHandler(void)

{

GPT_ClearStatusFlags(GPT1, kGPT_RollOverFlagInterruptEnable);

// 中断业务处理代码

}

三、系统全局中断控制

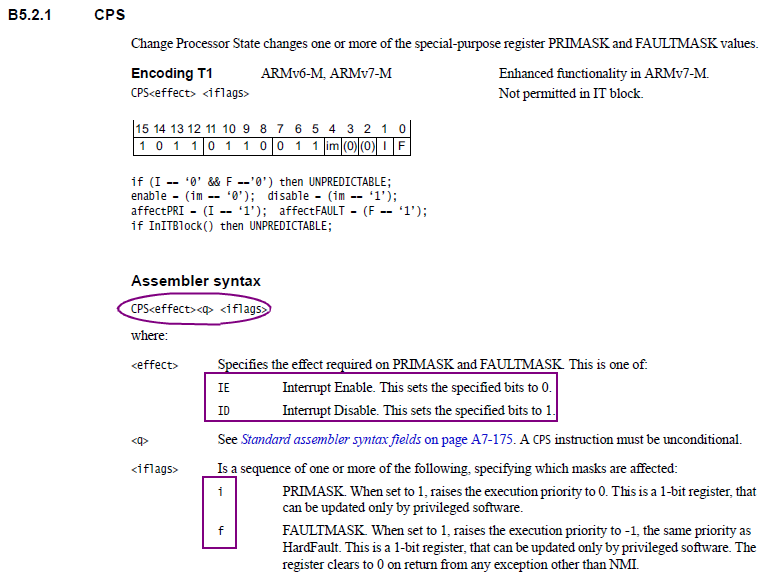

MCU 中最顶层的中断控制针对的是整个芯片系统,这个控制来自于 Cortex-M 内核的 CPS 指令。如下是 CPS 指令用法(取自 ARMv7-M 手册):

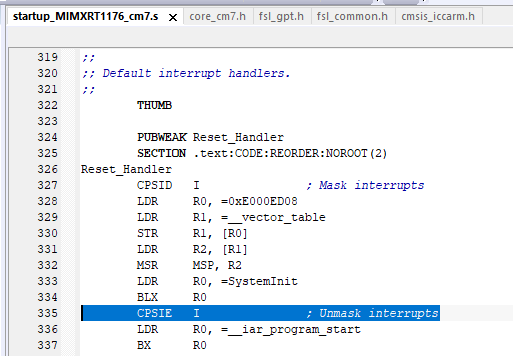

当你想对 MCU 整个芯片的所有中断进行统一开关控制时,就必须借助 CPS 指令。一般情况下开启芯片系统全局中断动作在 MCU 启动文件里已经做好了,所以在用户代码环境里常常不需要使能系统全局中断的动作。如下是 IAR 环境下 i.MXRT1170 启动文件中系统全局中断操作,基于汇编指令实现:

为了便于用户在 C 代码中操作系统全局中断,各 IDE 下均按同样的接口函数( __disable_irq / __enable_irq )做了封装实现。IAR 环境见 IAR SystemsEmbedded Workbench 8.50.6armincciccarm_builtin.h 文件,但是封装进其 Lib 了,没有暴露源码:

#include "iccarm_builtin.h" #define __disable_irq __iar_builtin_disable_interrupt #define __enable_irq __iar_builtin_enable_interrupt

Keil 环境见 Keil_v5ARMARMCLANGincludearm_compat.h 文件,我们可以看到源码:

static __inline__ unsigned int __attribute__((__always_inline__, __nodebug__))

__disable_irq(void) {

unsigned int cpsr;

#if __ARM_ARCH >= 6

#if defined(__ARM_ARCH_PROFILE) && __ARM_ARCH_PROFILE == 'M'

__asm__ __volatile__("mrs %[cpsr], primask

"

"cpsid i

"

: [cpsr] "=r"(cpsr));

return cpsr & 0x1;

#endif

#endif

}

static __inline__ void __attribute__((__always_inline__, __nodebug__))

__enable_irq(void) {

#if __ARM_ARCH >= 6

__asm__ __volatile__("cpsie i");

#endif

}

最终 GPT 例程里完整的三重中断使能代码应如下:

void periph_int_config(void)

{

// 初始化 GPT1...

GPT_Init(GPT1, &gptConfig);

// ...

// 开启 GPT1 的超时事件中断

GPT_EnableInterrupts(GPT1, kGPT_RollOverFlagInterruptEnable);

// 开启 GPT1 的全局中断

NVIC_EnableIRQ(GPT1_IRQn);

// 开启芯片系统全局中断

__enable_irq();

}

本文转载自痞子衡嵌入式 审核编辑:汤梓红

-

怎么实现嵌入式MCU中标准的三重中断控制设计?2021-11-29 0

-

ARM Cortex-M内核的相关资料推荐2021-12-27 0

-

Arm 10款 Cortex-M系列MCU内核对比2022-07-29 0

-

第三方的MCU内核中,Arm Cortex M系列为什么占主导地位2022-07-29 0

-

干货:对比看看Arm推出的10款Cortex-M系列MCU内核IP2022-07-29 0

-

国内MCU厂商90%都采用的Arm 的Cortex-M系列内核,优点在哪?2022-07-29 0

-

ARM Cortex-M 系列微控制器(ST)2009-11-02 952

-

传统的单片机和ARM较量 助推MCU踏上高端Cortex-M市场2018-04-28 1617

-

mcookie与单片机的关系_使用ARM Cortex-M MCU拓展单片机教学2021-11-30 652

-

一点理解之 CmBacktrace: ARM Cortex-M 系列 MCU 错误追踪库2021-11-30 545

-

Cortex-M中断及FreeRTOS中断优先级配置原理2022-02-08 658

-

分析ARM Cortex-M内核复位启动过程2023-03-20 2398

-

基于32位Arm Cortex-M内核N32系列MCU应用2023-03-28 908

-

Cortex-M 内核中断/异常系统、中断优先级/嵌套 详解2023-09-27 2226

-

瑞萨Cortex-M内核RA MCU的RT-Thread BSP制作教程发布2023-09-18 715

全部0条评论

快来发表一下你的评论吧 !