ADS VerilogA的权宜之计—直接解决ADS向量端口问题

描述

01

问题描述

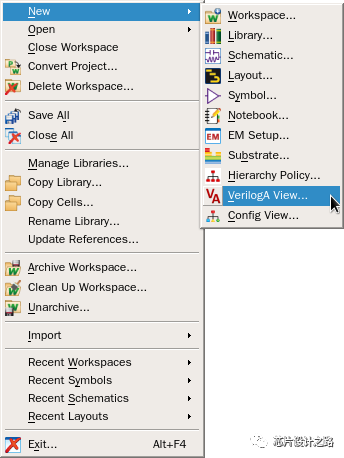

在ADS中建立一个Verilog-A模块,方法如下:

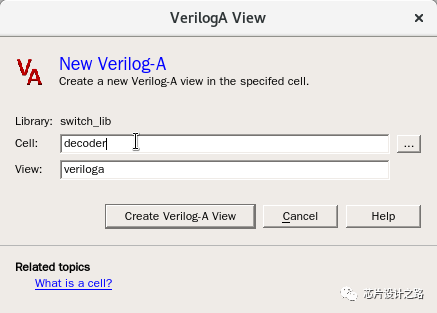

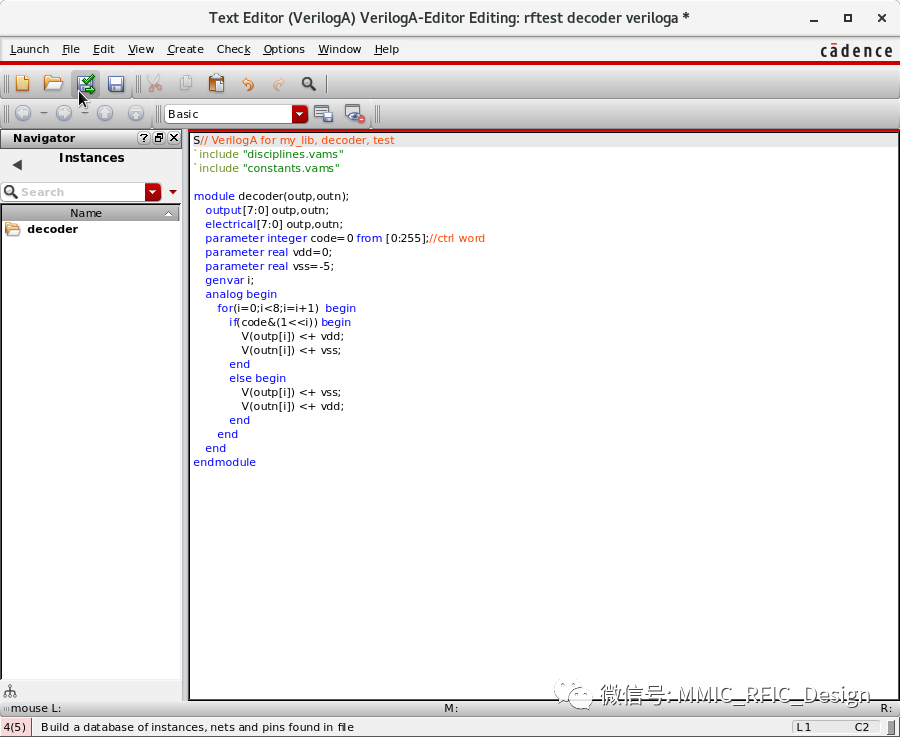

新建一个VerilogA View

在Verilog-A文本编辑器中添加以下代码:

// VerilogA for my_lib, decoder, test

`include "disciplines.vams"

`include "constants.vams"

module decoder(outp,outn);

output[7:0] outp,outn;

electrical[7:0] outp,outn;

parameter integer code=0 from [0:255];//控制码

parameter real vdd=0;

parameter real vss=-5;

genvar i;

analog begin

for(i=0;i<8;i=i+1) begin

if(code&(1<

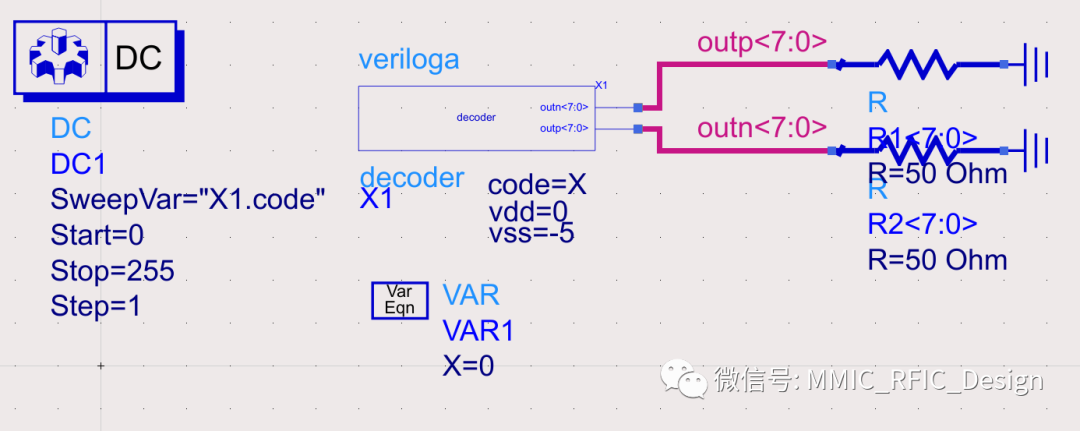

再给当前cell添加一个symbol view,包含两个Pin,跟Verilog-A中定义保持一致outp<7:0>、outn<7:0>。

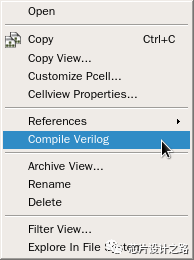

在veriloga view上右键选择【Compile Verilog】进行编译

编译通过会提示成功,否则会给出错误信息。

【注】作者在这里翻车了,本来标题写的是ADS应用技巧,但是作者发现当前使用的ADS不能正常编译这个decoder模块了,提示我symbol定义的端口outp<7:0>、outn<7:0>跟Verilog-A模块中定义的端口outp、outn不一致,我明确地知道是端口宽度不匹配导致的,但我坚持认为是软件的问题。

ERROR: Failed to compile verilog : Port names in verilog and symbol views do not match.

Symbol View Ports : outp<7:0> outn<7:0>

Verilog Module Ports : outp outn

Modify either verilog or symbol view of the cell : decoder

几年前用ADS2017的时候这个模块肯定是已经编译通过正常使用的,但毕竟作者是业余学习使用ADS,也没有人家的License授权,遇到这种问题也不好跟Keysight提……虽然可以将8位宽度的向量端口拆成8个独立的端口,但我认为这很不优雅!而且相同的代码,我在Virtuoso环境中都是可以完全正常使用的,所以上面的仿真结果实际上我是用Virtuoso跑出来的……如果有读者知道怎么解决这个问题,欢迎在公众号留言,或者发送邮件xhlyuestc@gmail.com交流,感激不尽!

02

权宜之计

好在ADS和Virtuoso都支持OA,因此只需要将Virtuoso编译好的VerilogA模块复制到ADS的library中就可以使用了。

在virutuoso中新建一个cell,类型选择VerilogA,粘贴同样的代码到编辑器中,点击build按钮,提示可以自动生成symbol即可:

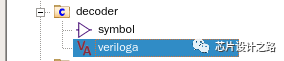

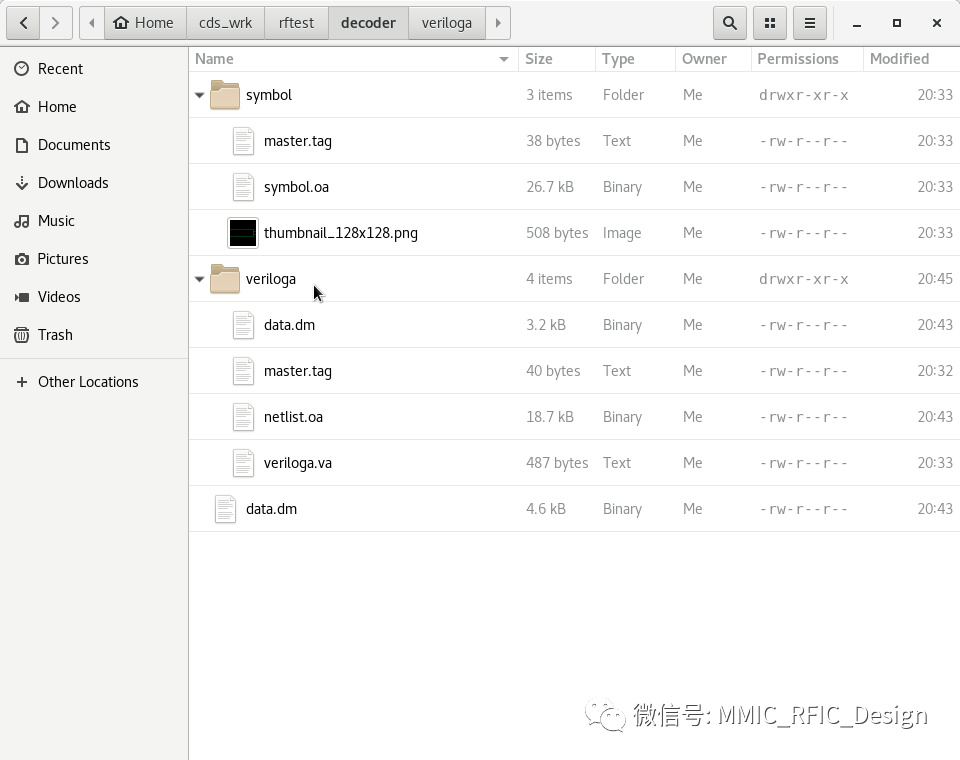

对应cell下面的文件结构如下图所示:

将decocer整个cell的文件夹复制到ADS对应工程的library里,然后就可以在ADS工程的Schematic中调用这个VerilogA Cell进行仿真了。

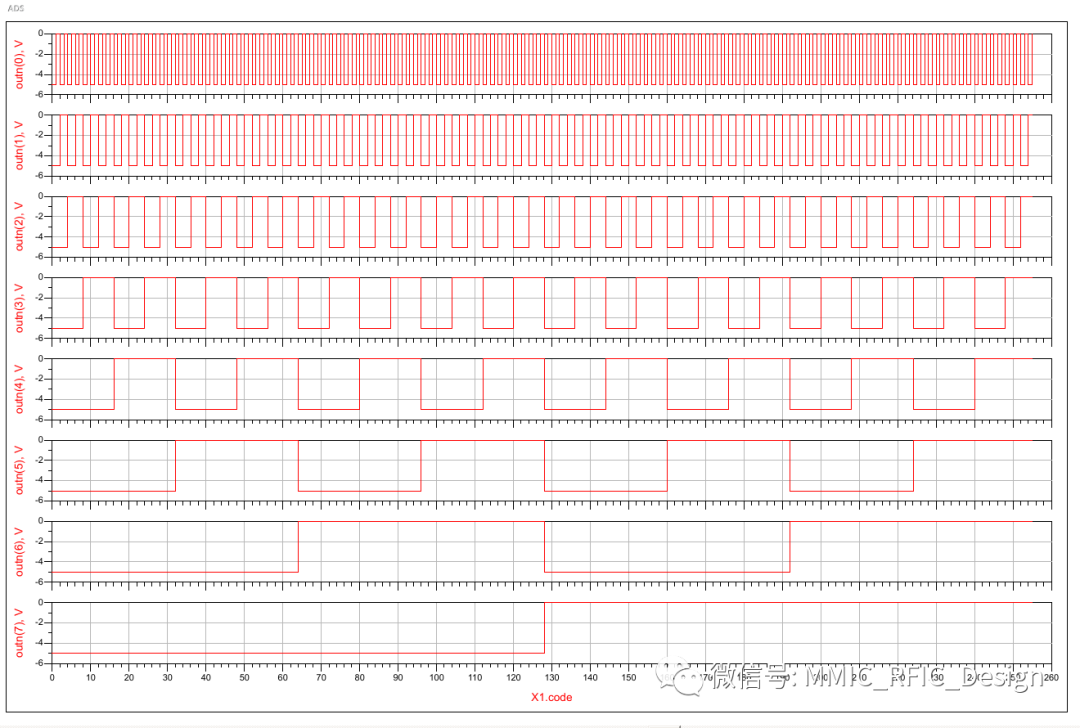

看看这个扫描输出的电压,是不是很像数字威廉希尔官方网站

里的二进制分频器,但那里是瞬态波形,这里是直流电压!

审核编辑:刘清

-

ADS7870/ADS7871 EVM2010-06-01 775

-

ADS1246/ADS1247/ADS1248pdf (242010-06-02 1183

-

ADS5481/ADS5482ADS5483,pdf (162010-06-03 674

-

ADS1113/ADS1114/ADS1115,pdf (U2010-06-03 1306

-

ADS6445/ADS6444/ADS6443/ADS644 MSPS quad channel A-D converters2010-06-04 941

-

ADS6245/ADS6244/ADS6243/ADS6242010-06-04 753

-

ADS6145/ADS6144/ADS6143/ADS6142010-06-04 719

-

ADS_ADS_Patch2013-09-13 971

-

ADS1286,ADS7816,ADS7817和ADS7822如何与80x51单片机的同步串口连接2018-05-29 1792

-

ADS快速入门:关于ADS的环境介绍2018-07-06 8096

-

ADS应用技巧—如何修改ADS的home目录?2024-02-26 2158

-

ADS6125/ADS6124/ADS6123/ADS6122模数转换器数据表2024-07-17 143

-

ADS6149/ADS6129/ADS6148/ADS6128模数转换器数据表2024-07-27 107

-

ADS8528、ADS8548和ADS8568时序注意事项2024-10-10 107

全部0条评论

快来发表一下你的评论吧 !