易灵思Ti180报错分析cannot connect to more than 4 different clocks per region on left and right

易灵思Ti180报错分析cannot connect to more than 4 different clocks per region on left and right

电子说

1.3w人已加入

描述

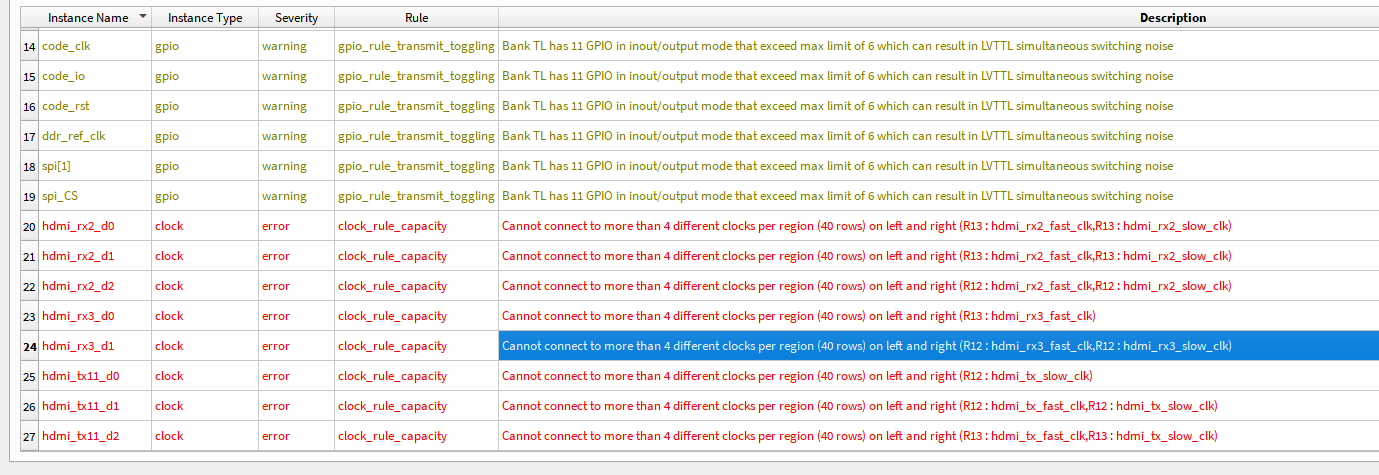

报错:cannot connect to more than 4 different clocks per region on left and right

今天在Ti180分配LVDS的时候出现了这个错误。原因是在pinout文件中对应的Clock Region中,不能超过4个时钟去驱动。

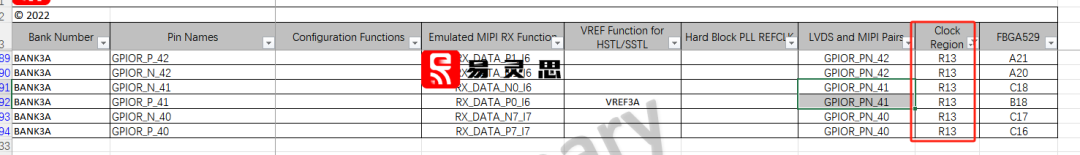

也就是GPIOR_PN_42,41,40三组差分对,不能由两组LVDS来驱动,因为每组LVDS时钟有lvds_fast_clk和lvds_slow_clk两个,两组就会有4个时钟在Region clock R13区域。

| Emulated MIPI RX Function | LVDS and MIPI Pairs | Clock Region |

| RX_DATA_P1_I6 | GPIOR_PN_42 | R13 |

| RX_DATA_N1_I6 | GPIOR_PN_42 | R13 |

| RX_DATA_N0_I6 | GPIOR_PN_41 | R13 |

| RX_DATA_P0_I6 | GPIOR_PN_41 | R13 |

| RX_DATA_N7_I7 | GPIOR_PN_40 | R13 |

| RX_DATA_P7_I7 | GPIOR_PN_40 | R13 |

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

三星S5PV210之芯灵思Sin210与TI Beaglebone Black之对比2013-05-18 0

-

为什么Crosstalk,Left-to-Right 和Right-to-Left是不一样的?2019-08-12 0

-

华大单片机HC32F003 error: L6235E: More than one section matches selector - cannot all be FIRST/LAST错误解决2021-11-23 1508

-

More Than Silicon是制胜模拟半导体市场的法宝2022-01-19 1460

-

易灵思Programmer工具的配置模式过程分析2022-03-09 1862

-

易灵思Ti60F100驱动LCD屏案例2023-07-10 1103

全部0条评论

快来发表一下你的评论吧 !