应对传统摩尔定律微缩挑战需要芯片布线和集成的新方法

电子说

描述

作者:应用材料公司 Kevin Moraes

从计算机行业的早期开始,芯片设计人员就对晶体管数量的需求永无止境。英特尔于1971年推出了具有2,300个晶体管的4004微处理器,激发了微处理器革命;到了今天,主流CPU已有数百亿的晶体管。

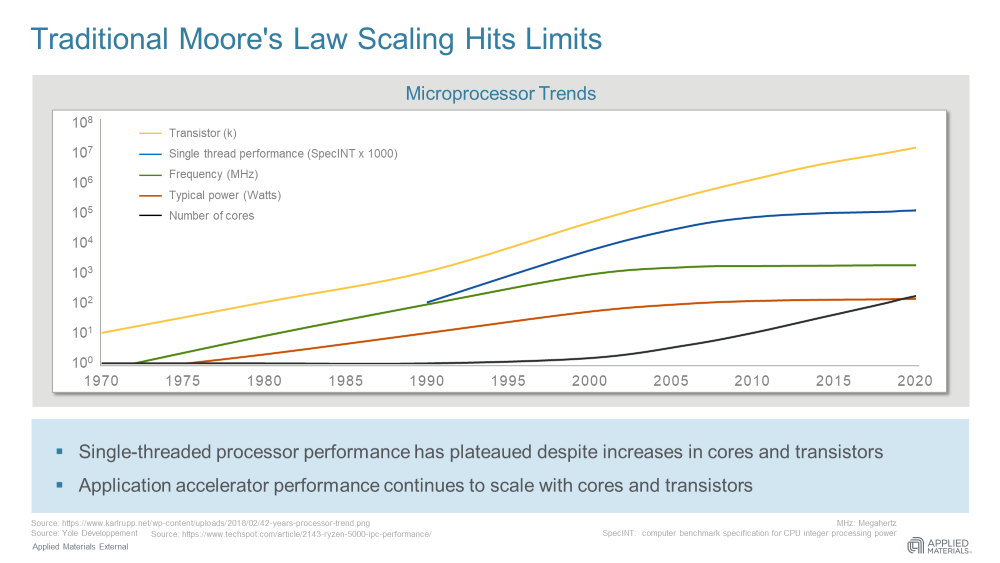

在过去多年的发展中,技术的变革在于——如何将更高的晶体管预算转化为更好的芯片和系统。在 2000 年代初期的丹纳德微缩时代,缩小的晶体管推动了芯片功率(Power)、性能(Performance)和面积成本(Area-cost)即PPAC的同步改进。设计人员可以提高单核CPU的运行速度,以加速现有软件应用程序的性能,同时保持合理的功耗和热量。当无法在不产生过多热量的情况下将单核芯片推向更高速度时,丹纳德微缩就结束了。而导致的结果就是——功率(下图中的橙色线)和频率(下图中的绿色线)改进也都停止了。

新的架构

如上图所示,设计人员使用越来越多的晶体管来添加CPU内核(上图中黑色线)以及并行化的软件应用程序,以使计算工作负载能够跨越更多的内核划分。最终,并行性达到了阿姆达尔微缩的极限(上图蓝色线),业界使用越来越多的晶体管来整合GPU和TPU。这些GPU和TPU继续随着核心数量的增加而扩展,从而加速了3D图形和机器学习算法等工作负载。今天,我们正处于一个以新架构为特征的时代——运算性能取决于内核和加速器,并由增加的晶体管预算和更大的芯片尺寸来驱动。但是,正如我将在本博客后面解释的那样,新的限制正在步步逼近。

EUV来了,现在怎么办?

EUV光刻技术已经到来,这使得在芯片上打印更小的晶体管特征和布线成为可能。但这些从业者也面临新的挑战。在国际电子器件会议(IEDM 2019)期间名为“逻辑的未来:EUV来了,现在怎么办?”的圆桌william hill官网 上,行业专家提出这种技术简化了图形化,但这并不是灵丹妙药。我列出了参会人员所讨论到的几个挑战,他们提出来的解决方案如今正在半导体行业的新路线图中逐步实现。

首先,william hill官网 提出了一个对某些人来说违反直觉的挑战:在芯片制造中,越小不一定越好,因为在同一空间中封装的晶体管触点和互连线越多,芯片的速度就越慢,能效就越低。

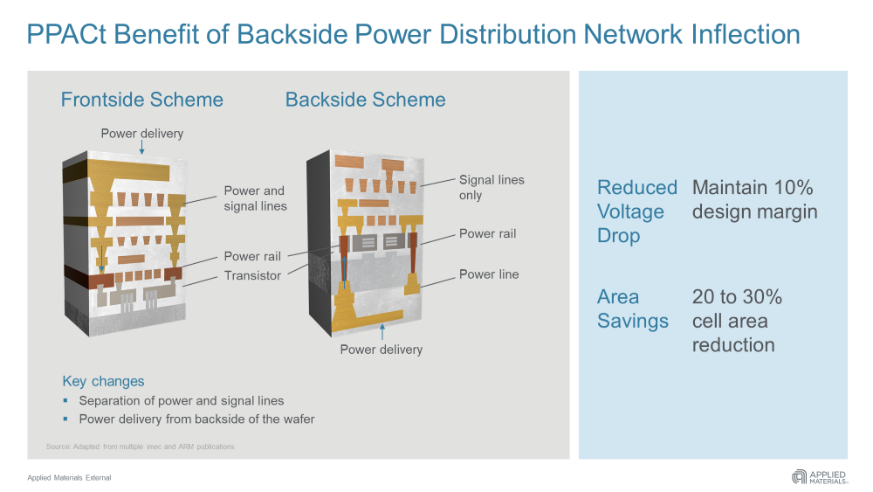

其次,该william hill官网 上预测了背面配电网络的到来——这是一种威廉希尔官方网站 协同优化(DTCO)技术,目前已出现在领先芯片制造商的路线图中。它允许逻辑密度增加高达30%,而无需对光刻进行任何更改。

我们现在正处于摩尔定律的第四次演变中,芯片制造商可以通过设计在各种节点上制造的芯片“然后使用先进的封装将它们缝合在一起”来降低成本。事实上,早在57年前,摩尔博士就已经预言了正在兴起的异构设计和集成时代。

应用材料公司已在5月26日的“芯片布线和集成的新方法”大师课上,进一步探讨了上述三个话题,同时我们也展示了材料工程和异构集成方面的创新,从而解决EUV微缩出现的电阻问题;在不改变光刻技术的情况下,实现微缩逻辑芯片的新方法;以及为设计人员提供几乎无限的晶体管预算。以下是本次大师课的内容概述。

提高功率和性能所需的布线创新

EUV的出现使制造商能够通过单次曝光打印25纳米间距内的特征,从而简化了图形化。不幸的是,使芯片布线更小并不能使它变得更好。EUV微缩的电阻难题存在于最小的晶体管触点、通孔和互连中,这就是材料工程需要创新的地方。

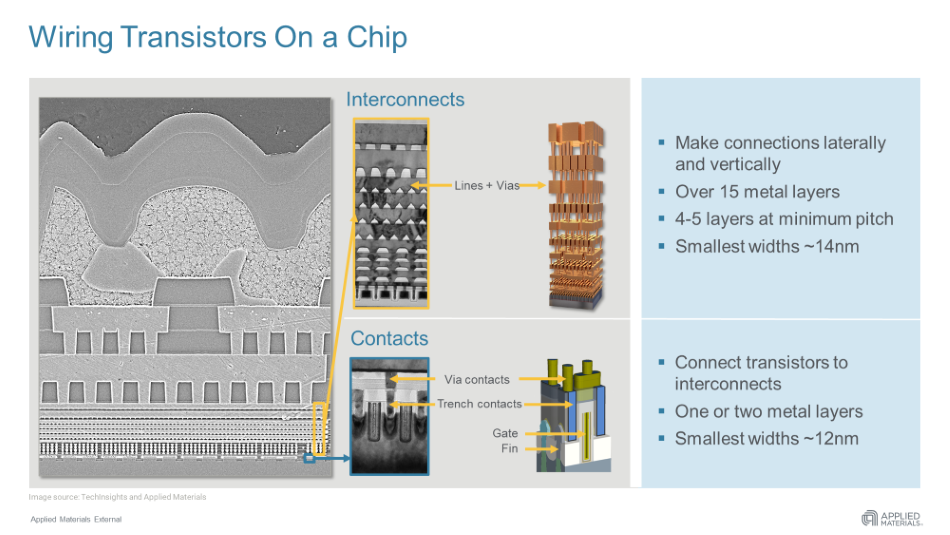

芯片中最小的导线是为晶体管的栅极、源极和漏极供电的触点。触点将晶体管连接到周围的互连线,该互连线由金属线和通孔组成,允许将电源和信号路由到晶体管并贯穿整个芯片。

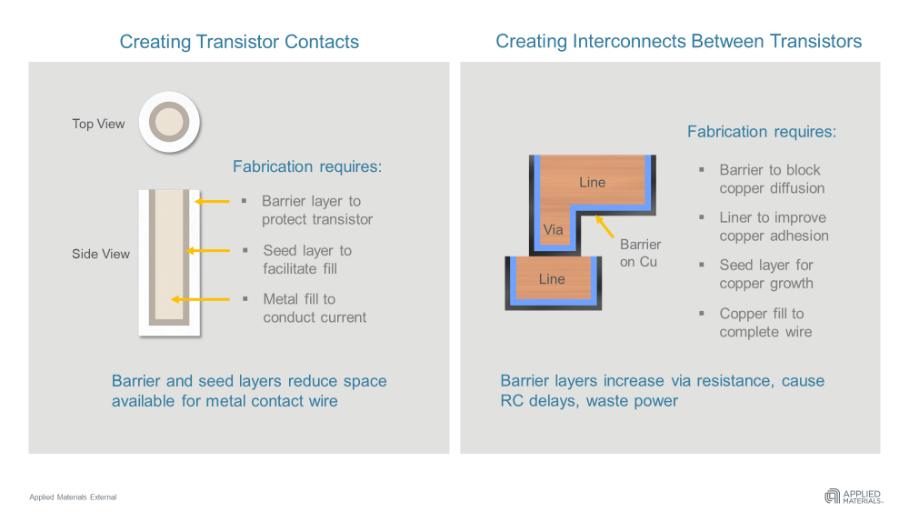

为了创建布线,我们在介电材料中刻蚀出沟槽,然后使用金属叠层沉积布线,该金属叠层通常包括一个阻挡层,可防止金属与介电材料混合;提升粘附的衬垫层;促进金属填充的种子层;晶体管触点使用钨或钴等金属,互连线使用铜。

但遗憾的是,阻挡层和衬垫层不能很好地缩小,并且随着我们使用EUV缩小沟槽图案,阻挡层和衬垫占用的空间比例增加,而可用于布线的空间减少了。布线越小,电阻越高。

而应用材料公司一直致力于开发新的技术,重塑芯片布线的设计和制造方式。

使用背面配电网络促进逻辑威廉希尔官方网站 微缩

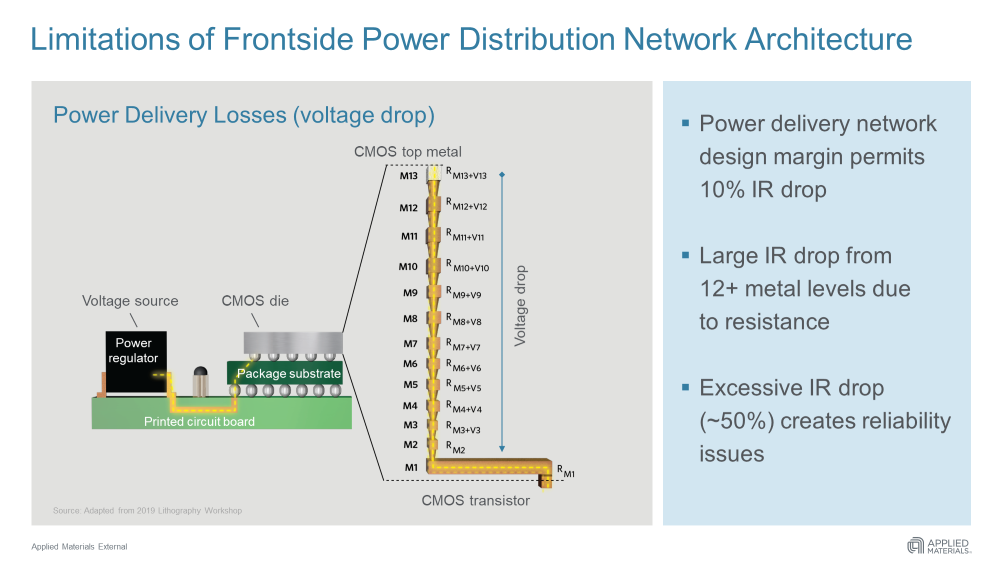

晶体管由电线网络供电,电线网络将电压从片外稳压器通过芯片的所有金属层传输到每个逻辑单元。在芯片的12个或更多金属层中的每一层,布线电阻都会降低电源电压。

供电网络的设计裕度可以承受稳压器和晶体管之间10%的压降。使用EUV进一步微缩线路和通孔会导致更高的电阻和布线拥塞。因此,如果不承受高达50%的电压降低,我们可能无法使用现有的电力传输技术微缩到3纳米以下,从而产生严重的晶体管稳定性问题。

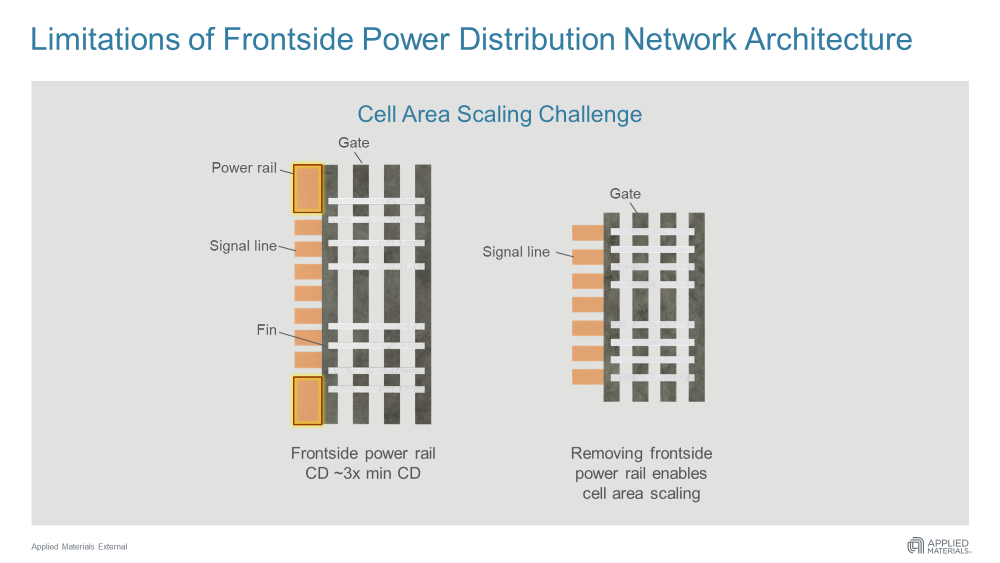

在每个逻辑单元内,电源线(也称为“轨道”)需要具有一定的尺寸,以便为晶体管提供足够的电压以进行切换。它们不能像晶体管结构和信号线等其它逻辑单元组件那样微缩。因此,电源轨现在比其它元件宽约三倍,对逻辑密度微缩构成了主要障碍。

其解决方案是一个简单而美妙的想法:为什么不将所有电源线移到背面呢?从而解决电压降低问题和逻辑单元微缩难题并显著地增加价值?

这正是应用材料公司基于晶圆正面布线领先技术上的创新。“背面配电网络”将绕过芯片的12个或更多布线层,以将电压降低多达7倍。从逻辑单元中移除电源轨可以使逻辑密度在相同的光刻间距下最多微缩30%——相当于在相同的光刻间距下两代EUV的微缩。

根据公开信息,芯片制造商正在评估三种不同的背面配电架构,每种架构都有设计权衡。一些方法将更容易制造,而其它更复杂的方法可以最大限度地扩大面积。

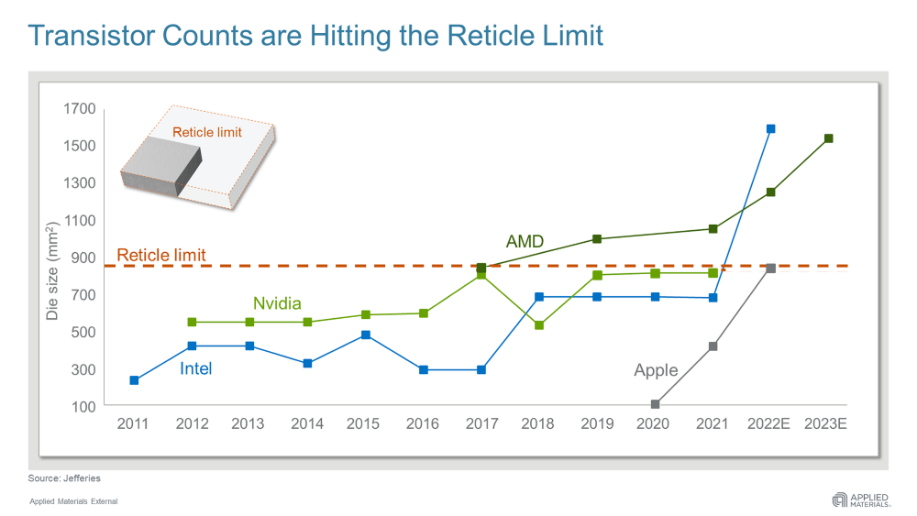

异构集成在芯片和系统级别推动PPACt

随着晶体管数量继续呈指数增长,而二维微缩速度放缓,芯片尺寸正在增加,并推高了“光罩限制”。当摩尔定律微缩平稳时,设计人员可以在该空间中放置大量高性能PC和服务器芯片,或少量极高性能服务器芯片。今天,服务器、GPU甚至PC芯片的设计者想要的晶体管数量超过了标线片区域所能容纳的数量。这迫使并加速了行业向使用先进封装技术的异构设计和集成的过渡。

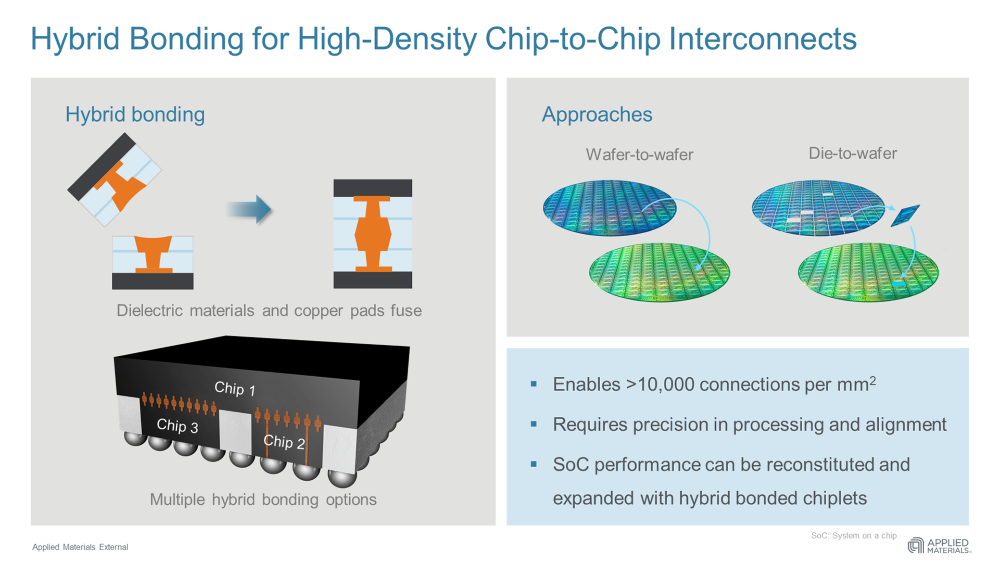

从概念上讲,如果两个芯片可以使用它们的后端互连线连接,那么异构芯片可以作为一个芯片执行,从而克服标线限制。事实上,这个概念是存在的:被称为混合键合,它正在领先的芯片制造商的路线图中出现。一个有前景的例子是将大型SRAM高速缓存芯片与CPU芯片结合,以同时克服标线限制、加快开发时间、提升性能、减小芯片尺寸、提高良率和降低成本。SRAM缓存可以使用旧的、折旧的制造节点来构建,以进一步降低成本。此外,使用先进的基板和封装技术,例如硅通孔,设计人员可以引入其它无法很好扩展的技术,例如DRAM和闪存、模拟、电源和光学芯片,更接近于逻辑和内存缓存,进而改善系统设计灵活性、成本和上市时间,并提高系统性能、功率、尺寸和成本。

为了加速行业从系统单芯片时代向系统级封装时代过渡,应用材料公司正致力于开发混合键合的解决方案。

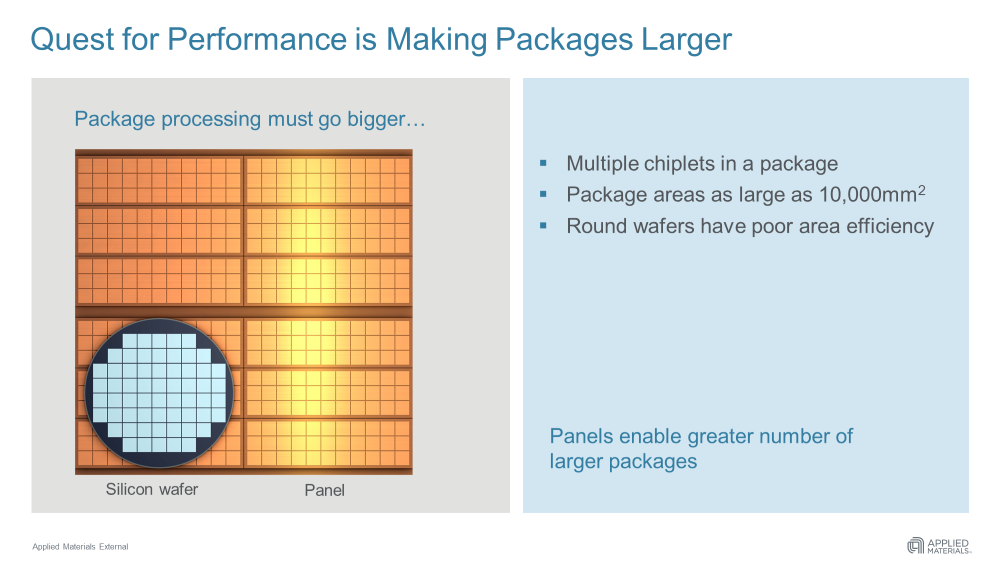

此外,我们在美国时间5月26日举办的“芯片布线和集成的新方法”大师课上,还探讨了一个相关的领域——需要更大的半导体级先进基板用于异质集成,以此使得设计人员能够利用更大的封装集成更多的芯片并且成本更具竞争力。

作者简介:

Kevin Moraes是应用材料公司半导体事业部产品和营销副总裁。他负责领导团队制定产品战略、投资重点、管理产品线等。Moraes博士拥有伦斯勒理工学院材料科学与工程博士学位、加州大学伯克利分校哈斯商学院MBA学位。

关于应用材料公司

应用材料公司(纳斯达克:AMAT)是材料工程解决方案的领导者,全球几乎每一个新生产的芯片和先进显示器的背后都有应用材料公司的身影。凭借在规模生产的条件下可以在原子级层面改变材料的技术,我们助力客户实现可能。应用材料公司坚信,我们的创新实现更美好的未来。欲知详情,请访问www.appliedmaterials.com 。

审核编辑 黄宇

-

小芯片能否“续写”摩尔定律?电子学习 2023-02-08

-

晶圆和摩尔定律有什么关系?2011-12-01 0

-

摩尔定律也适用于EPON芯片商用之路?2011-09-27 0

-

半导体行业的里程碑“摩尔定律”竟是这样来的2016-07-14 0

-

摩尔定律推动了整个半导体行业的变革2019-07-01 0

-

摩尔定律在测试领域有哪些应用?2021-04-13 0

-

请问摩尔定律死不死?2021-06-17 0

-

IC芯片的密度和计算机的速度能够一直按照摩尔定律前行吗?2021-07-22 0

-

摩尔定律,摩尔定律是什么意思2010-02-26 1592

-

摩尔定律_摩尔定律是什么2012-05-21 2789

-

所谓的后摩尔定律时代,IC业者面临什么挑战?2017-02-06 6544

-

摩尔定律变数下,中国“芯”如何迎接挑战2017-03-20 932

-

摩尔定律的现在及未来2022-03-28 2228

-

2nm芯片符合摩尔定律吗 摩尔定律能够延续下去吗2022-07-05 1587

-

摩尔定律为处理器创新让路2022-08-12 798

全部0条评论

快来发表一下你的评论吧 !