功率MOSFET管应用问题汇总

描述

功率MOSFET管应用问题汇总

问题1:在功率MOSFET管应用中,主要考虑哪些参数?在负载开关的功率MOSFET管导通时间计算,通常取多少比较好?相应的PCB设计,铜箔面积布设多大散热会比较好?漏极、源极铜箔面积大小是否需要一样?有公式可以计算吗?

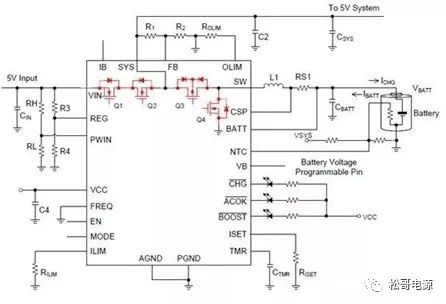

回复:功率MOSFET管主要参数包括:耐压BVDSS、RDS(on)、VGS(th)、Crss、Ciss,高压应用还要考虑Coss。半桥和全桥威廉希尔官方网站 、同步BUCK变换器下管以及隔离变换器次级同步整流MOSFET管,还要考虑内部寄生体二极管的反向恢复性能。各种参数选取要结合具体应用。

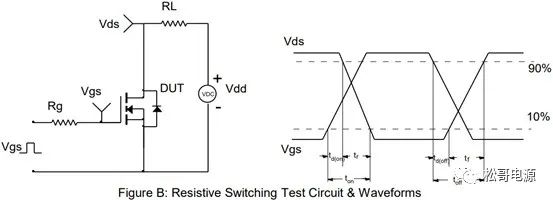

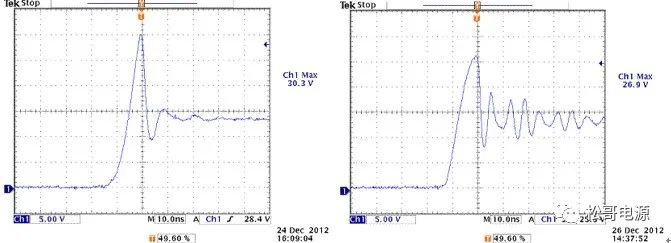

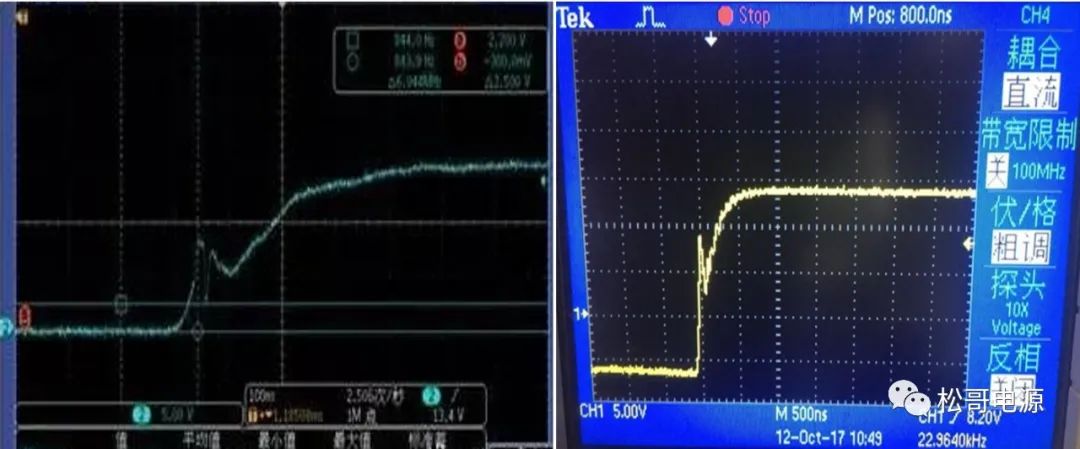

负载开关应用中,从VGS(th)到米勒平台电压VGP这一段时间控制电流变化率,米勒平台持续时间段控制电压变化率,米勒平台电压VGP由系统最大的浪涌电流决定,浪涌电流由输出电容与负载电流大小、软起动设定的导通时间决定。如果输出电压稳定后才加负载电流,那么,具体计算步骤是先设定最大容许的浪涌电流,根据最大输出电容、输出电压,就可以得到软起动时间:

为了线性控制输出电压的变化率,栅极与源极并联外部电容,如果不并联这个电容,就由Crss控制输出电压的变化率。选取相关元件参数后,对威廉希尔官方网站 进行测试,直到满足设计要求。负载开关稳态功耗并不大,但是瞬态功耗很大,特别是长时间工作在线性区,会产生热失效问题。因此,要校核功率MOSFET管的安全工作区SOA性能,同时,PCB布局,特别是贴片封装功率MOSFET管,要在源极、漏极管脚充分敷设铜皮进行散热。

功率MOSFET管数据表的热阻测量通常有一定限制条件,如元件装在1平方英2OZ铜皮威廉希尔官方网站 板上进行测量,实际应用中,源极、漏极管脚附近区域,可以布设更大面积铜皮,来保证散热性能,如果是多层PCB板,源极、漏极对应铜皮位置的每个层都敷设铜皮,用多个过孔连接。PCB铜箔面积大小与热阻关系查看公众号文章。

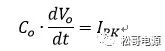

问题2:功率MOSFET管Qiss,Qg,Qrss,Qoss与Ciss,Crss,Coss是什么关系?可否用数据表的tr和tf计算开关损耗?

回复:Qiss与Ciss相关,Qrss与Crss相关,Qoss与Coss相关,Qg与Crss、Ciss以及驱动电压相关,由于Crss与Coss存在非线性特性,不能用电容值和电压变化值直接计算。测量时,在一定条件下,用恒流源对相应电容充电,使用充电电流和时间计算相应电荷值。

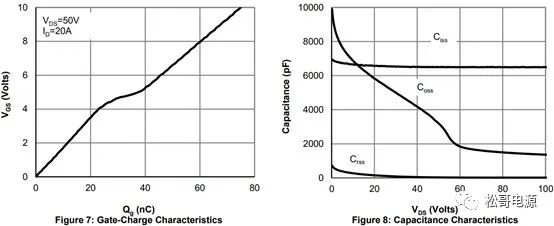

tr和tf为上升和下降的时间,数据表中,这二个参数测量条件是阻性负载,实际应用中,大多都是感性负载,VDS与ID波形的形态,和阻性负载完全不一样,因此,不能用tr和tf计算开关损耗。

问题3:AOD4126数据表中,ID、IDSM、IDM有什么区别?PD、PDM有什么区别?另外,RθJA和RθJC,要按照备注中哪一项判定?同样规格功率MOSFET管,双管和单管相比,优势在哪里?是不是简单的将RDS(on)减半、ID加倍等参数合成?

回复:功率MOSFET管数据表中,ID和IDSM都是计算值。ID是基于RθJC和RDS(on)以及最高允许结温计算得的,IDSM是基RθJA和RDS(on)以及最高允许结温计算得到。PD和PDM也是基于上述条件的计算值。计算时取TC=25℃,实际应用中TC超过100℃,而且,由于散热条件不一样;在开关过程中,还要考虑动态参数产生的开关损耗,所以,数据表中的ID不能用来进行设计。

RθJA和RθJC是二个不同热阻值,数据表中的热阻值,都是在一定条件下测量得到,实际应用的条件不同,得到的测量结果并不相同。

双管和单管功率MOSFET管,要综合考虑开关损耗和导通损耗,RDS(on)不是简单减半,因为双管并联工作,会有电流不平衡性的问题存在,特别是开关过程中,容易产生动态不平衡性。不考虑开关损耗,仅仅考虑导通损耗,也要对RDS(on)进行降额。

问题4:不同测试条件会影响功率MOSFET管VGS(th)和BVDSS吗?ATE是如何判断?

回复:不同测试条件,结果会不同,因此,在数据表中会标明详细测试条件。AET测试,VGS(th)与IGSS相关,BVDSS与IDSS相关。例如,AON6718L,当栅极与源极加上最大20V电压,VDS=0V,如果IGSS小于100nA, 由表明通过测试。不同公司可能使用不同IGSS作为标准,例如,200nA、100nA,行业内使用100nA更通用。BVDSS测试条件为IDSS=250uA,VGS=0V,如果IDSS越大,BVDSS电压值越高。

问题5:耐压100V功率MOSFET管,VGS耐压约为30V。在器件处于关断时,VGD也会到100V,是因为栅极与源极之间的栅氧化层厚度比较厚,还是说压降主要在衬底与外延层上面?

回复:栅极与源极最大电压主要由栅氧化层厚度控制,栅极与漏极最大电压主要由外延层厚度来控制,所以VGD耐压高。

问题6:单独一次雪崩,会击穿损坏功率MOSFET管吗?雪崩损坏功率MOSFET管有两种情况:一种是快速高功率脉冲,直接使寄生二极管产生较大雪崩电流,芯片快速加热过温损坏。另一种是寄生三极管导通,并发生二次击穿,什么情况下倾向于第一种发生,什么情况下倾向于第二种发生?雪崩损坏是否都发生在VDS大于额定值的情况?

回复:功率MOSFET管具有抗雪崩UIS能力,只要不超过UIS额定值,即使是高于额定的电压值,单独一次雪崩不会击穿损坏功率MOSFET管。

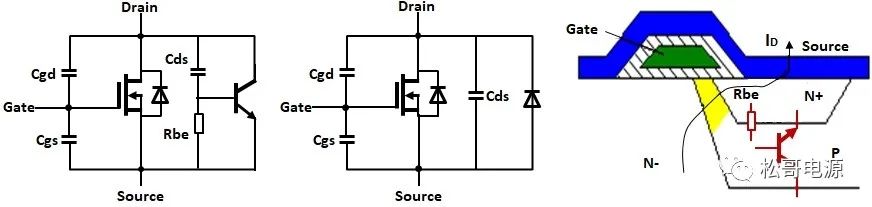

如果功率MOSFET管内部单元一致性非常好,散热非常好均匀,热平衡好,就会发生第一种情况,早期平面工艺有时候就会看到这种损坏模式。现在,新工艺导致单元密度越来越大,电流越来越集中,单元之间相互影响,导致寄生三极管导通,非常容易产生第二种情况的损坏,寄生三极管导通后,还会发生二次击穿。二次击穿并不全是因为雪崩发生,过高dV/dt、流过内部P体区电流过大,内部P体区横向电阻过大,也有可能导致寄生三极管导通。

另外,在高温条件下,在大电流关断过程中,也会发生寄生三极管导通而损坏,由于二次击穿看不到过压情况,但是,这种损坏仍然是雪崩UIS损坏。内部寄生三极管导通产生雪崩损坏,同时伴随着体内寄生三极管发生二次击穿,此时,集电极电压在瞬态时间1-2个n秒内,减少到耐压的1/2,原因在于内部电场、电流密度都很大,耗尽层载流子发生雪崩注入。电流大,电压高,电场大,电离强,大量空穴电流流过内部P体区的横向电阻,导致寄生三极管导通,集电极电压快速返回到基极开路时的击穿电压,特别是增益大时,三极管中产生雪崩击穿,此耐压值低。

三极管内部产生雪崩注入条件:电场应力,正向偏置热不稳定性。功率MOSFET管关断时,沟道漏极电流减小,感性负载使VDS升高,以维持ID电流恒定,ID电流由沟道电流和位移电流组成,位移电流是寄生体二极管耗尽层电流,和dV/dt成比例。VDS升高与基极放电、漏极耗尽层充电速度相关,漏极耗尽层充电速度与电容Coss、ID相关;ID越大,VDS升高越快,漏极电压升高,寄生体二极管雪崩产生载流子,全部ID电流雪崩流过二极管,沟道电流为0。

通常,发生UIS雪崩损坏时,电压会达到耐压值的1.2-1.3倍,可以明显看到电压有箝位(平顶波形、波形砍头),那么,对于耐压100V功率MOSFET管,工作在105V是否安全,110V是否安全?如果加上110V电压不会损坏,那么,安全原则是什么呢?

从设计角度,要求在最极端条件下,设计参数有一定余量,保持系统的安全和可靠性,通常,在动态极端条件下,瞬态电压峰值不要超过功率MOSFET管耐压的额定值,因为,长期过压工作,产生热载流子注入问题,影响器件长期工作可靠性。

问题7:沟槽Trench 功率MOSFET管的安全工作区SOA,在放大区有负温度系数效应,所以容易产生热点,这是否就是二次击穿?但是,看资料,功率MOSFET管的RDS(on)是正温度系数,不会产生二次击穿,这一点一直都不了解,能否详细说明?

回复:平面工艺和沟槽Trench工艺功率MOSFET管经过放大区时都有负温度系数特性,在完全导通的稳态条件下,RDS(on)才是正温度系数特性,可以实现稳态的电流均流。但是,在在动态开通过程中,必须跨越负温度系数区才然后进入到完全开通的正温度系数区;同样,在关断过程中,从完全开通的正温度系数区进入负温度系数区,然后关断。因为平面工艺的单元密度非常小,产生局部过流与过热的可能性小,因此,热平衡更好,相对而言,动态经过负温度系数区时,抗热冲击更好。在开关过程中,快速通过负温度系数区,可以减小热不平衡的产生。

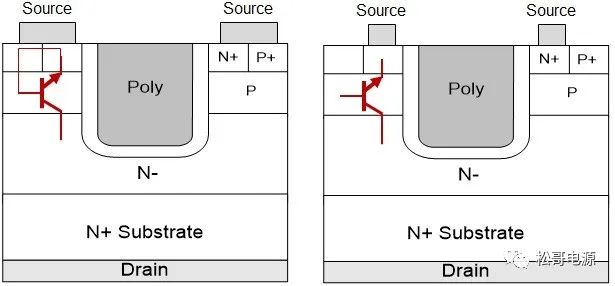

问题8:如果功率MOSFET管源极不和内部P体区层直接接触,那么就不存在寄生二极管,只有寄生三极管。由于三极管会误导通,所以将P体区层也直接连到源极,以消弱三极管效应,那么,此时就体现为明显寄生二极管,这种理解是否正确?

回复:的确如此,功率MOSFET管内部,源极和P体区都是连接在一起,主要原因在于:源极和P体区连接在一起,相当于内部寄生三极管基级与发射级短路,不连接在一起相当于基极开路,VCBO远大于VCEO,因此,可以提高器件耐压。这样连接后,内部寄生体二极管功能也连接到外部威廉希尔官方网站 。

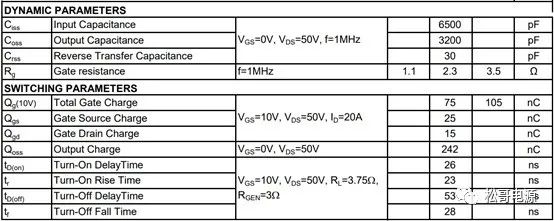

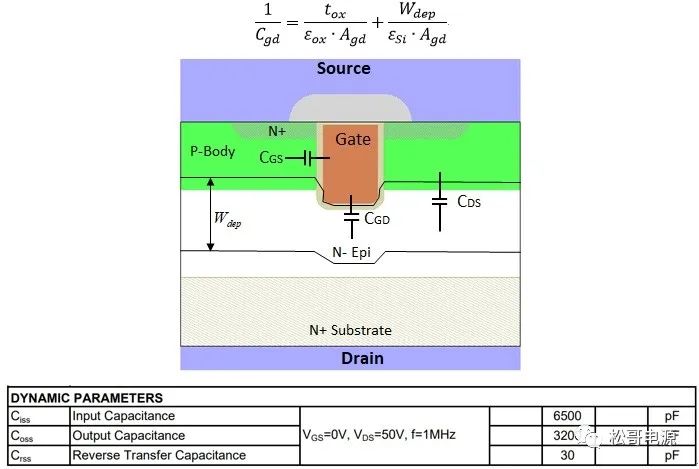

问题9:功率MOSFET管的米勒电容Crss是栅极通过氧化层对漏极的电容,开关过程中,沟道形成后,Ciss为什么会增加?耐压100V功率MOSFET管, Crss测量条件VDS=50V,这个测试条件基于什么原因?是否可以给出其它条件下的电容值?

回复:Ciss增加原因是因为Crss增加,器件导通后,耗尽层宽度Wdep减小,Crss增加。耐压100V器件,经过米勒平台区,VGD电压将从100V降到10V以内,Crss为动态电容,具有非线性特性,随着VDS降低,Crss电容不断增加。数据表中采用0.5·VDS测试条件,是行业通常采用标准,因为VDS电压减低到50V之后,VDS变化时,Crss电容变化非常小。如果有要求,可以测量0.8·VDS或VDS电压条件下Crss电容值。

问题10:功率MOSFET管的安全工作区SOA曲线如何确,可以用来作为设计安全标准吗?

回复:绝大多数功率MOSFET管的安全工作区SOA曲线都是计算值,SOA曲线主要有4部分组成:左上区域的导通电阻限制斜线、最上部水平的最大电流直线、最右边垂直的最大电压直线以及中间区域几条由功率限制的斜线。导通电阻、最大电流与最大电压值就是数据表中的额定值,功率限制的斜线基于数据表中的热阻、瞬态热阻、导通电阻以及最大允许结温的计算值,而且都是基于TC=25℃,TC代表封装裸露框架铜皮的温度,在实际应用中,TC温度远高于25℃,因此,SOA曲线不能用来作为设计验证标准。

问题11:VGS电压大于VGS(th),功率MOSFET管就导通,在刚进入米勒平台时,是否就算达到了饱和?如果是这样,此时,停止向栅极供电,忽略栅极氧化层的漏电,这时,VDS会一直维持比较高压降吗?RDS(on) 与VGS相关,VGS达到10V以后,RDS(on) 已经降到非常低的值,压降也应该降到非常低的值。如果米勒平台期间压降自动降低,那是不是说明米勒平台后期的充电没有什么用?

回复:VGS大于VGS(th)时,功率MOSFET管开始导通,也就是刚刚形成导通沟道,在米勒平台结束前,功率MOSFET管都工作在放大区,而且器件并没有完全导通,此时。功率MOSFET管承受电源电压,导通电阻非常大,理论上,电流乘以电阻等于VDS值。到了米勒平台区,电流达到系统的最大电流后,电流就不能再增加,栅极提高的多余电子进入到外延层的耗尽层,导致耗尽层宽度降低,对应的VDS电压开始下降,即使VDS电压下降非常小,对应的电压变化率非常大,因此,驱动回路的电流将全部被米勒电容Crss所抽取,此时,就看到米勒平台,栅极电压基本保持不变,VDS电压不断降低,直到下降到最小值,此后,VDS电压变化率为0,米勒平台区结束。

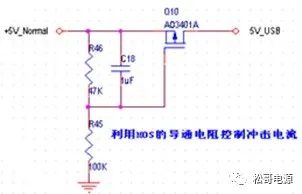

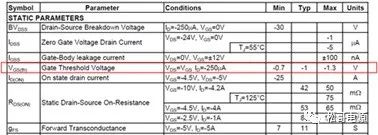

问题12:使用AO3401A做负载开关,缓冲热插入移动硬盘的瞬间冲击电流,防止瞬间把主机芯电压拉低,将VGS电压设定在-1.6V左右,RDS(on)大约在100mΩ左右,插上移动硬盘瞬间的冲击电流由原来的9A下降到5A左右,冲击电流持续时间为80微秒左右,效果很明显。移动硬盘正常工作时电流约300mA,如果将VGS设定在-2.5V左右,RDS(on)只有几十mΩ,对冲击电流的抑制作用不大,这个威廉希尔官方网站 设计原则是什么?

AO3401A数据表中,VGS(th)电压为-1.3V,设定VGS=-1.6V,电压绝对值大于-1.3V,它是否正常导通?应用中,不考虑损耗,0.03V 的VGS差异,RDS(on)的压降对系统没有任何影响。原来使用0.1欧姆的氧化膜电阻限制浪涌电流,但是,该电阻体积太大,用这个威廉希尔官方网站 目的就是想替换这个电阻。但是,电视机开机后,这个威廉希尔官方网站 的功率MOSFET管一直导通,而不是在插入移动硬盘后再打开功率MOSFET管,所以,调节功率MOSFET管的外围驱动威廉希尔官方网站 元件参数,不能起到降低冲击电流的作用。利用功率MOSFET管的恒流区特性来降低冲击电流,如果把VGS调整到-2.5V以上,对冲击电流的限制作用就非常小,只能从9A降到8A左右,这样的做法,对功率MOSFET管会有问题吗?

AO3401A数据表中,第1页标明栅极工作电压低于2.5V,是否要求栅极电压必须大于2.5V, VGS必须小于-2.5V?设计时,VGS=-1.6V有问题吗,如果继续加大VGS到-1V,有问题吗?是不是VGS大小没有关系,只要保证RDS(on)产生功耗不要导致过热就行,是否正确?

回复:VGS=-1.6V时,可以保证功率MOSFET管导通,要考虑电阻阻值的分散性,威廉希尔官方网站 中源极与栅极电阻为47K,栅极到地电阻为100K,在最极差条件下,如果使用电阻的精度为10%,VGS电压绝对值为:1.3+1.6·20%=1.64V,功率MOSFET管仍然可以工作。如果电阻的精度为15%,考虑到VGS(th)电压的分散性,在一定条件下,例如,在低温时,功率MOSFET管有可能不工作。VGS(th)电压是负温度系数,温度越低,其值越大。驱动电压的稳定值,要结合输入电压最低值、分压电阻值的精度、VGS(th)和VGS(th)的温度系数等条件综合考虑,来选择合适的电阻分压比,从而保证系统的设计要求。

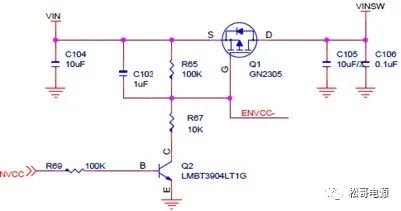

负载开关威廉希尔官方网站 利用功率MOSFET管在开通过程中较长时间工作在线性区(放大区、恒流区)控制上电瞬态输出容性大负载产生的浪涌电流,例如热插拨移动硬盘,因为硬盘带有较大的容性负载,切入瞬间形成非常大的浪涌电流.如果功率MOSFET管已经导通,后面再插入移动硬盘这样的大容性负载,就无法限制浪涌电流。在功率MOSFET管栅极下拉电阻下面串联一个NPN三级管,当热插拨移动硬盘时,给出信号控制三极管基极导通,然后,功率MOSFET才开始工作,从而有效控制浪涌电流。

功率MOSFET工作在线性区时,电阻远大于完全导通的电阻,也可以理解为用电阻限制浪涌电流。设计负载开关威廉希尔官方网站 时,分压电阻既要保证正常工作时,功率MOSFET管完全导通,又要保证VGS最大电压不要超过额定的最大值。串联在栅极的电阻可以调节功率MOSFET管开通速度,在满足要求的开通速度后,VGS电压不能超过最大额定电压值,然后,可以适当提高VGS电压值,这样,在正常工作状态下,功率MOSFET管完全导通后,RDS(on)降低,减小产生的静态损耗。

AO3401A工作在VGS=-2.5V时,导通电阻约为120mΩ。如果VGS电压太小,低于阈值电压VGS(th),AO3401A可能无法完全开通,无法正常工作。建议将VGS的绝对值设定2.5V以上,如-3.5V左右,通过调节分压电阻的阻值、栅极与源极并联的电容来降低冲击电流。

问题13:功率MOSFET管关断时VDS电压发生振荡,在同一个威廉希尔官方网站 上测试两个不同厂商的功率MOSFET管,得到关断波形并不相同。器件1的尖峰较高,振荡抑制的很快;器件2的尖峰较低,振荡抑制的较慢。在同一块PCB上测量,威廉希尔官方网站 的寄生电感、寄生电容等参数不变,只有功率MOSFET管不同。这种尖峰是威廉希尔官方网站 上的寄生电感和功率MOSFET管的寄生电容谐振引起,这两个器件的哪些参数会产生这种差别,导致振荡波形不同?是否能够从器件数据表的某些参数对比来选择一款实际应用中,峰值较低、振荡又能快速消除的功率MOSFET管?

回复:功率MOSFET管关断中,VDS电压波形经常会发生振荡。测量VDS波形,首先要保证正确的测量方法,如去掉探头帽、使用最短的地回路,示波器以及探头带宽等满足测量要求;通常,VDS振荡波形由PCB寄生回路电感和功率MOSFET管的寄生电容形成高频谐振而产生,在寄生电感值一定条件下,寄生电容越小,振荡频率越高,幅值也越高,振荡初始幅值与回路的初始电流值也相关;同时,回路的总电阻越大,波形衰减越快。另外,功率MOSFET管的寄生电容Coss具有非线性的特性,随着电压增大而减小,因此,波形振荡的频率并不固定。降低功率MOSFET管的关断速度、可以降低振荡的幅值,在源极与漏极并联电容,可以降低振荡的频率和幅值,抑制电压尖峰。

问题14:功率MOSFET管的耐压为什么是正温度系数?温度越高,耐压越高,那是不是表明功率MOSFET管对电压尖峰有更大裕量,越安全?

回复:随着温度升高,晶格热振动加剧,致使载流子运动的平均自由路程缩短,在与原子碰撞前由外加电场加速获得的能量减小,发生碰撞电离的可能性也相应减小。在这种情况下,只有提高反向电压进一步增强电场,才能发生雪崩击穿,因此雪崩击穿电压随温度升高而提高,具有正的温度系数。功率MOSFET管耐压测量基于一定漏极电流,温度升高时,为了达到同样的测量漏极电流,只有提高电压,因此,测量得到的耐压提高。功率MOSFET管损坏的最终原因是温度,更多时候是局部过温,导致局部形成热点,发生过热损坏,在整体温度提高条件下,功率MOSFET管更容易发生内部局部单元的热和电流不平衡,从而导致损坏。

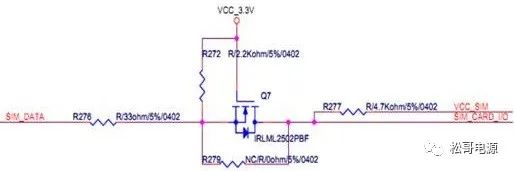

问题15:使用功率MOSFET管进行不同电平信号间的转换,3.3V加到栅极,源极通过33Ω电阻连接到SIM_DATA信号,栅极与源极之间并联2.2KΩ电阻。漏极的连接有二个支路,一个直接连接到SIM_CARD_I/O,另一个通过4.7KΩ电阻连接到VCC_SIM=5V,其中,SIM_CARD_I/O属于I/O双向传输,SIM_DATA为输入信号。SIM_DATA为高时功率MOSFET管截止,SIM_CARD_I/O接收为5V信号;SIM_DATA为低时,功率MOSFET管导通,SIM_CARD_I/O接收为低电平信号。当SIM_DATA为输出信号时,如何理解SIM_CARD_I/O输入为低电平信号?

回复:功率MOSFET管的电流可以从漏极到源极,也可从源极到漏极。电流从源极到漏极时,寄生体二极管导通,因此,这个方向电流不可控。SIM_DATA为输出信号时,SIM_CARD_I/O为低电平,功率MOSFET管寄生体二极管导通,信号SIM_DATA也拉低,接收低电平信号。SIM_CARD_I/O输出高电平5V时,功率MOSFET管寄生体二极管截止,信号SIM_DATA上拉到3.3V,接收高电平信号。

问题16:超结高压功率MOSFET管的UIS雪崩能力为什么比平面工艺低?

回复:超结高压功率MOSFET管的P柱几乎贯穿整个芯片厚度,生产工艺复杂,内部晶胞单元密度大,多层外延结构P柱两侧电荷平衡不均匀,或者直接填充结构内部布局有空隙,影响中间耗尽层与横向电场分布的对称性,产生局部电场集中从而导致局部电场强度过大,影响UIS雪崩能力。

问题17:实际应用中,功率MOSFET管损坏模式有那些?如何判断MOSFET的损坏方式?

回复:除去生产过程中产生缺陷或损坏,实际应用中,功率MOSFET管损坏模式包括ESD损坏、过流损坏、过压损坏、过流后过压损坏、UIS雪崩损坏、寄生体二极管反向恢复损坏等,要结合具体应用威廉希尔官方网站 和失效形态来分析。参考公众号文章。

问题18:功率MOSFET管的数据表中dV/dt为什么有二种不同额定值?如何理解寄生体二极管反向恢复特的dV/dt?

回复:反激开关电源中,初级主开关管关断过程中,VDS电压波形从0开始增大,产生一定斜率dV/dt,同时产生电压尖峰,就是寄生回路的电感和功率MOSFET管的寄生电容振荡形成,这个dV/dt会通常通过米勒电容耦合到栅极,在栅极产生电压。如果栅极电压大于开通阈值电压,功率MOSFET管就会误导通,产生损坏,因此,要限制功率MOSFET管关断过程中的dV/dt。另一种情况就是在LLC、半桥和全桥威廉希尔官方网站 以及同步BUCK变换器下管,当下管关断后,下管寄生体二极管先导通续流,然后对应的上桥臂的上管开通,寄生体二极管在反向恢复过程中,产生dV/dt问题。寄生体二极管反向恢复的dV/dt额定值,远小于功率MOSFET管本身dV/dt额定值。

寄生体二极管在反向恢复过程中,如果存储电荷没有完全清除,就不能承受电压,相当于处于开通状态。那么,在这个过程中,电源电压就只能加在回路的杂散电感,输入电流增加,回路的杂散电感限制电流增加,这个过程持续时间越长,反向恢复电流越大,如果寄生体二极管反向恢复特性差,功率MOSFET管就可能在寄生体二极管反向恢复过程中发生损坏。有时候,反向恢复电流过大,也可能直接损坏上管。

问题19:做LED背光驱动的BOOST变换器,发现其中一颗功率MOSFET管失效,栅极、漏极与源极都短路,继续工作一些时间后,漏极与源极又变成开路,为什么?

回复:开始的失效发生在硅片内部,栅极、漏极与源极都短路。继续工作一些时间后,由于大电流冲击,导致源极与硅片的键合线熔化烧断开,因此,漏极与源极开路。

问题20:测量VGS波形,发现在米勒平台处存在振荡下降,这个电压降低到阈值开启电压以下,是否存在风险?

回复:VGS降低到阈值开启电压以下,会导致开关损耗增加,要校核功率MOSFET管的温升是否满足要求。如果是多管并联工作,在开关过程中不能很好均流,特别是一个功率MOSFET管关断,所有电流完全从另一个功率MOSFET管流过,损坏风险很大。

问题21:在多个功率MOSFET管并联扩流应用中,当使用具有过流保护功能的电源调试时,威廉希尔官方网站 如果出现损坏,通常只会烧毁一个功率MOSFET管,如何判断是那个功率MOSFET管损坏?

回复:万用表打在电阻挡,检测每个功率MOSFET管栅极与漏极电压,红笔接漏极,测得电阻值最小,就是功率MOSFET管的功率MOSFET管。

问题22:隔离电源模块,功率为480W,初级全桥威廉希尔官方网站 ,模块输入电压51-56V DC,额定输出10.8V,48A。其中一个桥臂两颗功率MOSFET管都损坏。在应用时,因为外围威廉希尔官方网站 异常造成二次侧电流反灌到初级,初级功率MOSFET管电流从源极流向漏极,结合失效分析报告FA,源极表面出现烧毁痕迹,原因分析是电流EOS,电流从源极流向漏极,能否是导致其烧毁的原因?

回复:同步整流产生输出反灌电流是最恶劣的一种工作条件,在设计过程中要尽可能减小输出反灌电流。输出反灌导致输出整流管雪崩,损坏输出同步整流管,取决于输出同步整流管的雪崩能力以及反灌电流形成的负向电流大小。输出反灌电流还会影响初级功率MOSFET管工作。当输出形成反向电流时,若Q1/Q2是一个半桥臂,Q1为上管,Q2为下管;Q3/Q4是另外一个半桥臂,Q3为上管,Q4为下管;输出反灌通常发生在轻载条件,全桥威廉希尔官方网站 工作在硬开关,由于输出是反向电流,因此,当Q1/4导通前,电流从Q1/4二极管中流过,而且Q1/4导通后,从Q1/4沟道流过;输出电压越高,次级输出电感的能量越大,其初级电流不足以反向,Q1/4关断后,电流还是从Q1/4二极管中流过,经过死区时间后,Q2/Q3导通,此时,由于Q1/4二极管中流过电流时间长,电流也比较大,而且死区时间短,如果功率MOSFET管寄生体二极管反向恢复特性差,导致Q2/3导通,功率MOSFET管发生损坏。

损坏的功率MOSFET管在上桥臂还是下桥臂、在初级还是次级,取决于功率MOSFET管抗短路大电流冲击的能力。副次级通常是大电流关断后的电压雪崩,初级通常是寄生体二极管反向恢复上下桥直通形成大电流损坏。寄生体二极管是负温度系数,其产生的损坏形态和开通时线性区损坏形态比较接近。从设计角度,必须减小输出反灌电流;从器件角度,提高初级功率MOSFET管寄生体二极管的反向恢复特性,可以提高初级器件的安全性。

问题23:功率MOSFET管测量电压时,电流为250uA,而IDSS电流只有几个uA,为什么?

回复:IDSS电流小,表明实际的漏电流小于测试规范的要求,因此产品合格。

问题24:功率MOSFET管损坏后,阻抗变为一个中间值,有时工作有时不工作,为什么?

回复:通常功率MOSFET管损坏后,如果电源没有电流保护,经过更大电流二次冲击,导致内部的金属线熔化与汽化。系统不工作,功率MOSFET管冷却下来,熔化汽化的金属凝固,局部区域连通,形成较大阻抗。功率MOSFET管通电工作后,这些局部连通区域又断开,功率MOSFET管停止工作。有时也会出现这样现象:冷却凝固后内部金属断开,通电后金属熔化又导致内部区域连通。

问题25:测试功率MOSFET管寄生体二极管的反向恢复特性时,IF越低,Qrr越大,电压尖峰越高,为什么?

回复:这种情况主要发生在高压功率MOSFET管,当寄生体二极管导通时,电荷在PN结积累,当寄生体二极管开始承受阻断电压时,这些电荷将被清除。如果IF低, PN结积累的电荷水平低,清除的速度非常快,dV/dt越大,C·dv/dt的偏移电流就大。数据表中测量得到的Qrr包括二部分:一是与寄生体二极管真正Qrr以及C·dv/dt直接相关少子,二是和Coss相关的电荷。

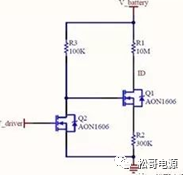

问题26:使用一个外部信号控制PMIC的管脚ID,PMIC由电池供电,ID管脚内部由10M的电阻上拉后接到电池。当外部信号为0时,300K外部电阻要接到ID管脚;当外部信号为1时,300K外部电阻和ID管脚断开,如何实现?

回复:使用二个N沟道功率MOSFET管Q1与Q2,Q1漏极直接连接到ID,栅极通过100K电阻连接到电池电压,源极通过300K电阻连接到地。Q2漏极直接连接到Q1栅极,源极连接到地,Q2栅极通过外部信号V_driver控制。V_driver为0时,Q2关断,Q1导通,ID由300K电阻下拉到地。V_driver为1时,Q2导通,Q1关断,ID由内部10M电阻上拉到电池电压。此时,100K电阻产生静态损耗,阻值越大,功耗越小。Q1导通时,电池电压为3.8V,Q1源极电压为:3.8V·300K/(10M+300K) =0.11V。

问题27:PD充电器输出,VBUS电压开关为什么用P管,而不是N管?

回复:P管可以直接驱动,N管需要浮动驱动,因为N管导通后,源极电压为VBUS,栅极电压必须高于VBUS一定电压值,才能保持导通状态。

问题28:功率MOSFET管电容的温度系数是正温度系数还是负温度系数?

回复:功率MOSFET管的电容在正常温度范围内(小于500K),不随温度的变化而变化。Coss由功率MOSFET管的Cgd和PN结电容二者组成,如果温度太高,接近硅的本征温度,本征半导体载流子的浓度增加非常多,PN结的电容将增加。温度从300K增加到600K的仿真结果如下。

问题29:在平面水平导电结构的功率MOSFET管中,内部具有二颗背靠背的二极管,这种结构有什么优点和缺点?是不是这种结构不存在寄生体二极管?

回复:这种结构因为工艺原因主要用于单芯片电源芯片,垂直结构功率MOSFET管的源极和P体区相连接,因此,寄生体二极管引出。如果源极和P体区不连接,寄生体二极管就不能引出。

问题30:功率MOSFET管标称的VGS(th)最小值为0.4V,是指所有情况吗,还是温度升高还有可能更加低?

回复:测量条件是25℃,250uA电流,温度越高,VGS(th)值会越低。

问题31:VDS超过最大额定电压,但通过电流很小,会使损坏器件吗?

回复:要计算功率损耗,同时,校核安全工作区。

问题32:封装对结电容、开关时间影响有多大?

回复:封装主要影响是键合线产生的寄生电感和电阻,对电容影响非常小。

问题33:如果驱动电阻调大,开关速度变慢,Eoss会有变化吗?

回复:Eoss对应着Coss储存能量,在硬开关开通过程中放电消耗掉,和驱动电阻没有关系,驱动电阻影响开关损耗。

问题34:超结结构高压功率MOSFET管和平面结构对比,Coss会高很多吗?与沟槽Trench 相比,SGT结构降低Crss,但是会增加Cds,Coss是变好还是变差?

回复:超结结构功率MOSFET管,Coss在高压时比平面结构小很多,在低压时比平面结构大很多。SGT结构额外产生Cds,Coss值会变大一些。

问题35:电源电压为VDD,计算开通损耗和关断损耗时,Ciss和Crss都是使用数据表查找VDS=VDD对应电容值吗,还是使用电压平均值或者有效值查找相应电容值?

回复:Ciss随电压变化影响不大,Crss随电压变化影响非常大,计算时,不要使用Crss,而是使用Qrss来计算。

问题36:降低米勒平台电压会有什么影响?超结结构功率MOSFET管应用中,是不是不能刻意提高快速开关?

回复:降低米勒平台电压,开通速度加快,关断速度降低,开通损耗减小,关断损耗增加。超结结构功率MOSFET管开关速度本来就非常快,栅极非常容易振荡,为了减小栅极振荡,通常会在栅极与源极并联电容、加大栅极外部串联电阻,来降低开关速度,同时控制dV/dt。在一些极端情况下,甚至在栅极与漏极之间并联电容。

问题37:用小电感大电流串联UIS雪崩能量,线路杂散电感与等效直流电阻会引起测量偏差吗?FT使用小电感提高测试效率,小电感测量得到Eas比大电感时低,原因是什么?如果UIS雪崩标称值为能量,是不是根据能量大小就可以评估雪崩耐量,而不需要去考虑使用的电感值?

回复:如果线路杂散电感与测量所用电感相比非常小,影响可以忽略,否则,就要考虑杂散电感的影响。小电感测量时,电流上升速度非常快、电流大,发生雪崩前,器件热量由于热容影响不容易耗散,器件局部瞬态温度非常高,因此,雪崩能量降低。电感值越大,电流上升时间越长,电流增加速度越慢,发生雪崩前,器件热量相对耗散更多,因此,雪崩能量增大。电感值越大,测试时间就越长,生产效率越低。评估雪崩耐量,仍然要考虑电感值的影响。

问题38:功率MOSFET管的输出电容Coss越大,Eas性能会越好,实际应用需要低的Coss,这两者是不可调和的矛盾吗?

回复:输出电容Coss只是表象,不是真正原因。同样技术平台,Coss越大,表明硅片尺寸越大,相应的雪崩能量更大。功率MOSFET管内部结构,比如加场板、场环,工艺特点,晶胞单元一致性等许多其它因素,都会影响雪崩能量。

问题39:功率MOSFET管在生产线测试雪崩过程中,会不会造成伤害?

回复:由于雪崩能量测量值有较大降额,正常规范下测量不会有伤害。

问题40:功率MOSFET管线性区工作,空穴电流由外延层epi中耗尽层产生,那么,空穴电流是不是和截止状态时产生漏电流一样?如果是一样,截止状态下寄生三极管不会导通,那么,线性区工作状态下,寄生三极管应该也不会导通。

回复:工作条件不同,在截止状态下,如果将电压提高到雪崩电压,就会出现寄生三极管导通的情况。线性区工作时,虽然没有到雪崩电压,但是,内部温度高,特别是局部不平衡温度变大,在一定电场强度作用下,加剧碰撞电离,产生较大空穴电流,容易导致寄生三极管导通。

问题41:功率MOSFET管在开通过程中,会在米勒平台电压附近振荡,如何计算有足够能量打开功率MOSFET管,避免振荡发生?振荡原因是不是VGS在米勒平台电压时持续时间不够,VDS电压没有完全降下去,ID电流没有完全流过漏极,VGS已经停止给电容CGD充电,多余ID反而给CGD充电,重新拉回VGS,这个过程反复循环造成振荡?实际应用中,推荐在栅极与源极之间加1uF左右电容,栅极与漏极之间加电容,这样增加漏极流过电流的时间,ID完全从漏极流过,没有多余电流对CGD反向充电,应该更容易避免振荡。在栅极与源极之间加电容又是什么原因?和栅极与漏极之间加电容的效果一样吗,原理是什么?如何在威廉希尔官方网站 设计中避免类似的振荡发生,可以计算吗?如果可以计算,是否可以利用VGS上升斜率大于VDS下降斜率来避免振荡发生?

回复:VDS下降比较快,从CGD抽走电流超过IG能提供的电流,导致VGS电压下降。由于VGS电压正好处于功率MOSFET管阈值电压之上,VGS轻微下降会导致ID迅速变小,因此,VDS下降速率会变慢,这样反过来减少从CGD抽走的电流,于是,VGS又开始上升,驱动回路的寄生电感也参入振荡的过程。栅极与源极之间加电容,振荡频率、幅值降低,功率MOSFET管的开通速度变慢,dV/dt也变慢,可以抑制振荡,缺点是开通时间变长,损耗增大。栅极与漏极之间加电容,可以减小CGD随电压改变非线性突变产生的振荡。选用开关速度较慢的功率MOSFET管,增大栅极外部驱动电阻,栅极与源极之间加电容,栅极与漏极之间加电容,漏极与源极之间加电容,都可以用来抑制振荡。

问题42:在系统调试中发现,功率MOSFET管驱动电压过高,导致输出过载时,功率MOSFET管的电流过大。于是,降低驱动电压到6.5V,电流就会降低,这样做可行吗?

回复:系统短路时,功率MOSFET管相当于工作在放大的线性区,降低驱动电压,可以降低跨导限制的最大电流,从而降低系统的短路电流,提高短路保护性能。降低驱动电压,正常工作时,RDS(on)会增大,损耗增加,功率MOSFET管温度会升高,系统效率会降低。CPU控制系统,可以通过电流检测威廉希尔官方网站 ,当电流大于某个设定值时,动态减小驱动电压,从而减小短路电流的冲击。当系统输出负载恢复到正常水平后,驱动电压回到正常电压值,提高系统正常工作的效率。另外,短路保护也可以通过威廉希尔官方网站 设计来优化,从而减小短路保护延时时间,提高响应时间。

问题43:对于功率MOSFET管的可变电阻区、放大区(饱和区)的划分有些不太理解,可变电阻区的电流ID与VDS成恒定线性关系,RDS(on)应该是恒定且极小。在恒流区工作,ID被VGS限制,此时,VDS急剧升高,RDS(on)急速升高,从跨导的定义,由于ID不再增加,因此,定义为饱和区,但是,为什么又称为放大区?

回复:在可变电阻区,功率MOSFET管已经完全导通,此时,功率MOSFET管的导通压降VDS等于流过的电流ID与导通电阻的乘积,这个区定义为可变电阻区的原因在于:功率MOSFET管数据表中,测量得到导通电阻都有一定条件,当VGS不同时,沟道的饱和程度不同,因此,不同VGS对应的导通电阻并不相同。在漏极导通特性曲线中,这个区域的不同VGS对应曲线密集排在一起,当VGS变化时,电流保持不变,对应VDS电压(电流和导通电阻的乘积)也跟随着变化,也就是导通电阻在变化,可变电阻区由此而得名。在可变电阻区,VGS变化时,导通压降变化不大,说明内部沟道的饱和程度变化较小。如果VGS相差比较大,导通电阻还是有明显变化。恒流区称为饱和区、线性区,当VGS电压一定时,沟道对应着一定饱和程度,也对应着跨导限制的最大电流。恒流区也被称为放大区,因为功率MOSFET管也可以作为信号放大元件,和三极管具有相类似的放大特性,功率MOSFET管的恒流区就相当于三极管的放大区。恒流区有时候还可以称为线性区,这些名称只是定义的角度不同,叫法不同。

问题44:什么是功率MOSFET管的放大区?

回复:功率MOSFET管具有和三极管类似的放大特性,例如,三极管工作在放大区,IB=1mA,电流放大倍数为100,IC=100mA。功率MOSFET管,VGS(th)=3V,VGS=4V,跨导为20,ID=20A。开关电源中,功率MOSFET管工作在开关状态,相当于在截止区和可变电阻区(完全导通区)快速切换。在这个切换过程中,必须跨越放大区,这样,电流、电压就有交叠,于是就产生了开关损耗。因此,功率MOSFET管在开关过程中,跨越放大区是产生开关损耗最根本原因。

问题45:功率MOSFET管的寄生体二极管导通,VGS=2.5V,ID=100mA,功率MOSFET管的导通压降只有0.06V,功率MOSFET管在反向工作时, VGS(th)是不是比正向导通时要低?是不是二极管的分流作用,导致反向工作时的压降降低?

回复:VGS(th)是功率MOSFET管固有特性,表示功率MOSFET管在开通过程中沟道形成的临界电压。功率MOSFET管内部寄生体二极管导通,PN结的耗尽层宽度减小直到消失,N区电子会注到P区,P区空穴会注入到N区,形成非平衡少子,增加沟道中少子穴浓度,促进沟道中反型层的形成,因此,同样VGS电压,形成更宽沟道,降低沟道的导通电阻,从而降低导通压降。随着VGS电压的提高,沟道狭窄区的载流子浓度接近饱和,沟道的导通电阻及导通压降就不再有明显的变化。

问题46:功率MOSFET管做同步整流管,关断后,漏极电流是立刻切换到寄生体二极管,还是缓慢下降,然后逐渐切换到寄生体二极管?如果是后者,这个时间有没有相关参数?

回复:漏极电流会逐渐从沟道切换到寄生体二极管,一般不考虑这个时间。沟道彻底夹断前,VGS电压降低,沟道电阻逐渐变大,只要阻抗低于二极管正向压降,电流仍然从沟道流过,沟道和二极管同时流过电流。

审核编辑:汤梓红

-

[原创]功率MOSFET管2010-08-12 0

-

功率场效应管(MOSFET)的结构,工作原理及应用2011-12-19 0

-

理解功率MOSFET管的电流2016-08-15 0

-

功率MOSFET选型第一步:P管,还是N管?2016-12-07 0

-

SiC-MOSFET功率晶体管的结构与特征比较2018-11-30 0

-

功率场效应管MOSFET的特点2019-04-10 0

-

功率MOSFET的基本知识分享2021-04-23 0

-

基于功率MOSFET管的RCC威廉希尔官方网站2010-05-13 935

-

功率场效应晶体管(MOSFET)原理2009-04-25 10038

-

功率场效应管MOSFET,功率场控晶体管2009-05-12 1552

-

功率MOSFET管2009-11-07 1959

-

mosfet的应用_mosfet品牌-精华汇总2012-08-10 2058

-

开关电源中功率MOSFET管损坏模式及分析2013-09-26 1146

-

功率MOSFET管Rds负温度系数对负载开关设计有什么影响2023-02-16 1452

全部0条评论

快来发表一下你的评论吧 !