Altium Designer 24.0.1版本新功能说明

描述

Altium Designer 24.0.1

发布时间:2023年12月14日

Altium Designer 24.0.1 离线包

15天免费试用 Altium Designer

PCB设计改进

任意角度差分对布线器(Open Beta版)

本次发布引入了对任意角度差分对布线的支持。当使用Interactive Differential Pair Routing工具(Route » Interactive Differential Pair Routing)对差分对进行布线时,现在可以在Properties面板中以Differential Pair Routing模式对布线属性进行配置,选定Any Angle转角样式()。

任意角度差分对布线支持对称焊盘入口和间距变化。

当从天线开始进行差分对布线时,该工具将保持从左到右的网络顺序(即,左侧的延续性将仍位于左侧)并支持捕捉至原始方向。

使用Any Angle转角样式进行差分对布线时,按住Shift键即可使用切线圆弧进行差分对布线。

任意角度差分对布线演示。

请注意,当使用Route » Gloss Selected命令时,此功能还会启用更新后的角度差分对修线算法。

任意角度差分对布线的目前主要限制为:

目前不支持通过具有不同设计规则的Room边界进行布线转换。

目前不支持SMD Entry设计规则。

目前不支持环路自动删除。

此功能目前处于Open Beta阶段,且仅当在Advanced Settings对话框中启用PCB.Routing.AnyAngleDiffPairRouter选项时可用。

如需了解更多信息,请参阅Differential Pair Routing页面。

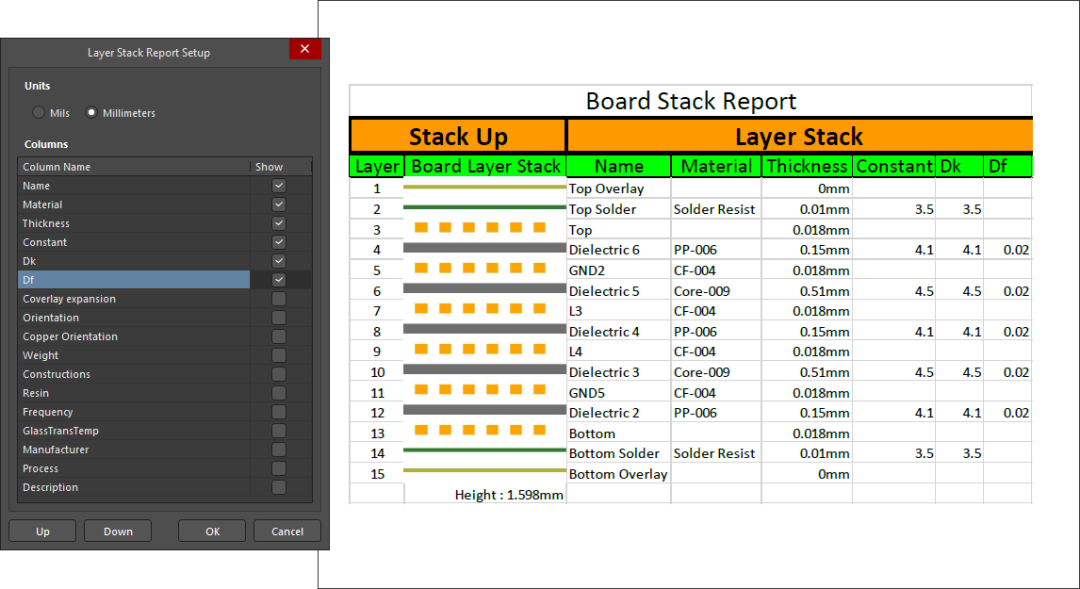

增强版Layer Stack Report Setup对话框(Open Beta版)

Layer Stack Report Setup对话框(File » Fabrication Outputs » Report Board Stack)功能已得到增强,现在包括Layer Stack中存在的所有列。可以使用该对话框选定想要在Layer Stack Report中显示的列。

此功能目前处于Open Beta阶段,且仅当在Advanced Settings对话框中启用PCB.ModernBoardStackGenerator选项时可用。

如需了解更多信息,请参阅Preparing Fabrication Data页面。

PCB CoDesign改进

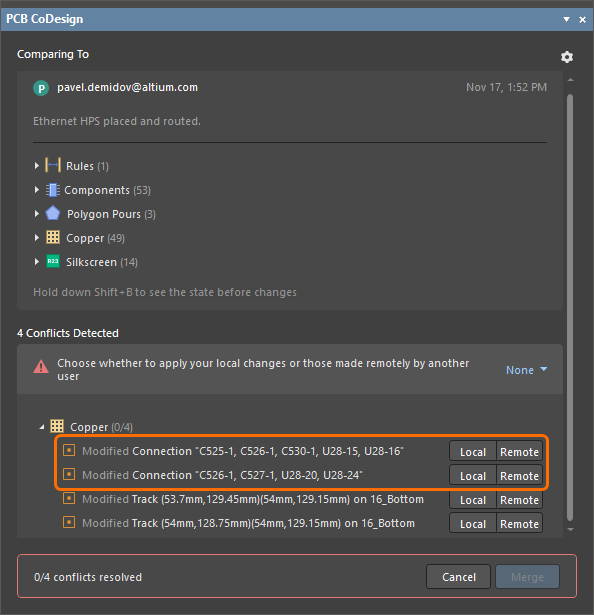

增强版铜皮冲突显示和解决

现在可根据具体情况,将铜皮对象冲突分为引脚间连接组,以便于探索和解决更改。

现在可以在引脚间连接级别上,对铜皮冲突进行解决。

现在可以在引脚间连接级别上,对铜皮冲突进行解决。

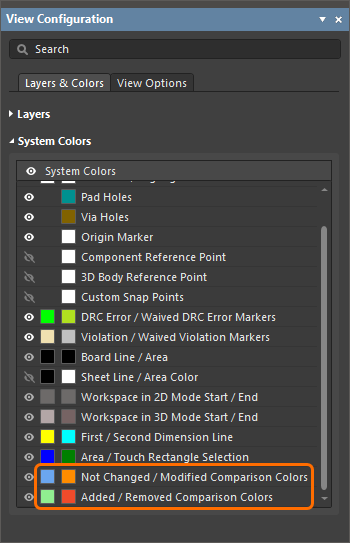

添加了颜色图例配置功能

您现在可以在View Configuration 面板中,为已添加、修改、删除和未更改的对象(在PCB CoDesign面板中选定引脚间连接时未更改的对象)选定颜色。

使用View Configuration面板,对比较颜色图例进行配置。

其他PCB CoDesign UI更改

显示正在进行比较的弹出窗口,现在将在运行比较后立即弹出。

添加了在更改列表中选定和取消选定入口的功能。当某个入口(通过单击该入口)已被选定时,再次单击即可取消选定该入口并将设计区内的对象高亮显示重置。

在使用PCB CoDesign面板将更改合并后显示的Project面板Merged图标(  )菜单中,添加了Save to Server命令 – 显示图像。

)菜单中,添加了Save to Server命令 – 显示图像。

合并更改后,单击PCB CoDesigner面板上的Save to Server按钮时,将在Save to Server对话框中默认仅选定合并后的PCB文档 - 显示图像。

运行合并更改时,现在将会出现一个新弹出窗口,提示正在进行合并 - 显示图像。

如需了解更多信息,请参阅PCB CoDesign 页面。

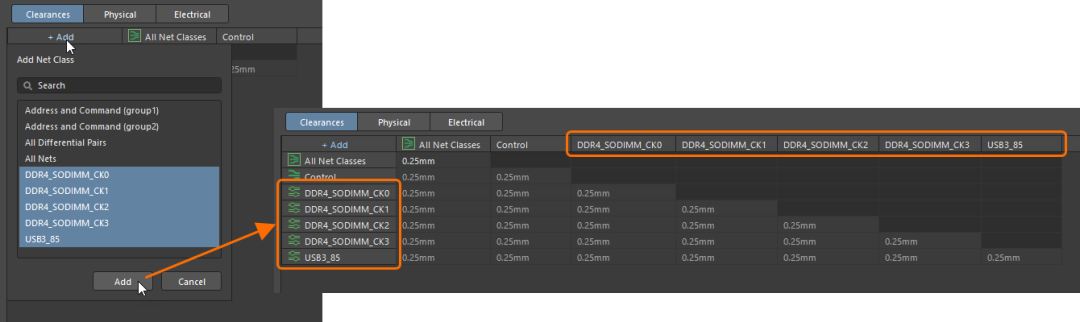

约束管理器改进

将差分对类别添加到间距矩阵中

自本次发布以后,您即可将网络类和差分对类添加到Clearances Matrix(Clearances视图)中。

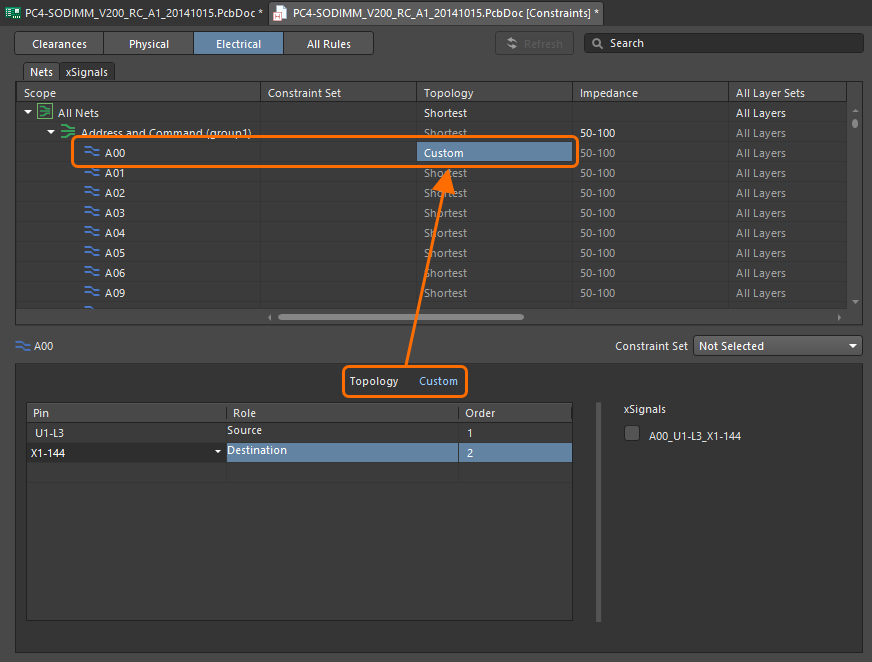

在PCB端对自定义拓扑结构进行编辑

现在可以将网络的拓扑结构定义为Custom,并在从PCB端访问网络时根据需要在Constraint Manager中对其进行编辑。

编辑约束集时传播拓扑结构更改

当对包含自定义拓扑结构的Constraint Set进行编辑时,对拓扑结构所做更改现在将传播到应用此Constraint Set的其他对象。

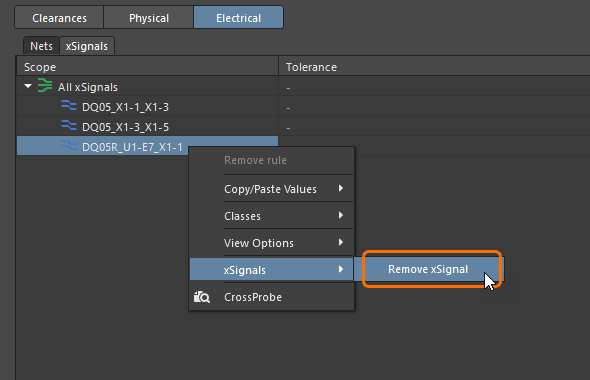

具备了删除xSignals的能力

现在可以从Electrical视图的xSignals选项卡中,删除xSignal。操作时,请右键单击xSignal,然后从上下文菜单中选定xSignals » Remove xSignal命令。

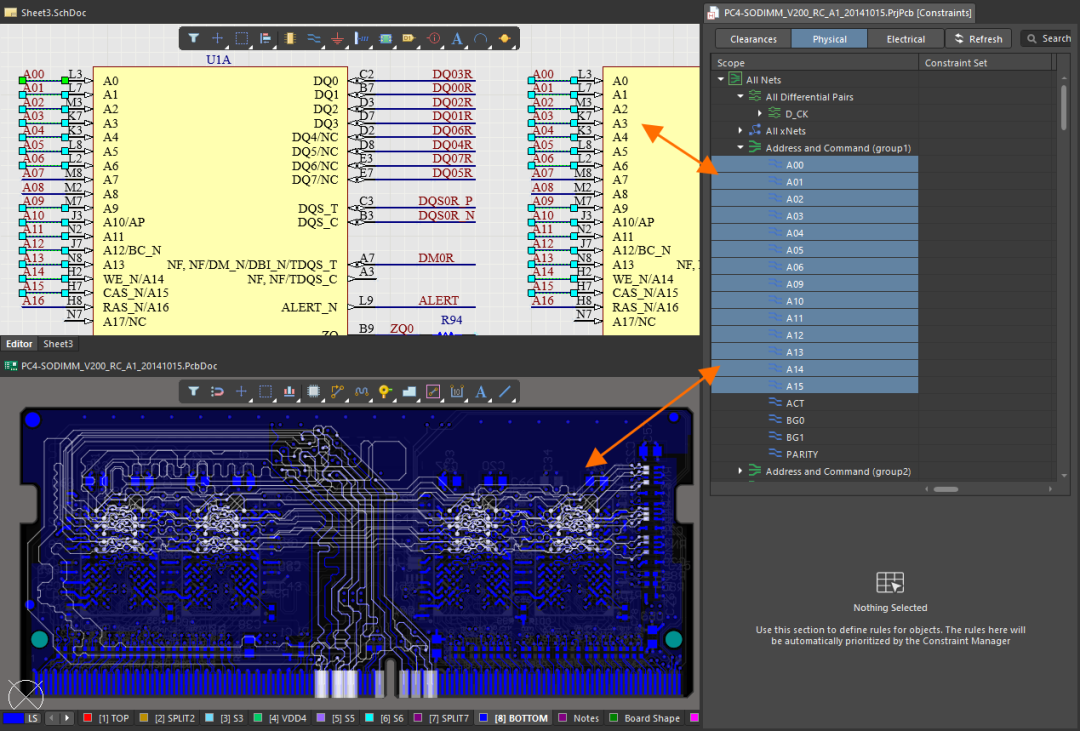

Constraint Manager交叉选定

在本次发布中,添加了从Constraint Manager中交叉选定对象的功能。(使用Constraint Manager、原理图或PCB编辑器Tools主菜单中的Cross Select Mode命令)启用交叉选定模式后,在Constraint Manager中选定的对象亦会在原理图和PCB文档中被选定,反之亦然。

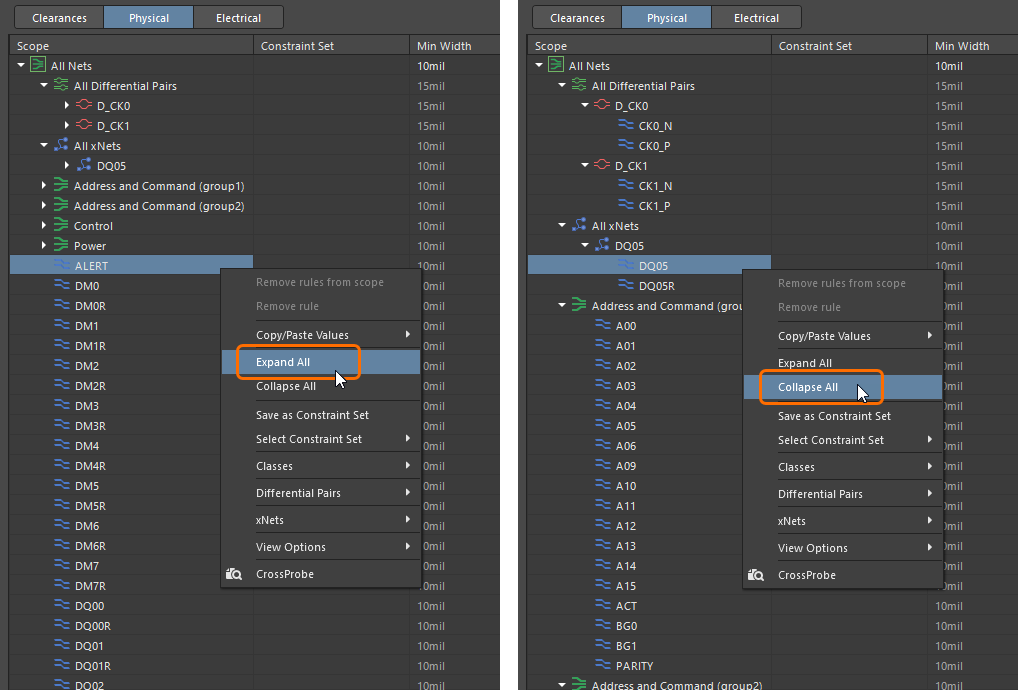

增强了展开/折叠状态

除预定义节点(例如,All Nets)以外,所有节点现在均默认在Physical和Electrical视图中折叠。您可以使用新Expand All和Collapse All右键单击菜单命令来控制网格节点。

如需了解更多信息,请参阅 Defining Design Requirements Using the Constraint Manager 页面。

如需了解更多信息,请参阅 Defining Design Requirements Using the Constraint Manager 页面。

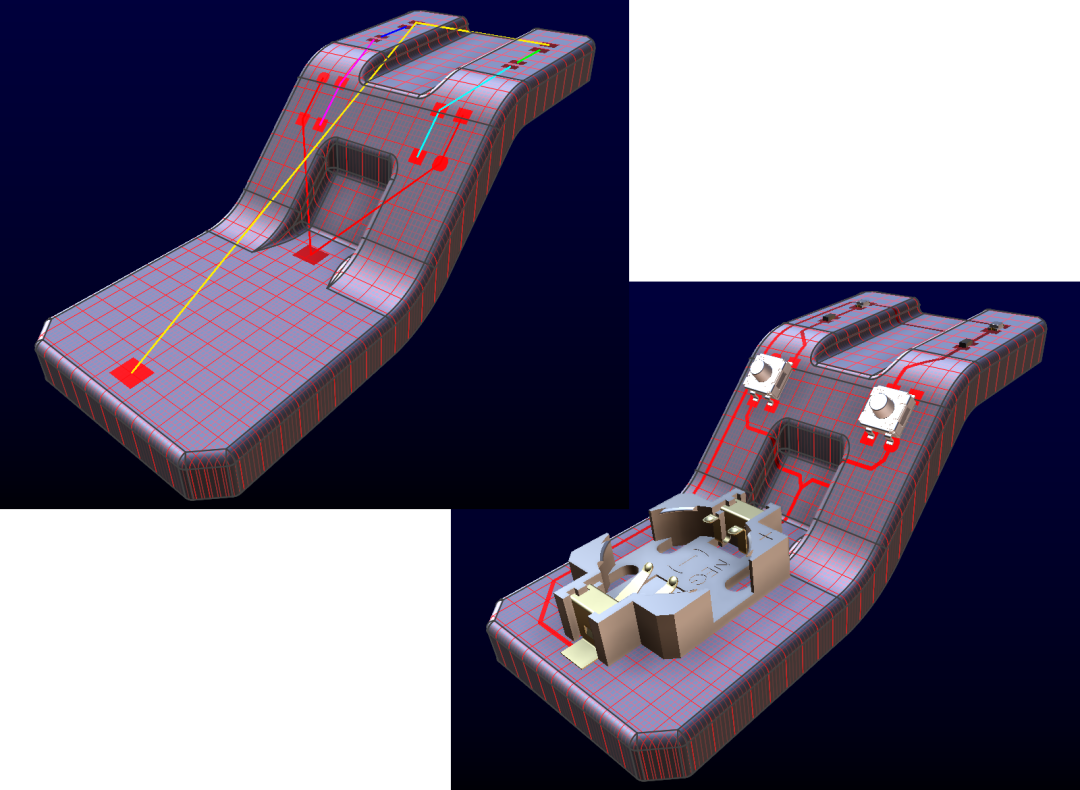

3D-MID设计(Open Beta版)

3D-MID技术将威廉希尔官方网站 与三维机械部件相结合。此项功能融合给各种应用领域带来了无限可能。

一直以来,由于缺乏合适的ECAD工具,3D-MID设计人员通常仅限于使用MCAD封装。这种工作方式会存在许多固有问题,尤其是其无法通过电气智能来驱动威廉希尔官方网站 布局,并且存在与将2D手动绘制草图投影到3D表面相关的困难。

Altium Designer中新3D-MID编辑器允许您将标准表贴元件放置在3D-MID文档内的3D形状上,并沿形状表面进行导线布线以完成布局。

然后,可以将完成的设计导出为Laser Direct Structuring(LDS)制造工艺所需的文件格式。

如需了解关于此功能的详细信息,请参阅3D-MID Design。

请注意,Altium Designer Standard Subscription不支持3D-MID功能。如果您对3D-MID感兴趣并拥有Standard Subscription,请与Altium销售代表联系,以了解您的评估选项。

此功能目前处于Open Beta阶段,且仅当在Advanced Settings对话框中启用System.3DMID选项时可用。

线束设计改进

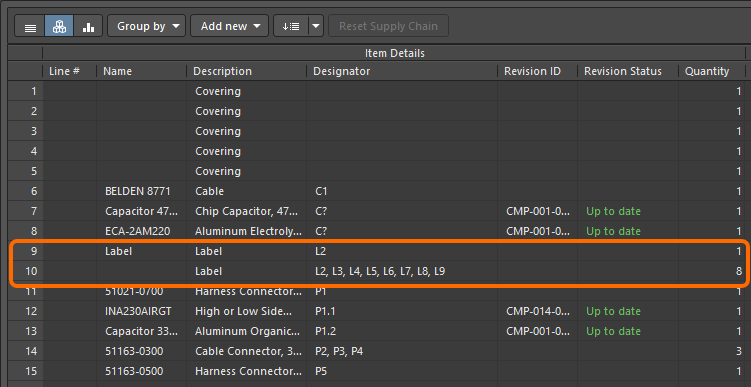

将布局标签视为BOM中的元件

Layout Drawing中的布局标签现在被视为BOM中的元件,并支持部件选择和分组。

如需了解更多信息,请参阅Creating the Harness Layout Drawing页面。

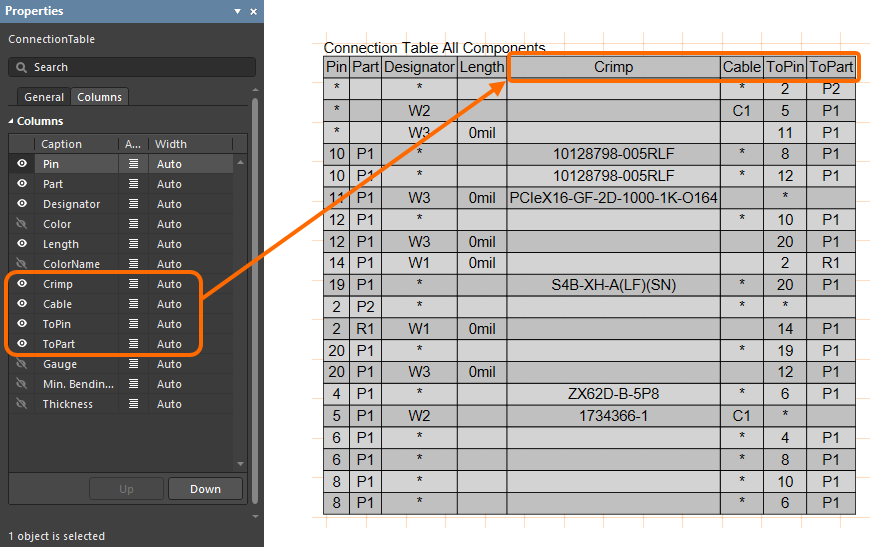

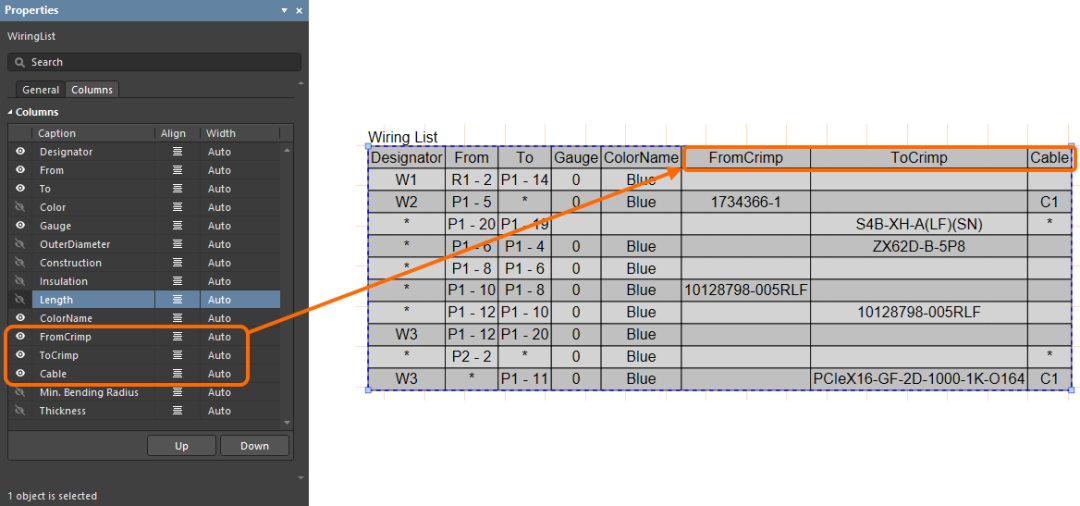

在连接表和接线列表中添加了列

在Manufacturing Drawing(*.HarDwf)的Connection Table和Wiring List中添加了其他列,以确保您可以轻松查看设计区内的附加信息。Crimp(部件编号)、Cable、ToPin和ToPart均已添加到Connection Table中;FromCrimp、ToCrimp和Cable均已添加到Wiring List中。在Properties面板中切换眼睛图标,以显示/隐藏连接表中的所需列。

如需了解更多信息,请参阅 Creating a Manufacturing Drawing for a Harness Design 页面。

平台改进

支持长路径名称(Open Beta版)

在本次发布中,实现了对长路径名称的支持。当文件名称的文件路径超过256个字符时,现在支持对文件执行以下操作:

从连接的Workspace打开项目。

使本地项目在Workspace中可用。

更改Outjob文件中的文件夹路径。

使用Outjob文件或Project Releaser生成输出。

将项目作为项目模板保存到Workspace中。

自Windows 10版本1607开始,已将MAX_PATH限制从常用Win32文件和目录函数中删除。但是,您必须通过更改Altium Designer所在计算机的注册表项来选择加入新功能。如需了解更多信息,请参阅Support for Long Path Names页面。执行此操作后,请务必重新启动计算机。

警告:不恰当地修改注册表,可能会导致Windows无法使用。请您自行承担使用Registry Editor的风险,并按照Microsoft文章How to back up and restore the registry in Windows中的说明进行注册表备份。

当发布使用长路径到Enterprise Server Workspace的项目时,还应配置安装Altium On-Prem Enterprise Server的PC:了解更多。

此功能目前处于Open Beta阶段,且仅当在Advanced Settings对话框中启用System.LongPathsSupport选项时可用。请注意,此选项仅当将LongPathsEnabled注册表项设置为1时可用。

如需了解更多信息,请参阅Support for Long Path Names页面。

导入/导出改进

xDX Designer导入增强功能

本次发布中提供了许多与将xDX Designer设计文件导入Altium Designer相关的关键改进和修复。

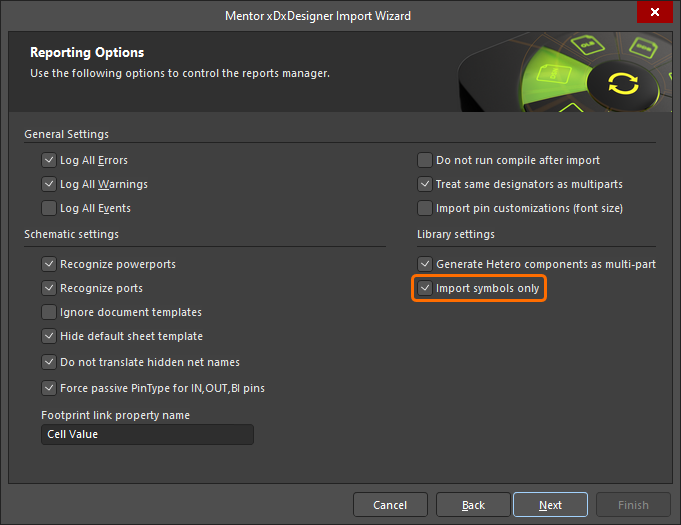

添加了仅导入符号功能

Mentor xDxDesigner Import Wizard的Reporting Options页面现在包括仅允许导入符号的Import symbols only选项。启用此选项后,即使原始元件库中多个元件使用该符号,元件库数据库中的相同符号亦将作为单个原理图符号导入,并且参数不会导入到Altium Designer中的符号内。

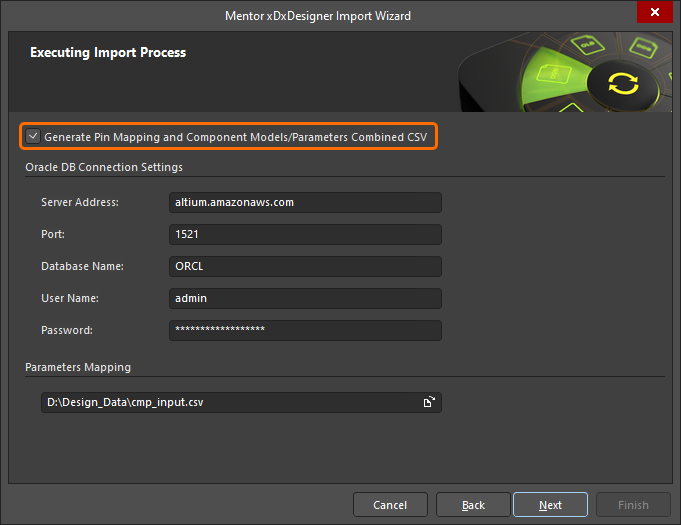

此外,启用此选项后,Wizard的下一页将建议通过启用Generate Pin Mapping and Component Models/Parameters Combined CSV选项,以CSV格式生成部件符号和引脚映射数据。启用此选项后,即可使用可用字段对Oracle DB连接参数和参数映射文件进行定义。

多部件符号导入改进

导入Altium Designer时,多部件符号会收到一个Design Item ID,以及在xDX Designer中定义的第一个和最后一个部件名称。此类组合型Design Item ID亦可用在生成的CSV文件中。

此外,将符号中部件导入Altium Designer的顺序现在与原始元件库中定义的顺序相同。

符号导入改进

其他导入改进包括:

现在可导入符号中的静态文本字符串。

xDX Designer中用于否定的‘~’字符现在被转换为引脚名称中的‘’字符,以确保可在Altium Designer中正确表示否定符号。

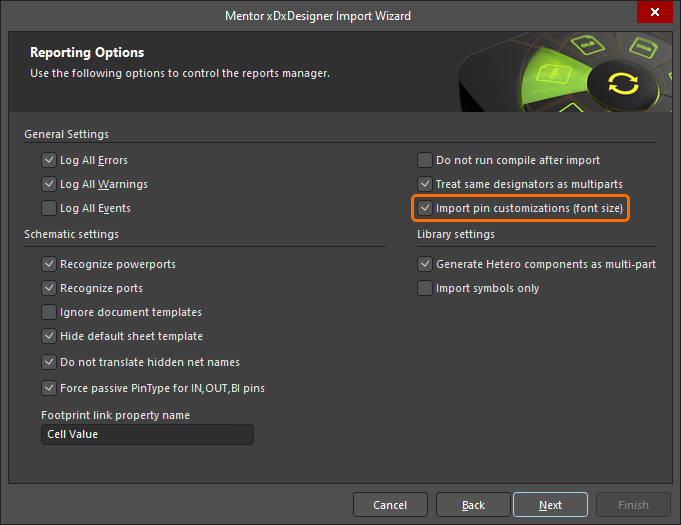

Mentor xDxDesigner Import Wizard的Reporting Options页面现在包括Import pin customizations(字体大小)选项。启用此选项后,引脚位号标识符和名称均将以与xDX Designer中的相同字体大小,被导入Altium Designer。

如需了解更多信息,请参阅Importing a Design from xDX Designer or DxDesigner 页面。

Mentor Expedition导入改进

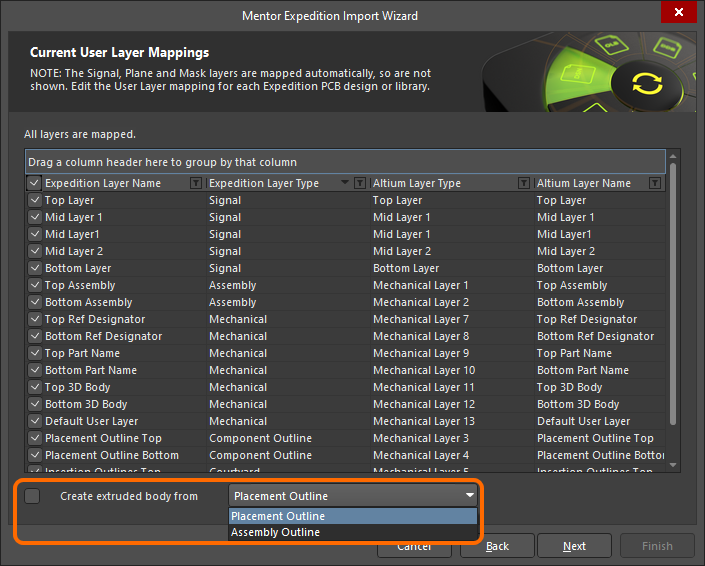

添加了选择挤压体层的功能

您现在可以在使用Import Wizard导入Mentor Expedition文件时,选定创建挤压体时需要的层。添加想要导入的Mentor PCB和Library文件后,使用Current User Layer Mappings页面上的Create extruded body from drop-down从Placement Outline或Assembly Outline中进行选择。启用该选项后,其将默认为Placement Outline。

Placement Outline改进

现在可以将Placement Outlines作为基元导入到Top/Bottom 3D Body组装层的Placement Outline上。

如需了解更多信息,请参阅 Importing a Design from Xpedition 页面。

威廉希尔官方网站 仿真改进

P-Channel晶体管的输出电流反相

P-Channel晶体管(BJT、JFET、MOSFET、MESFET)的输出电流现在将被视为流入电流,以确保其与N-Channel晶体管一致。

如需了解更多信息,请参阅 Creating a Simulation Model 页面。

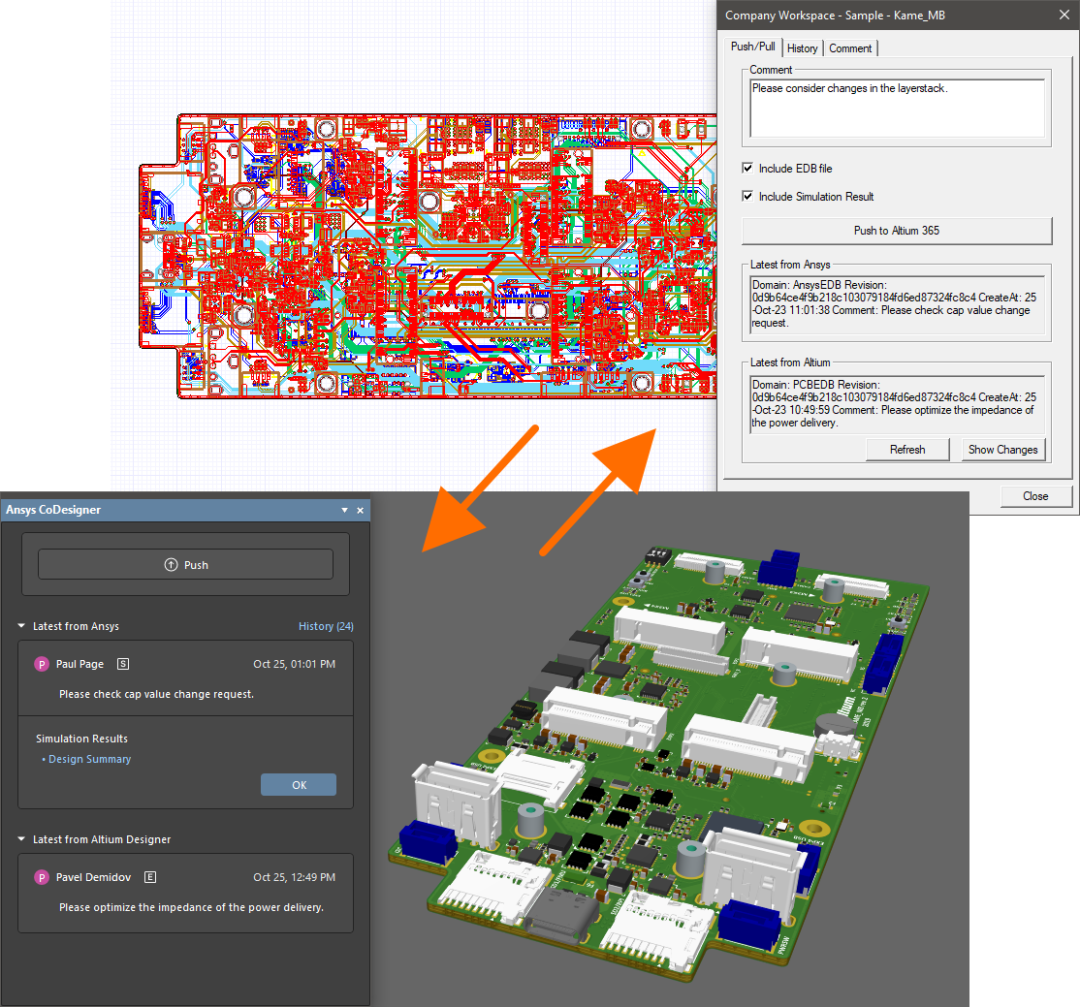

Ansys CoDesigner(Open Beta版)

本次发布介绍了在ECAD与Simulation域之间实现真正协作设计(CoDesign)的第一步。到目前为止,这两个孤立领域的工程师不得不依赖手动导出/导入文件流程,这些流程与设计修订以及变更和结果的沟通(通常通过电子邮件)只能在设计领域之间手动交互。

随着Ansys CoDesigner功能的推出,ECAD工程师(使用Altium Designer)现在可以与SIM工程师同事(使用Ansys Electronics Desktop(AEDT))进行无缝协作设计。Altium 365 Workspace将作为两个领域之间的桥梁,促进双方开展协作。本次首次发布包括对以下关键元素的支持:

两个领域之间可实现设计更改双向推/拉。在Altium Designer中,可以检测针对层堆栈以及材料、元件和基元所做的更改,并可在AEDT中进行应用。从AEDT中,可以通过EDB文件,推送针对层堆栈和材料的拟议更改,并在Altium Designer中进行检测/应用。

可将仿真结果从AEDT推送到Altium 365 Workspace,并与设计修订建立关联,以通过Workspace的浏览器界面对其进行查看,并在Altium Designer中进行预览。

使用注释系统进行双向通信,且每个注释线程均随附于设计中的特定元件。

Ansys CoDesigner目前支持2023 R1和2023 R2版本的AEDT。

如需了解更多信息,请参阅 Ansys CoDesigner 页面。

请注意,Altium Designer Standard Subscription不支持Ansys CoDesigner。

此功能目前处于Open Beta阶段,且仅当安装Ansys CoDesigner(用于Altium Designer)和Altium Link(用于Ansys Electronics Desktop)扩展时可用。后者可以通过联系 ansyscollaboration@altium.com 获得。

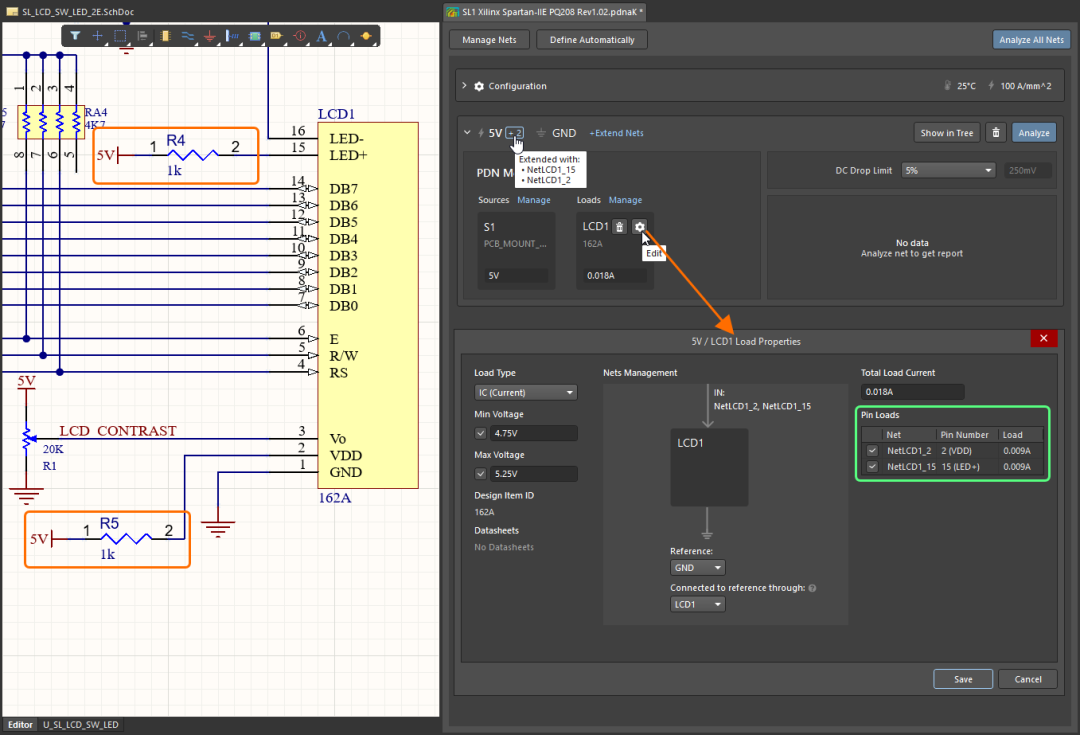

Power Analyzer by Keysight改进

添加了在同一元件上为多个网络分配电流的功能

在本次发布中,添加了在同一元件上为不同串行元素的多个网络分配电流的功能。

配置IC(Current)型负载时,您可以看到负载元件的所有引脚,这些引脚通过不同串行元件与源连接,并能够选定所需的引脚。

在以下示例中,5V电源网络通过R4和R5串行元件连接到LCD1元件的两个引脚。扩展电源网络并将LCD1作为负载添加后,可根据需要在Load Properties对话框中对两个引脚进行选定和配置。

如需了解更多信息,请参阅Power Analyzer QuickStart Guide页面。

Altium Designer 24.0中完全公开的功能

以下功能现已在本次发布中正式公开:

约束管理器 - 自23.11版开始提供

PCB CoDesign - 自23.10版开始提供

线束设计 - 自23.0版开始提供

改进版最小孔环违规检测 - 自22.10版开始提供

审核编辑:汤梓红

-

原创Altium Designer 17全程安装及新功能视频教程2016-11-20 0

-

Altium Designer®18新功能先睹为快2017-06-13 0

-

Altium Designer 20 新功能官方直播2019-12-27 0

-

Altium Designer 6.3 新功能教程2009-09-28 634

-

Altium Designer 6.8的新功能介绍2011-02-13 1347

-

Altium Designer14版本下载入口2017-01-05 999

-

altium_designer_16.1.11_软件下载2018-04-03 1325

-

Altium Designer版本14.2的发行说明详细说明2019-12-23 1098

-

Altium Designer 23.2.1版本发布,新功能说明2023-02-24 1710

-

Altium Designer 23.3.1版本发布,新功能说明2023-03-31 2088

-

Altium Designer 23.4.1版本新功能说明2023-04-21 1176

-

Altium Designer 23.5.1版本发布,新功能说明2023-05-26 2715

-

altium designer哪个版本稳定2024-01-04 22743

-

Altium Designer 24.3.1版本发布,新功能说明2024-03-29 3224

-

Altium Designer 24.7.2版本新功能图解说明2024-08-05 2521

全部0条评论

快来发表一下你的评论吧 !