为什么要在IIC信号线上加上拉电阻

描述

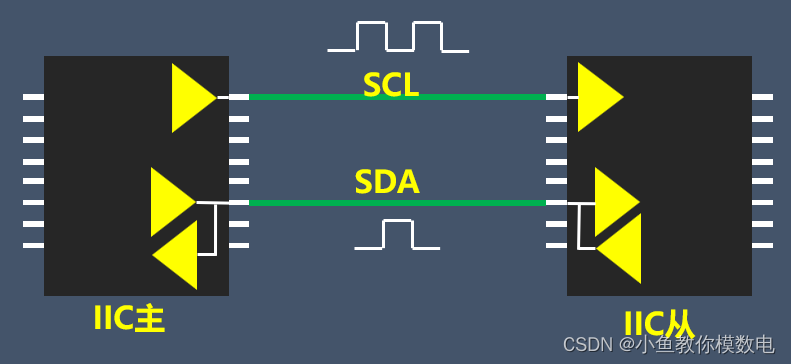

IIC 是一个两线串行通信总线,包含一个 SCL 信号和 SDA 信号,SCL 是时钟信号,从主设备发出,SDA 是数据信号,是一个双向的,设备发送数据和接收数据都是通过 SDA 信号。

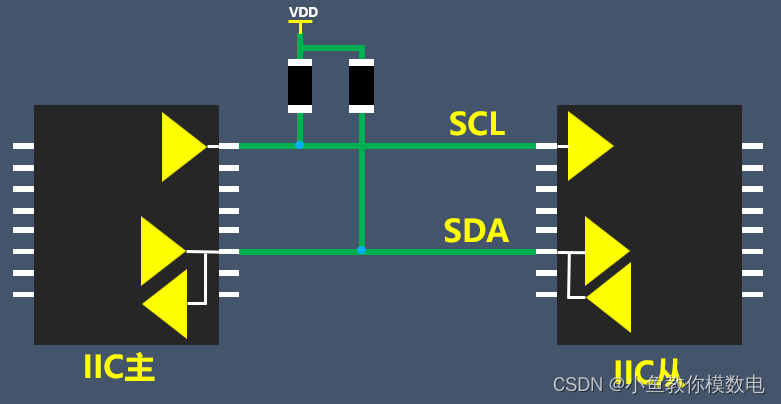

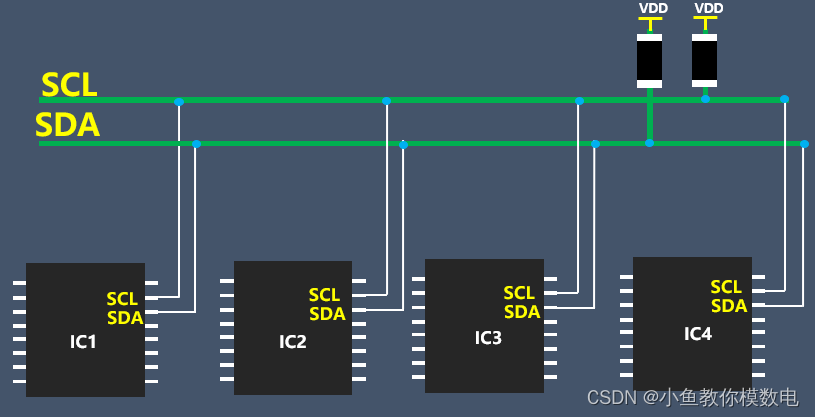

在设计 IIC 信号威廉希尔官方网站 的时候我们会在 SCL 和 SDA 上加一个上拉电阻。

今天就来分享下,为什么要在 IIC 信号线上加上拉电阻。

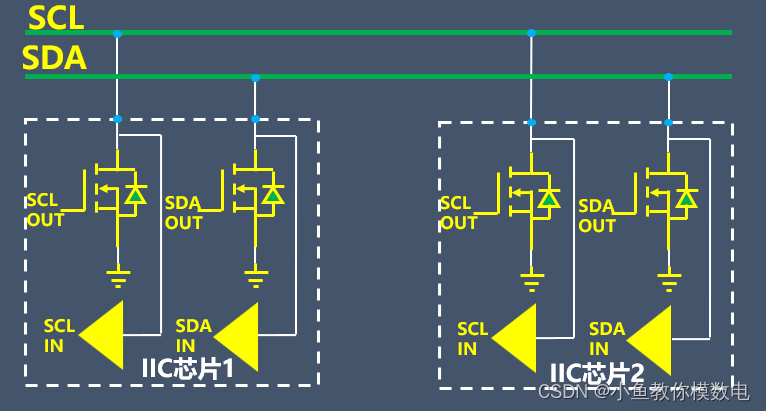

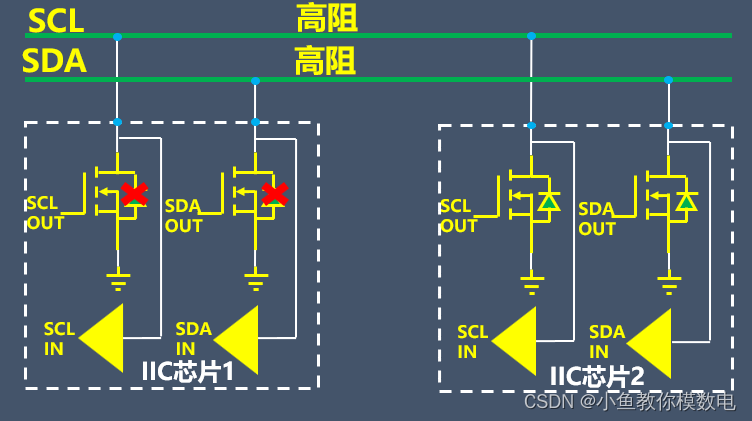

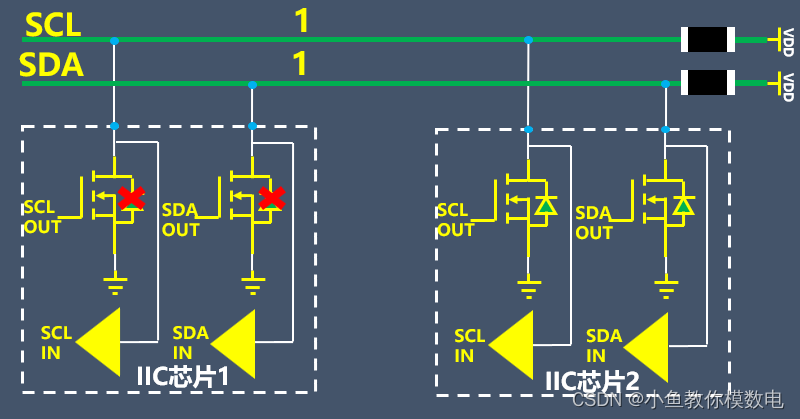

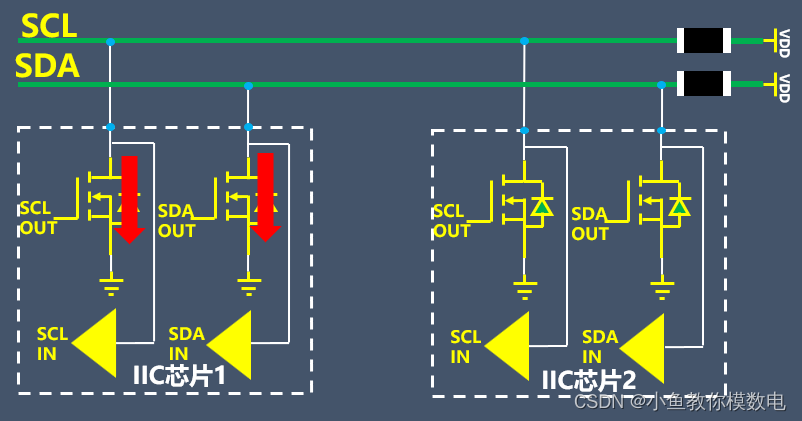

主要原因就是 IIC 芯片的 SDA 和 SCL 的引脚是开漏输出,就是只有一个 NMOS 管,不像推挽输出有两个 MOS 管。

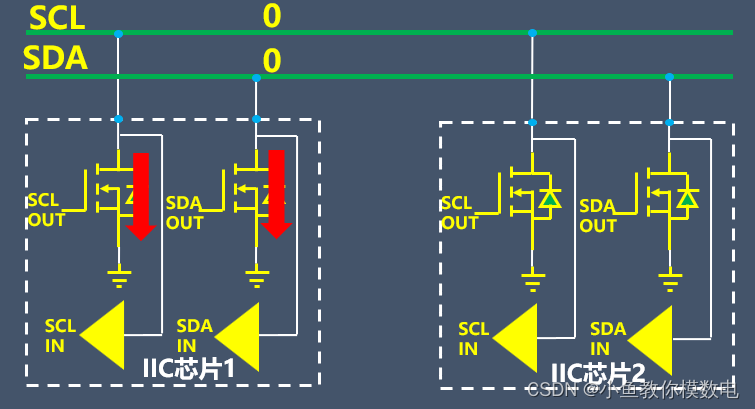

当芯片 SDA 和 SCL 的引脚输出 MOS 管导通,IIC 信号线电平为低电平。

当芯片 SDA 和 SCL 的引脚输出 MOS 管关闭,如果没有上拉电阻,IIC 信号线是处于一个高阻状态,电平是未知的,开漏输出是没有高电平的输出能力的。

所以加上上拉电阻后,当芯片 SDA 和 SCL 的引脚输出 MOS 管关闭,IIC 信号线上的电平就是一个确切的高电平。

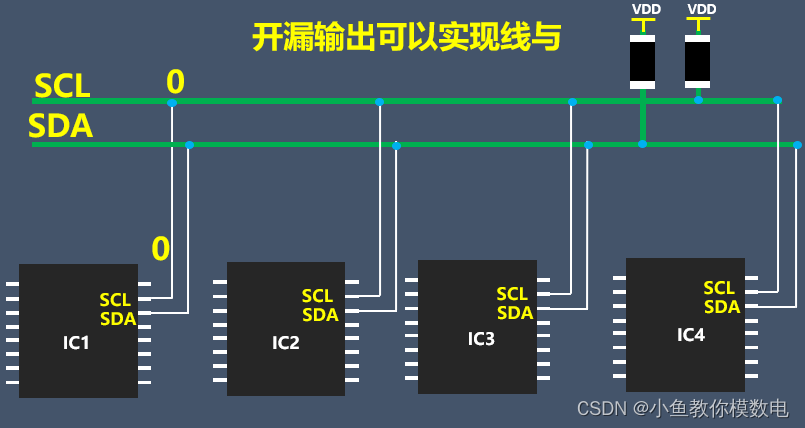

当多个 IIC 设备通过 IIC 总线接在一起,这就要求 IIC 设备间可以实现线与,而芯片的 IIC 引脚是开漏输出的话就能很好的实现这个线与。只要有一个 IIC 设备的引脚电平是低电平,那么相应的 SCL 或 SDA 总线也会成为一个低电平。如果 IIC 设备引脚为推挽输出,多个 IIC 设备接在一条总线上很容易烧坏芯片。

IIC 上拉电阻的取值

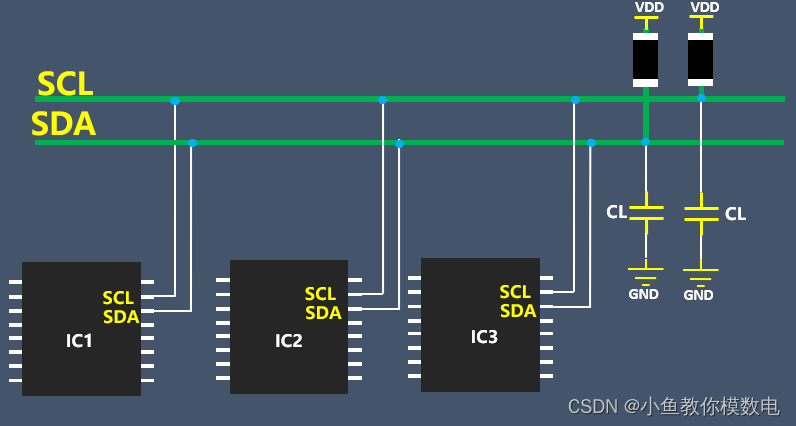

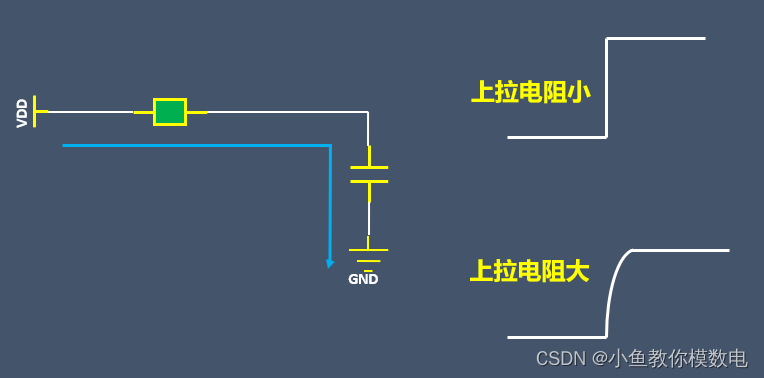

IIC 信号的上拉电阻阻值不能太大,因为 IIC 芯片 SCL 和 SDA 引脚都存在寄生电容,同时 SDA 和 SCL 信号的走线也会有寄生电容,整个 IIC 总线上相当于接了一个负载电容 Cl

上拉电阻过大,IIC 总线高电平的驱动能力差,总线电平从 0 到 1 变化时,等效为这个 RC 的充电威廉希尔官方网站 ,上拉电阻越大,波形上升沿会变缓,一定程度会影响 IIC 的时序,可能会出现误码。所以这个上拉电阻不能太大。

IIC SDA 和 SCL 信号的上升时间和总线电容在不同的模式下有不同的要求,大家可以看下这个表。

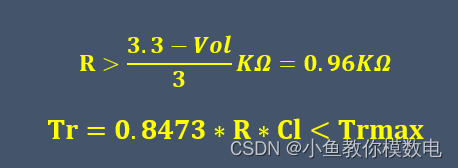

IIC 总线信号上升时间可以根据公式 Tr=0.8473*R*Cl Cl 就是 IIC 总线的等效负载电容

IIC 信号上拉电阻也不能太小,如果太小了,当 IIC 引脚输出低电平时,灌进芯片 IIC 引脚的电流会变大,可能会使 IIC 信号线的低电平变大,同时 IO 口电流过大还可能烧坏芯片。

我们一般要求,IIC 引脚低电平时,流过芯片 IIC 引脚的电流小于 3mA,所以如果是 3.3V 上拉的话,这个电阻就要 R>(3.3-VoL)l3KΩ=0.96KΩ ,其中 VoL 是 IIC 引脚为低电平时的最大电压,一般是 0.4V。再加上前面的这个公式我们就可以确定这个上拉电阻的取值范围。

电源电压决定上拉电阻的最小值,总线负载电容决定上拉电阻的最大值。

IIC 信号上拉电阻取值常用的值就是 4.7K,一般小于 10K,大于 1K,如果 IIC 总线比较长,从设备比较多,可以适当降低电阻。

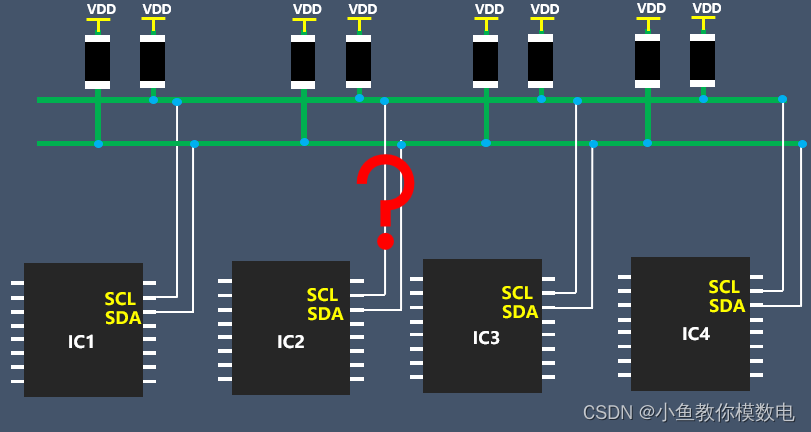

如果 IIC 总线接了很多 IIC 设备,是不是每个 IIC 设备都要加上拉电阻?

答案是否定的,我们只要在 SDA 和 SCL 总线上合适的位置各加一个上拉电阻即可,如果每个设备都加上拉,相当于这些电阻是并联在一起了,减小了电阻值。至于上拉电阻的位置一般没有特别的要求。一般加在 IIC 的末端。

审核编辑:汤梓红

-

为什么要在信号线上串接电阻?学习电子知识 2023-09-05

-

SD卡的时钟线为什么可以不加上拉电阻呢?是因为时钟永远是输出信号吗?为什么输出信号就可以不加上拉电阻2021-11-18 0

-

PCA9685芯片的模拟的IIC需要加上拉电阻吗?2023-10-18 0

-

关于单片机加上上拉电阻的详细解释2017-12-18 11402

-

iic通信协议是什么2019-09-13 19947

-

集电极加上拉电阻的作用2019-09-28 9439

-

上拉电阻与下拉电阻的概念详解2021-02-20 9474

-

IIC上拉笔记2022-01-14 508

-

IC之间的信号线为什么要接一个小电阻?2023-05-08 1723

-

什么是上拉电阻?如何计算I2C上拉电阻的大小值2023-10-12 6493

-

信号线或电源线上串个小电阻干啥用的?2023-11-23 2738

-

信号线上串接电阻的作用及其对整个威廉希尔官方网站 的影响2023-12-21 3153

-

信号线上为什么要加铁氧体磁环2023-12-21 1264

-

IIC信号线需要增加上拉电阻,是因为IIC的IO是什么2024-10-06 715

-

I2C总线上拉电阻阻值如何确定?2024-12-27 444

全部0条评论

快来发表一下你的评论吧 !