B码对时方案,基于TI AM62x异构多核工业处理器实现!

电子说

描述

什么是IRIG-B码对时

IRIG-B(inter-range instrumentationgroup-B)码是一种时间同步标准,通常用于精确的时间测量和数据同步,广泛应用于电力、通信、航空等领域。

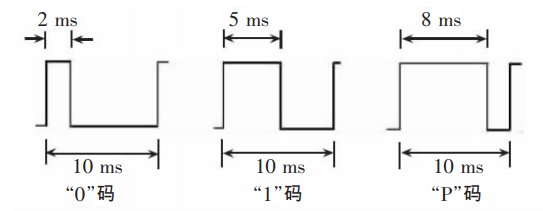

IRIG-B码为每秒一帧的时间串码,一帧串码中包含100个码元,频率为1KHz,即每个码元占用10ms时间。IRIG-B码基本的码元为"0"码元、"1"码元和"P"码元,"0"码元和"1"码元对应的脉冲宽度为2ms和5ms,"P"码元为位置码元,对应的脉冲宽度为8ms,IRIG-B码信息的基本码元的示意图如下所示。

图1

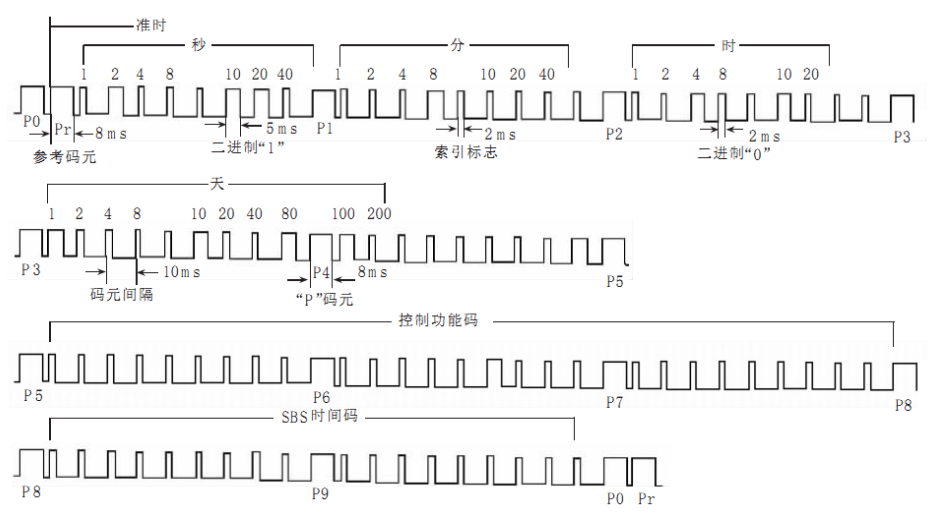

下图为一帧的IRIG-B码脉冲序列结构示意图。连续两个"P"码元表示整秒的开始,第二个"P"码元的脉冲前沿为“准时”参考点,定义其为"Pr"。每10个码元有一个位置码元,共有10个,定义其为P1,P2,…,P9,P0。IRIG-B码时间格式的时序为秒、分、时、天,所占信息位分别为:秒7位、分7位、时6位、天10位,其位置在P0 ~ P5之间。

通常,从"Pr"开始对码元进行编号,分别定义为第0,1,2,…,99码元,则“秒”信息位于第1、2、3、4、6、7、8码元,“分”信息位于第10、11、12、13、15、16,17码元,“时”信息位于第20、21、22、23、25、26码元,“天”信息位于第30、31、32、33、35、36、37、38、40、41码元。

图2

IRIG-B码对时应用场景

IRIG-B码对时可应用于继电保护装置、电力RTU、电力录波器、通讯管理机、电能质量在线监测等领域。创龙科技已基于TI AM62x异构多核处理器实现IRIG-B码对时方案,降低了终端用户的开发难度,缩减了研发时间,可快速进行产品方案评估与技术预研。

图3

常见IRIG-B码对时实现方案

IRIG-B码对时的实现常见方案一般基于FPGA或MCU实现,具体方案实现方式如下。

(1)基于FPGA实现

为达到IRIG-B码与时间信号输入、输出的精确同步,采用现代化靶场的IRIG-B码编码和解码的原理,从工程的角度出发,提出了使用现场可编程门阵列(FPGA)来实现IRIG-B码编码和解码的设计方案和体系结构,设计中会涉及到几个不同的时钟频率,FPGA对时钟的同步性具有灵活性、效率高、且功耗低,抗干扰性好的特点。结果表明,FPGA能够确保为从设备提供同源的时钟基准,使时钟与信号的延迟控制在200ns以内,从而得到了IRIG-B码与时间精确同步的效果。

但是,基于FPGA实现IRIG-B码开发难度较大,时间投入较多,开发成本将会较高,不利于产品的快速上市。

(2)基于MCU实现

MCU(Micro Control Unit)即微控制单元,通过MCU核心可实现解析IRIG-B码时序并提取时间信息,再将时间信息同步至其他核心。

基于MCU实现IRIG-B码开发方案结构简单、开发成本较低、同步精度较高,可满足多种工业应用场景要求。

AM62x IRIG-B码对时方案

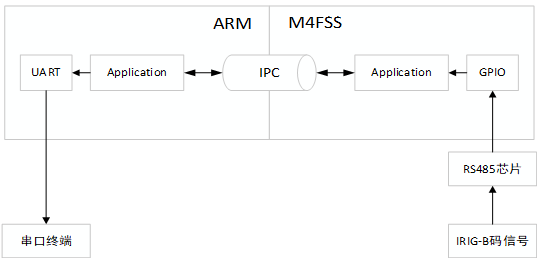

本章节主要描述创龙科技基于TI AM62x的MCU(Cortex-M4F)核心实现IRIG-B码信号解析功能。

AM62x内部集成Cortex-A53 + Cortex-M4F核心,可使用Cortex-M4F实现IRIG-B码对时功能,无需增加额外的MCU成本。并且,通过内部MCU实现IRIG-B码对时功能方案,硬件设计简单,有利于快速开发产品。

(1)案例说明

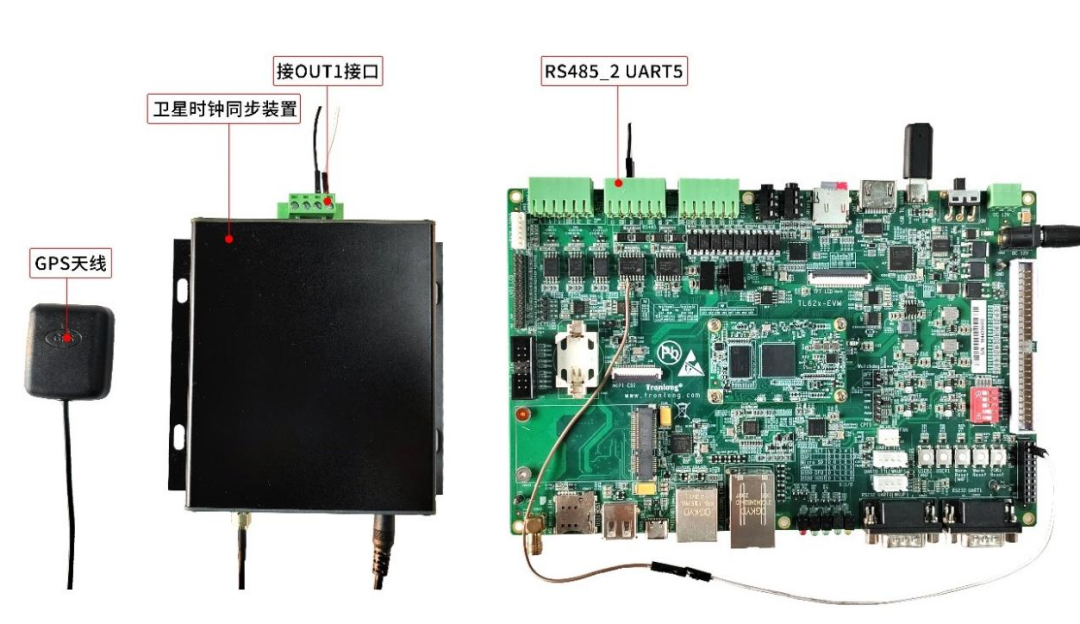

卫星时钟同步装置(厂家:南京诺煌电气科技有限公司,型号:YS-DN-100)通过GPS天线模块获取标准时间信息并输出IRIG-B码信号,经评估板板载RS485芯片转换成电平信号后传输至Cortex-M4F核心,Cortex-M4F核心通过读取GPIO引脚电平,解析IRIG-B码时序并提取时间信息,再通过TI-RPMsg机制将时间信息发送至Cortex-A53核心打印时间信息。系统框图如下所示。

图4

(2)

案例测试

本案例需在开阔场地进行测试,请确保卫星时钟同步装置的RUN指示灯处于常亮状态(表示设备工作正常),否则请检查GPS天线连接是否正常。

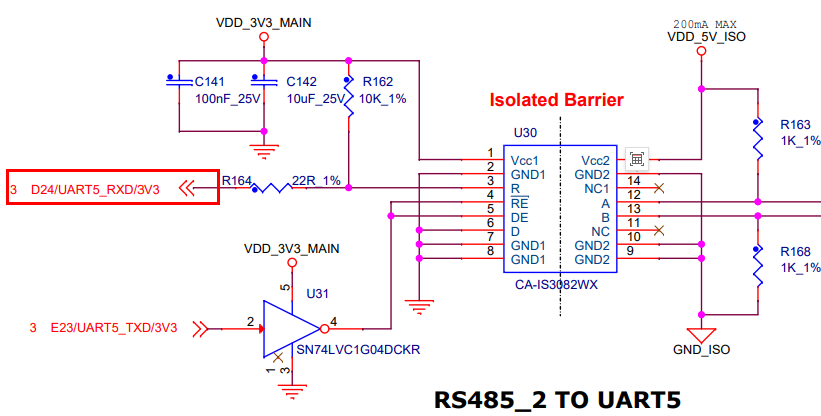

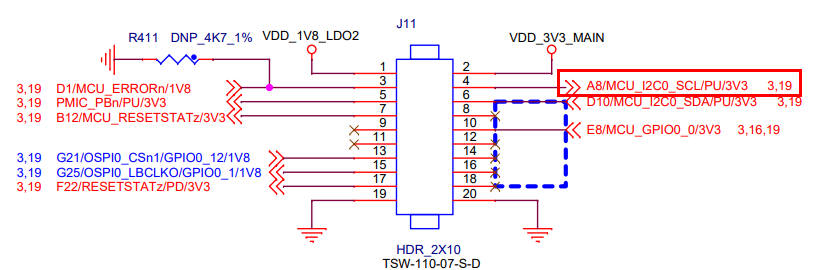

由于评估底板RS485_2 UART5为Cortex-A53核心的外设,因此请通过飞线的方式将RS485芯片(U30)的pin3引脚连接至EXPROT接口(J11)的pin4引脚(即Cortex-M4F核心GPIO)。卫星时钟同步装置输出的IRIG-B码信号经评估底板RS485_2 UART5接口后,再经过EXPROT接口(J11)的pin4引脚输入至Cortex-M4F核心。

图5

图6

请将卫星时钟同步装置的ANT接口连接至GPS天线模块,将卫星时钟同步装置OUT1接口的“+端子”连接至评估板的RS485_2 UART5接口“A2端子”、OUT1接口的“-端子”连接至评估板的RS485_2 UART5接口“B2端子”,硬件连接如下图所示。

图7

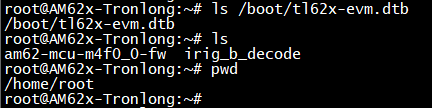

请将本案例"dtsbin"目录下的tl62x-evm.dtb设备树文件拷贝至Linux系统启动卡"/boot/"目录下,替换原有的tl62x-evm.dtb设备树文件。然后将案例bin目录下的am62-mcu-m4f0_0-fw文件、irig_b_decode可执行程序拷贝至Linux系统启动卡文件系统"/home/root/"目录下。

图8

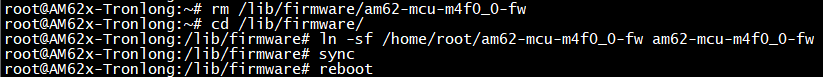

评估板上电,从Linux系统启动卡启动,依次执行如下命令,更新Cortex-M4F核心固件,并重启评估板。

Target#rm /lib/firmware/am62-mcu-m4f0_0-fw

Target#cd /lib/firmware/

Target#ln -sf /home/root/am62-mcu-m4f0_0-fw am62-mcu-m4f0_0-fw

Target#sync

Target#reboot

图9

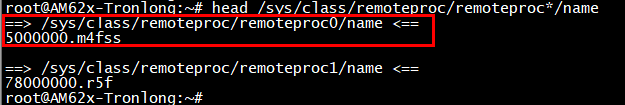

执行如下命令,查询Cortex-M4F核心与remoteproc对应关系。

备注:Cortex-M4F核心对应的RemoteProc Name为5000000.m4fss。

Target#head /sys/class/remoteproc/remoteproc*/name

图10

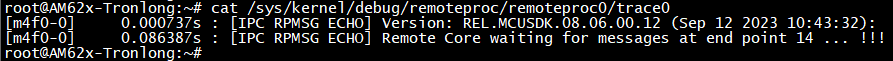

根据查询结果,执行如下命令查看Cortex-M4F核心程序运行日志,确认Cortex-M4F核心运行状态。

Target#cat /sys/kernel/debug/remoteproc/remoteproc0/trace0

图11

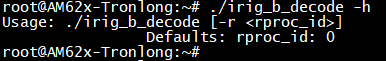

执行如下命令,查看程序运行参数。

Target#./irig_b_decode -h

备注:rproc_id:核心ID。Cortex-M4F核心ID为9,默认ID为0。

图12

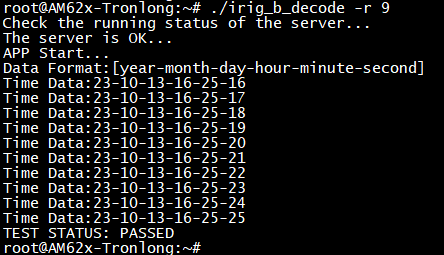

执行如下命令,解析IRIG-B码时序并提取时间信息,可看到串口终端打印当前日期如下图所示。

Target#./irig_b_decode -r 9

图13

审核编辑 黄宇

-

B码对时方案,基于TI AM62x异构多核工业处理器实现!2024-07-17 0

-

基于TI AM62x的Debian系统正式发布,丰富的软件生态,让您的应用开发更便利!2024-10-29 0

-

AM62x相比AM335x,到底升级了什么?2023-05-03 0

-

专用M4F+四核A53,异构多核AM62x让工业控制“更实时、更安全”2023-06-15 0

-

搭载TI Sitara AM62x系列工业级处理器的FET6254-C核心板2022-06-22 745

-

搭载TI AM62x处理器,飞凌FET6254-C核心板震撼发布2022-06-24 1118

-

TI AM62x接替AM335x,米尔核心板开发板2023-08-08 1189

-

AM62x基于GPMC的ARM+FPGA通信方案2023-09-25 1020

-

TI Sitara AM62x核心板软硬件参数资料规格书2022-09-07 559

-

TI Sitara系列AM62x开发板(4核ARM)规格书2022-09-21 576

-

米尔AM62x核心板,高配价低,AM335x升级首选2023-11-20 663

-

没抢到?米尔AM62x开发板限量5折又来了2024-05-17 508

-

GPMC并口多通道AD采集案例,基于TI AM62x四核处理器平台!2024-07-09 431

-

AM62x Sitara™处理器数据表2024-08-03 165

全部0条评论

快来发表一下你的评论吧 !