如何利用Tcl脚本在Manage IP方式下实现对IP的高效管理

描述

在Vivado下,有两种方式管理IP。一种是创建FPGA工程之后,在当前工程中选中IP Catalog,生成所需IP,这时相应的IP会被自动添加到当前工程中;另一种是利用Manage IP,创建独立的IP工程,缺省情况下,IP工程的名字为magaged_ip_project。在这个工程中生成所需要的IP,之后把IP添加到FPGA工程中。Xilinx推荐使用第二种方法,尤其是设计中调用的IP较多时或者采用团队设计时。Tcl作为脚本语言,在FPGA设计中被越来越广泛地使用。借助Tcl可以完成很多图形界面操作所不能完成的工作,从而,可提高设计效率和设计自动化程度。Vivado对Tcl具有很好的支持,专门设置了Tcl Shell(纯脚本模式)和Tcl Console(图形界面模式)用于Tcl脚本的输入和执行。本文介绍了如何利用Tcl脚本在Manage IP方式下实现对IP的高效管理。

Manage IP的特点:

(1)Vivado在Manage IP模式下只显示IP Catalog,便于直观地定制IP;

(2)IP工程目录独立于FPGA工程目录,可独立管理并便于IP复用;

(3)对IP采用OOC(Out-of-Context)的综合方式,生成相应的DCP文件,添加到FPGA工程中,无需再次综合;

与ISE Core Generator的不同之处:

(1)ISE Core Generator不同IP的生成文件会在同一目录下,而Vivado下每个IP有独立的文件夹,该文件夹下包含了IP所有相关文件,这为IP复用提供了便利;

(2)ISE Core Generator生成的IP定制文件为.xco,Vivado生成IP的定制文件为.xci;

(3)ISE Core Generator生成的网表文件为.ngc,Vivado生成的网表文件为.dcp,DCP不仅包含网表文件还包含约束文件;

(4)ISE Core Generator不支持Tcl脚本,Vivado则支持Tcl脚本;

Vivado下IP生成文件:

(1)用于综合的RTL文件和约束文件;

(2)实例化模板文件;

(3)行为级仿真文件;

(4)综合后的网表文件DCP;

(5)用于第三方综合工具的Stub文件;

(6)例子工程;

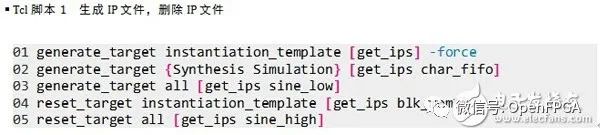

生成文件是可以定制的,这可通过generate_target命令完成,同时,生成的文件也可以通过reset_target被清除掉,如Tcl脚本 1所示。

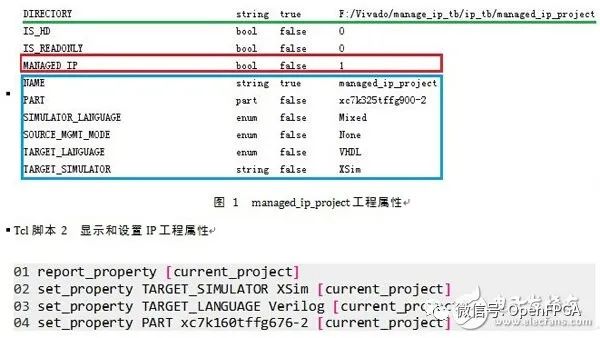

Vivado下每个对象都有自己的属性,这些属性可通过report_property显示。managed_ip_project的属性如图 1所示。图中绿色线条标记了该工程所在目录;红色方框MANAGED_IP属性值为1,表明该工程为IP工程;蓝色方框是我们创建或修改IP工程设置时最常用的一些属性。Tcl脚本 2中第1行语句用于显示IP工程属性,第2~4行语句用于设置仿真工具、目标语言和芯片型号。set_property命令的第一个参数为属性名,第二个参数为属性值,第三个参数为属性所属对象。

采用Vivado Manage IP创建IP工程后,可能会遇到以下情况:(1)软件版本升级,例如Vivado由2013.4升级至2014.2;(2)芯片型号改变,例如芯片型号由XC7K325TFFG676-2变为XC7K160TFFG676-2;(3)A项目中的一些IP在B项目中也被使用,且这些IP参数配置完全相同。上述三种情况均可通过Tcl命令完成。

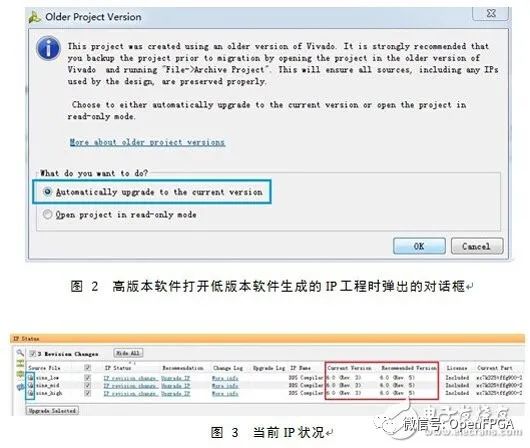

第一种情况:软件版本升级

假如用Vivado 2013.4创建的IP工程,当软件版本升级至2014.2时,需要将IP重新生成。此时,若用Vivado 2014.2打开该工程会弹出如图 2所示的对话框。选择图中蓝色方框标记的选项打开工程,通过report_ip_status命令显示当前IP状况,如图 3所示。

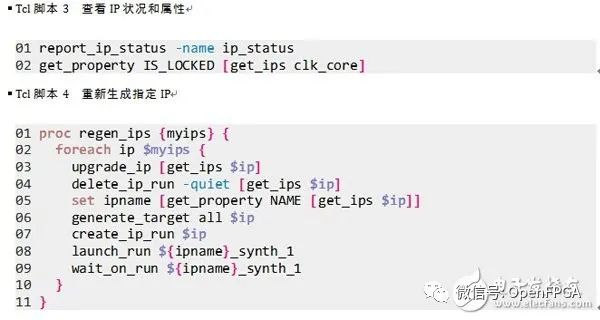

图 3中蓝色方框显示了IP处于锁定状态,可通过get_property查看IS_LOCKED属性确定;红色方框显示了IP当前版本号和建议升级到的新版本号。相应的Tcl脚本如Tcl脚本 3所示。对处于锁定状态的IP可选择升级,这可通过Tcl脚本 4完成指定IP的升级。Tcl脚本 4可内嵌到Vivado中作为用户常用命令。

第二种情况:芯片型号改变

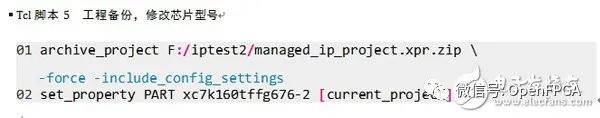

若芯片型号改变,首先要对旧型号芯片对应的工程做备份处理,这可通过archive_project命令完成;然后修改芯片型号。相应的Tcl脚本如Tcl脚本 5所示。完成这些操作之后,会发现IP处于锁定状态,此时可通过Tcl脚本 4对IP升级。

第三种情况:A项目中的一些IP在B项目中也被使用,且这些IP参数配置完全相同

在这种情况下,可将A项目中的IP导入到B项目的IP工程中,这可通过import_ip命令完成,如Tcl脚本 6所示。Import_ip的第一个参数为原始IP所在目录,第二个参数为该IP的新名字,缺省情况下与原始IP名一致。导入之后,可通过Tcl脚本 4重新生成IP。

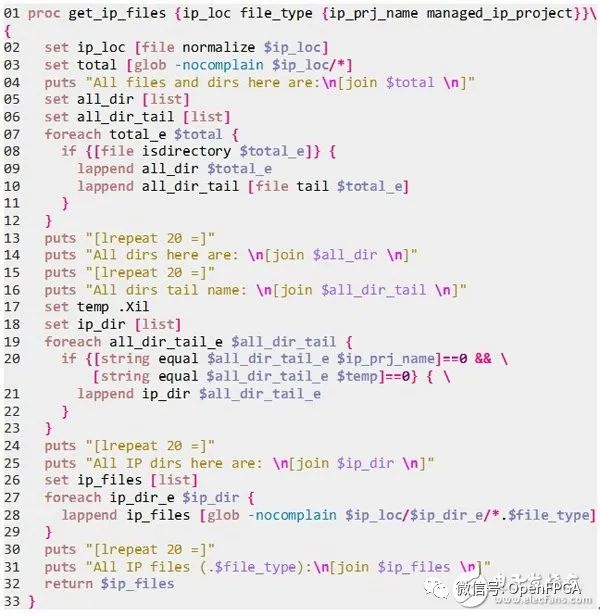

如前所述,Vivado下生成的IP都有独立的文件目录,在添加IP到Vivado FPGA工程中时,若采用图形界面方式就需要一个一个地浏览到IP所在文件目录,找到.xci文件,然后添加到工程中,如果调用的IP较多,显然这种方式不够高效。此时可用Tcl脚本 7所示的Tcl命令找到所有IP相关文件,文件类型可以是xci或dcp。该命令会返回完整的文件路径,如Tcl脚本 6中的文件路径。然后通过add_files命令将其添加到当前工程中。

此外,有些IP会有例子工程,这些例子工程带有完整的测试激励,可对IP进行仿真,以理解IP的输入/输出时序,也可单独生成bit文件。可通过open_example_project命令打开例子工程,如Tcl脚本 8所示。

与ISE Core Generator相比,Vivado Manage IP对IP的管理更加便捷,加之Vivado对Tcl脚本的支持,利用Tcl脚本可实现对IP更高效的管理,进一步加强FPGA设计自动化的程度。

审核编辑:黄飞

-

有效的代理IP采用合适的切换方法用户可以实现高效的网络IP切换操作jf_62215197 2024-08-20

-

如何使用FPGA和IP Core实现定制缓冲管理?2021-04-29 0

-

在Vivado图形化界面IDE中运行和调试Tcl命令2022-06-17 0

-

介绍IP数据报的格式及IP相关功能在Lwip中的实现方式2022-08-23 0

-

利用面向对象技术进行可配置的FFT IP设计与实现2010-07-04 831

-

利用FFT IP Core实现FFT算法2008-01-16 6918

-

在LabVIEW中利用TCP_IP协议实现网络通信_labview程序案例2016-01-12 4260

-

在LabWindowsCVI 中利用TCP_IP协议_labview程序案例2016-01-12 549

-

在Vivado下利用Tcl脚本对综合后的网表进行编辑过程2017-11-18 7540

-

在Vivado下利用Tcl实现IP的高效管理2017-11-18 5815

-

网站总被攻击?写个自动封禁IP的脚本给你2023-01-29 1119

-

封ip脚本进化的解决办法2023-06-11 686

-

IP 地址在XSS中的利用与防范2024-08-07 257

-

高效管理代理IP,关键操作步骤与技巧来了!2024-09-14 242

-

云计算环境下的IP地址分配方式2024-12-19 130

全部0条评论

快来发表一下你的评论吧 !