高算力集成系统封装,开始押宝!

电子说

描述

来源:晶上世界

近日,三星电子宣布其先进封装(AVP)部门正潜心研发一项革命性技术——3.3D封装,该技术整合了三星电子多项先进异构集成技术,能够以更低成本替代昂贵的“硅中介层”,并预计于2026年第二季度量产。这一新技术概念的披露,预示着先进封装技术领域的市场竞争格局可能迎来新的变革。

高算力集成封装技术智能时代战略高地

在万物智联的新时代,国家间的竞争愈发聚焦于算力这一核心资源。算力不仅是支撑国家发展的坚实基石,更是衡量一个国家综合实力与竞争力的关键指标。简而言之,“算力即国力”已成为新时代的战略命题。

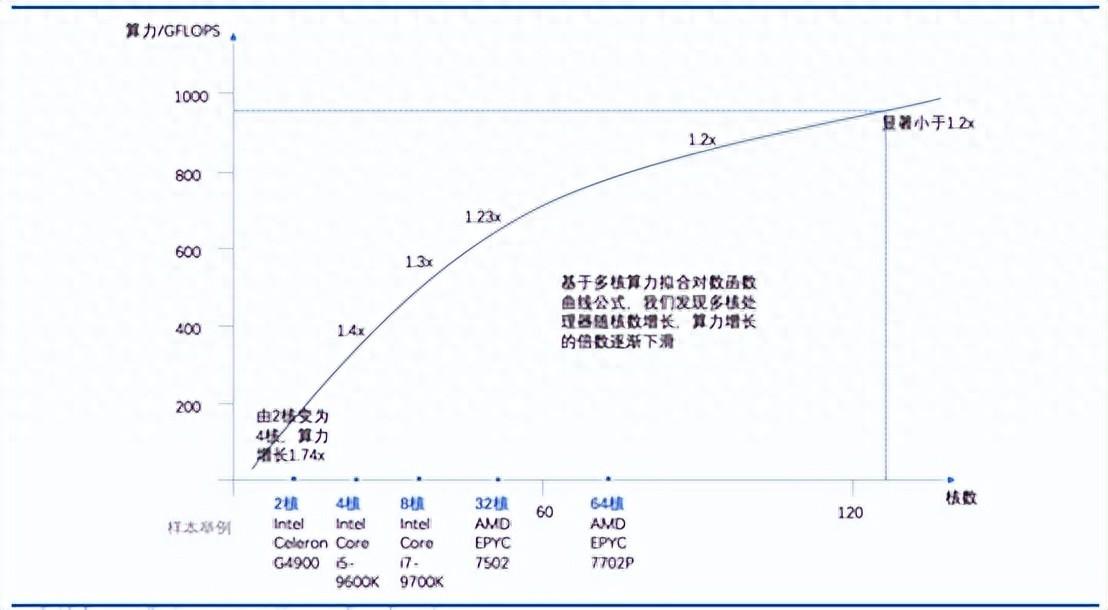

图1 Intel芯片算力发展趋势

(图源:华为、罗兰贝格、国盛证券研究所)

面对日益增长的算力需求,传统技术路线渐露疲态,系统层级的集成度提升成为破局的关键。正如建筑师追求建筑的高度与美感,科技界也在不断探索如何将更多的计算单元巧妙地融入方寸之间,以实现算力的飞跃式提升。

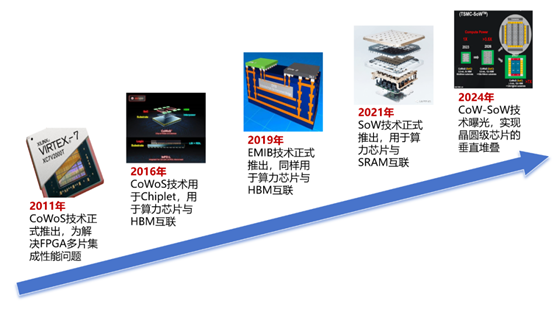

晶上系统(System on Wafer,SoW)作为已知集成算力的最高形式,凭借前所未有的集成密度和卓越性能,成为了大算力领域的领航者。封装技术作为实现高算力集成系统的重要技术,在追求算力最大化的征途上,并未陷入同质化竞争的泥潭,而是在系统性能与成本双轮驱动下,不断涌现出创新成果。

图2:先进封装技术的迭代

美国对封装技术的认知升级与布局深化

美国作为芯片科技的引领者,其对先进封装技术的认知与理解正随着算力时代的浪潮不断演进与深化。

在美国与欧洲、日本、韩国、中国台湾联合发布的国际半导体技术发展路线图(ITRS)2021年版本的内容中,围绕封装技术的发展指明了封装互联技术、封装电威廉希尔官方网站 、封装热威廉希尔官方网站 、可靠性与安全技术、可制造性以及材料技术六大发展方向,虽已展现出对封装技术多维度的重视,但发展重点主要聚焦于技术本身。

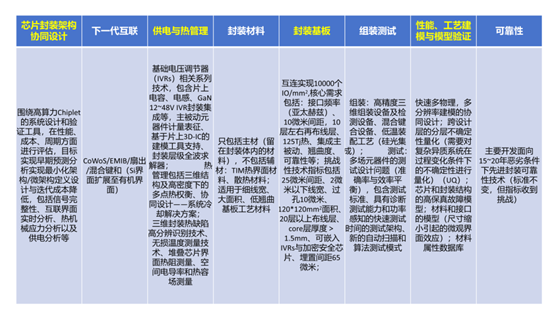

两年后,这一认识边界已被大幅拓展。2023年10月,美国半导体工业协会(SIA)联合半导体研究联盟(SRC)发布《微电子和先进封装技术(MAPT)路线图》,深化了对传统封装技术领域的理解,重新定义了先进封装技术的发展方向,开创性地引入了芯片封装架构协同设计、供电与散热管理、封装基板和性能、工艺建模与模型验证四大技术方向,标志着先进封装正式成为对高算力集成起关键重要性作用的环节,其定制化、差异化属性将伴随后续高算力芯片的全生命周期。

图3 MAPT中先进封装技术的布局方向

封锁挑战下的中国封装技术破局策略

近十年来,美国在微电子领域竭力维持技术霸权,不断升级对我国的技术封锁,以保持压倒性优势。为此,我国积极寻求在封装技术领域的突破,以期在芯片工艺制程暂时落后的背景下,开辟出一条自主创新的道路。随着Chiplet技术的崛起,我国紧跟技术发展潮流,在此基础上深化技术布局,力图通过封装技术的革新,弥补制程上的不足,加速高算力集成系统的国产化进程。

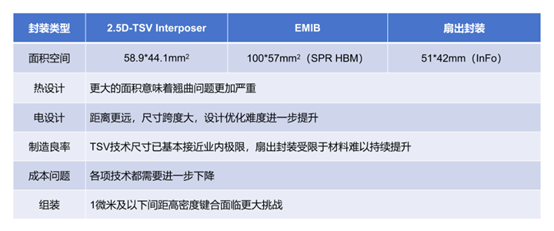

诚然,Chiplet与先进封装技术的融合,为我国技术升级提供了宝贵的助力,但是落后的制程意味着我们需要将更大面积的芯片集成于转接板上,随之而来的则是封装难度的升级,包括热管理、电气设计、良率提升及成本控制在内的多重挑战接踵而至。

图4 国内高集成封装技术面临的技术挑战

因此,Chiplet+先进封装技术仅可作为我国工艺受限情况下的重要战略“保底方案”。我们还需构建一套中国特色的晶上集成系统解决方案,精准击破高算力芯片封装集成技术领域的“瓶颈”,实现从技术依赖到技术引领的跨越。

为此,我们应将布局的重点聚焦于以下方向:

- 深化高算力芯粒异构集成芯片封装技术的研究与应用:通过优化芯粒间的互连与协同工作,提升整体系统的算力与效率;

- 构建多物理场耦合仿真验证平台:开发热学、应力分析、信号完整性(SI)、电源完整性(PI)及多物理场联合仿真等综合仿真工具链,全面模拟封装过程中的复杂物理交互,确保封装设计的精准性与可靠性;

- 积极探索基于有机介质的晶上系统(SoW)封装技术:利用有机材料的独特性质,提升封装的灵活性与可靠性。

【近期会议】

10月30-31日,由宽禁带半导体国家工程研究中心主办的“化合物半导体先进技术及应用大会”将首次与大家在江苏·常州相见,邀您齐聚常州新城希尔顿酒店,解耦产业链市场布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二届半导体先进封测产业技术创新大会”将再次与各位相见于厦门,秉承“延续去年,创新今年”的思想,仍将由云天半导体与厦门大学联合主办,雅时国际商讯承办,邀您齐聚厦门·海沧融信华邑酒店共探行业发展!诚邀您报名参会:https://w.lwc.cn/s/n6FFne

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:viviz@actintl.com.hk, 电话:0755-25988573

审核编辑 黄宇

全部0条评论

快来发表一下你的评论吧 !