数字威廉希尔官方网站 电平标准与接口设计解析

电子说

描述

输入:VIH>3.5V,VIL<1.5V。

可以看出TTL电平的噪声容限为0.4V,CMOS的噪声容限为1.5V。

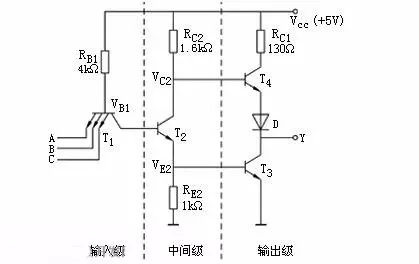

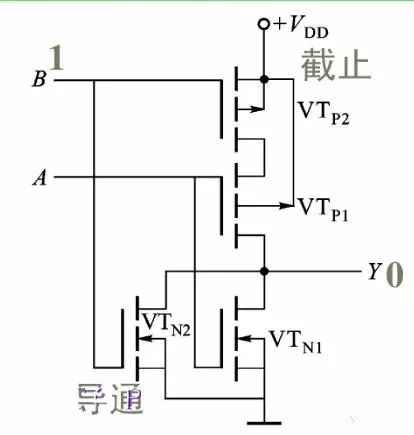

TTL和CMOS门威廉希尔官方网站 结构:

如图TTL门结构,输出级采用推挽式输出结构,T4为射极跟随的形式,输出电阻小,带负载能力强。

如图CMOS门结构。

3.3V LVCMOS: Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。 2.5V LVCMOS: Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。

二、高速电平标准

在高速威廉希尔官方网站 中如何实现高速驱动输出呢?要么增大驱动电流,要么降低电平标准,或者提高晶体管工作速度。显然前者会带来非常大的功耗,因此改变电平标准和改进晶体管设计成为选择,虽然低电平更容易受到干扰,所以需要更严格的硬件设计。

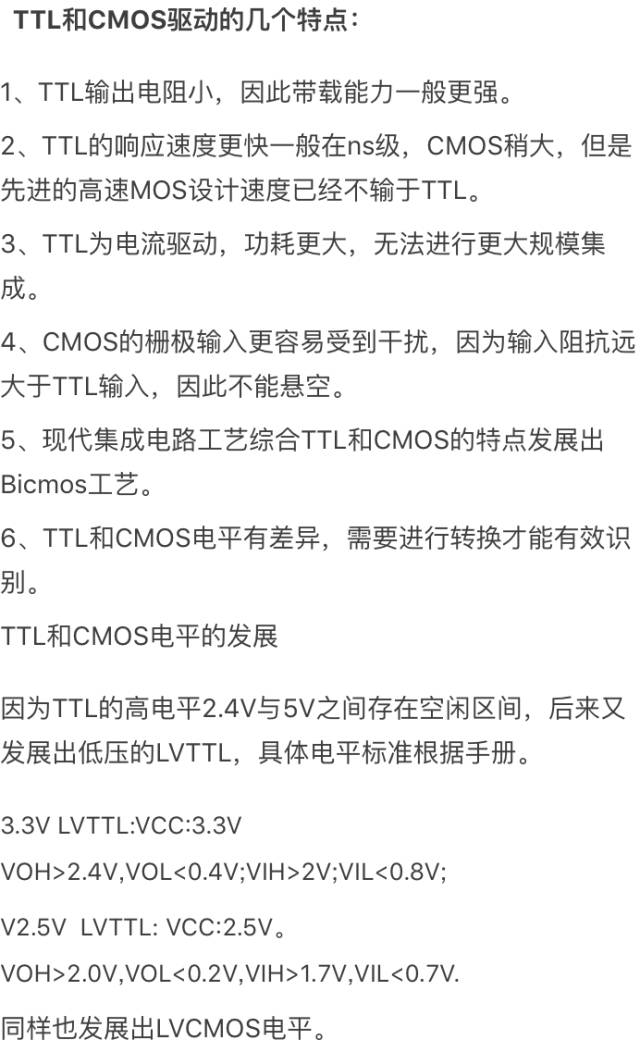

1、ECL和PECL电平接口

ECL即射极耦合逻辑(Emitter Coupled Logic)采用的是差分结构输出,并需要负电源供电。后来发展处PECL,即正电源射极耦合逻辑。基本原理就是利用晶体管工作在非饱和区来减小转换时间,大大提高转换速度。

ECL的输出管始终有电流通过,非常有利于高速转换。输出阻抗几欧姆,输出电流10mA左右,驱动能力强。

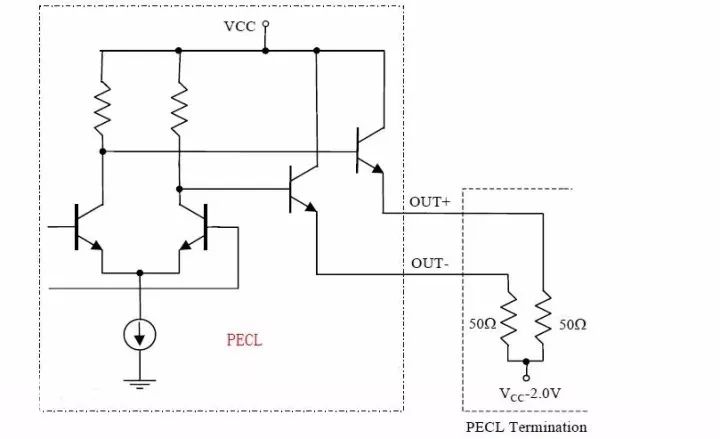

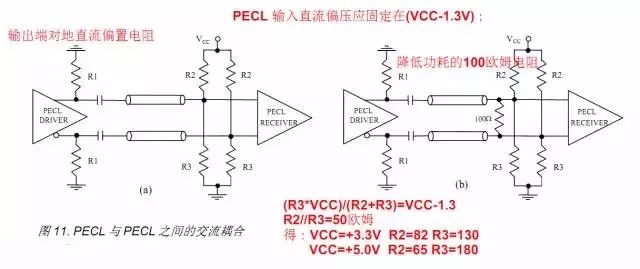

接口连接:直流耦合,适用于短距离

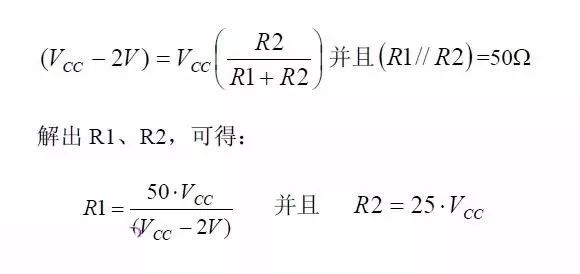

这个匹配方式由等效而来,具体阻值计算:

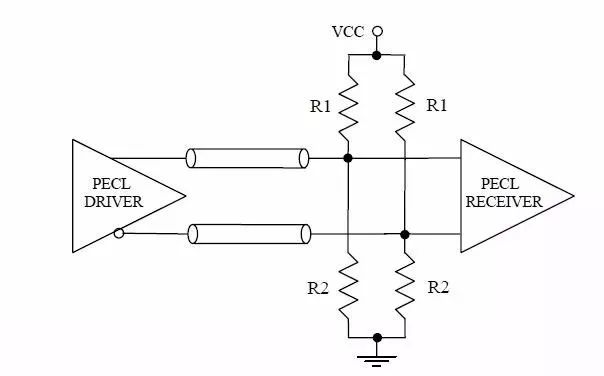

接口连接:交流耦合,适用于较远距离

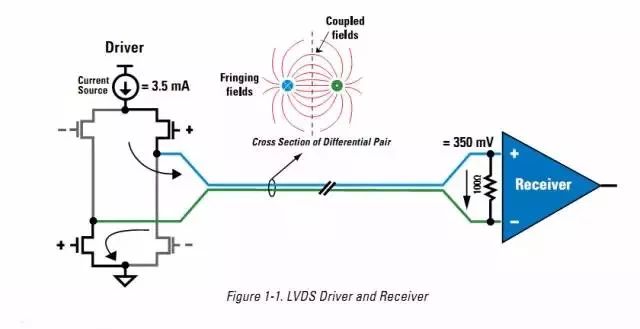

2、LVDS电平接口

LVDS即Low-Voltage Differential Signaling,是一种利用低压差分信号传输高速信号的电平标准。特点是:低压,低功耗,噪声抑制能力强。

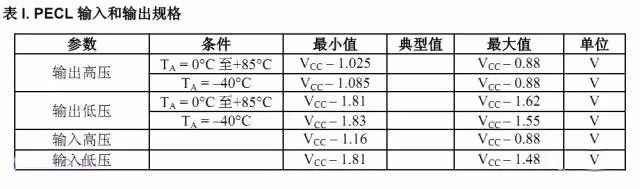

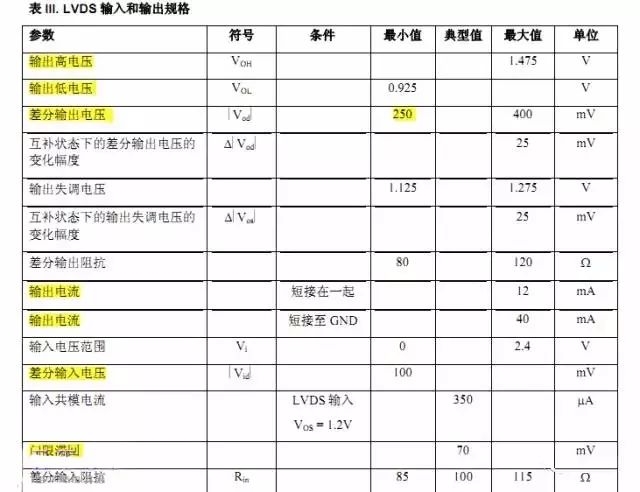

如图LVDS的输入和输出规格:

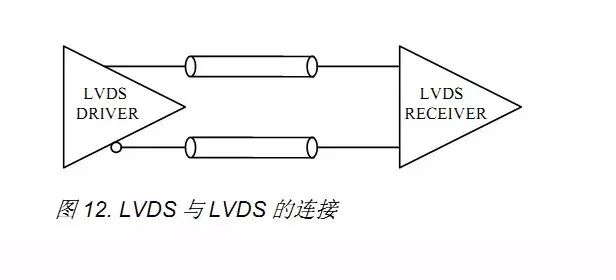

LVDS的连接方式:直接连接,因为片内具有端接电阻。

三、CML电平接口

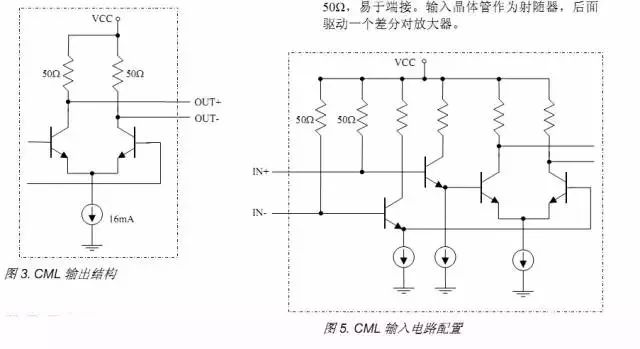

CML即电流模式逻辑电平,采用恒流驱动,内置匹配电阻,使用简单,短距离高速应用中最多。

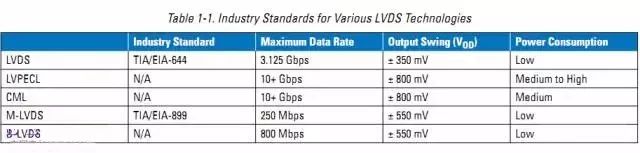

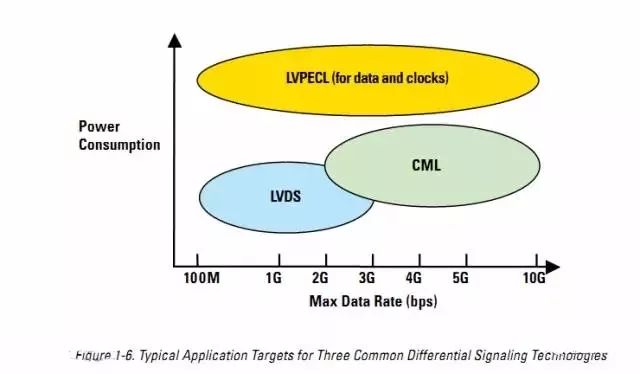

下图是几种高速接口的性能简单比较:

三、常用普通电平标准

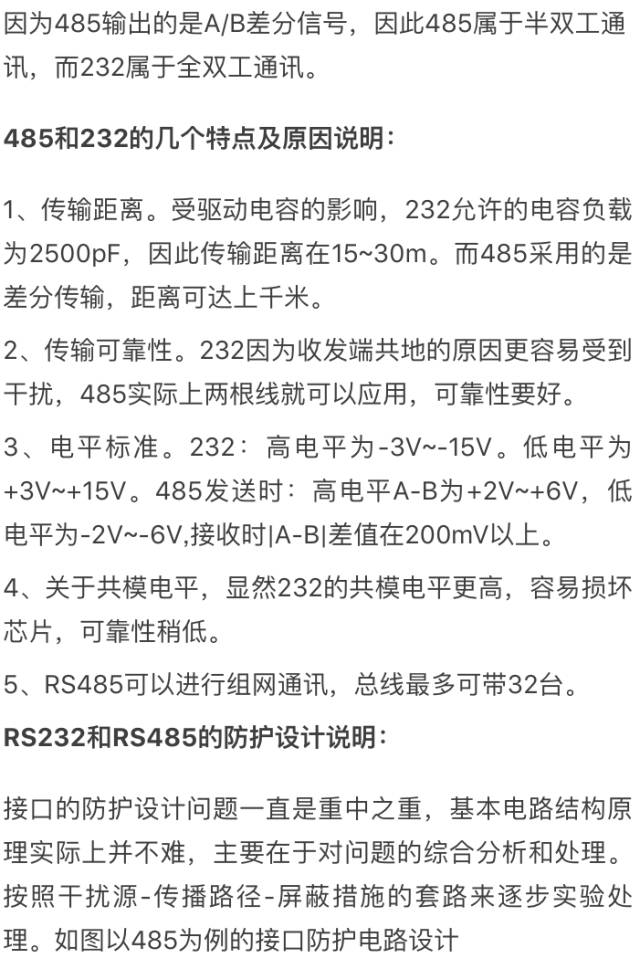

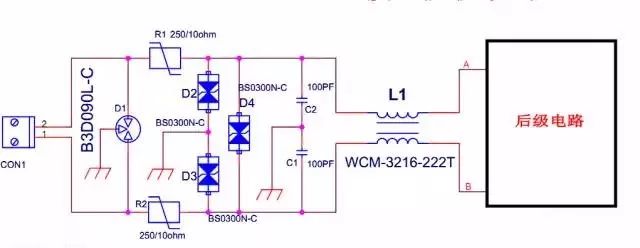

在工业领域应用最多的应该是485 232的电平标准,两者各有优缺点,成本低,使用也比较简单,但是依然有很多技术要点可以讨论,譬如传输速度,距离,防护设计等等。

RS232和RS485的连接问题:

工作中了解到不少同学对于232或者485的连接一直有些迷糊,关于信号的收发端定义及公母头连接,一开始我也是经常摸不着头脑。以收发地三线为主。

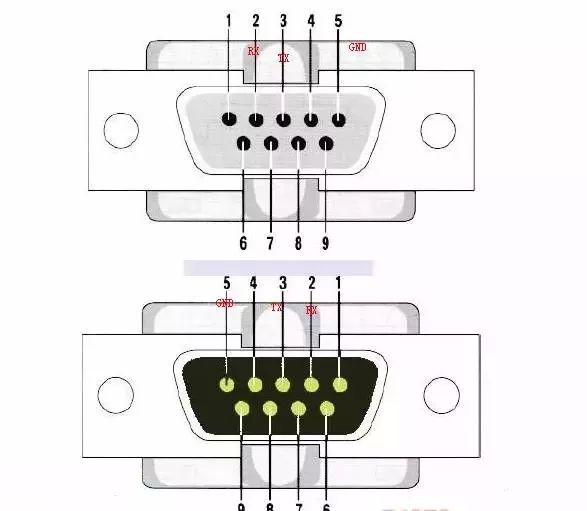

标准的232是DB9接头:

简记为:235-收发地。

485如何利用DB9连接:

485的两根线对应DB9头的1,2脚。

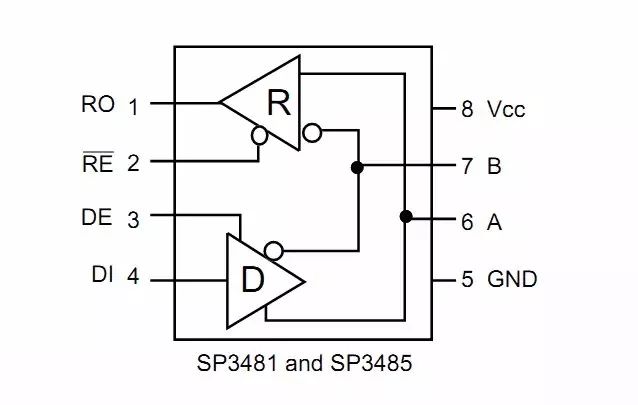

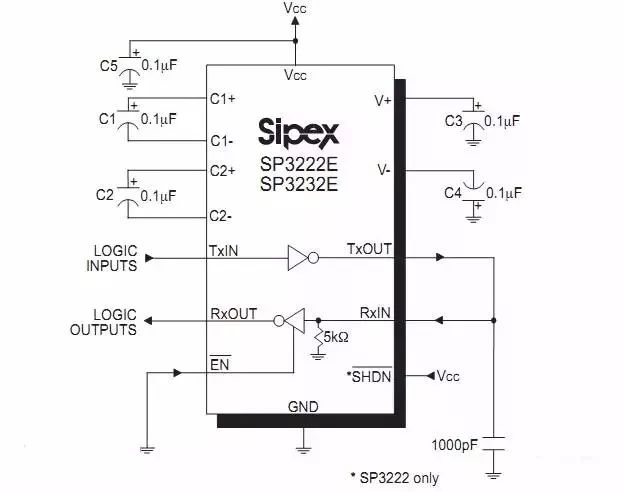

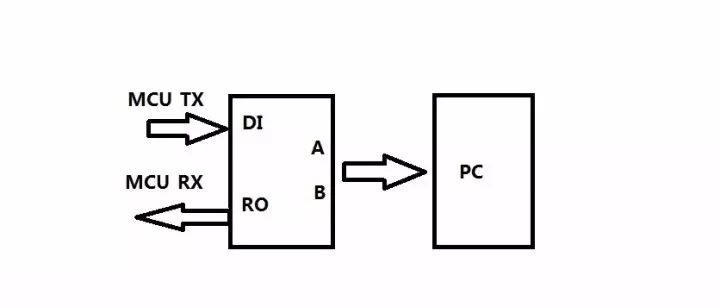

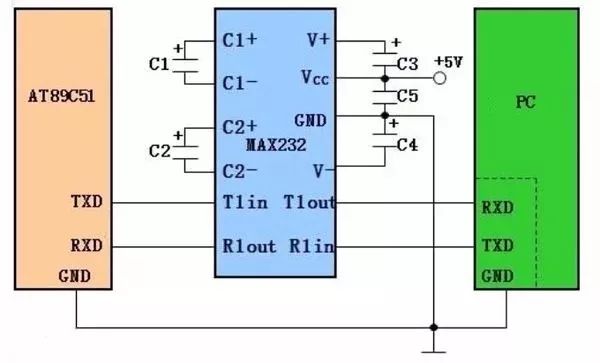

232和485与MCU的连接:

四、小结

关于数字电平的标准主要就这么几种,这些都是在硬件层面的定义,在软件上对应的就有各种协议通讯方式的规定。关于接口设计确实是威廉希尔官方网站 设计中的重点,尤其是在目前的高速数字通讯应用当中,我觉得主要有几个要掌握的方面:

1、信号电平的应用威廉希尔官方网站 ,也就是基本结构要清晰。

2、防护设计问题要考虑周全,不同接口对于负载对于匹配度的要求都不一样。

3、PCB设计的重要性,在高速设计中很多都采用EDA软件仿真的方式来协助查找关于干扰的问题,但是首要的还是要严格遵循相关规则和规范来设计。

4、实验的必要性。尤其是接口的干扰问题,尽可能全面的实验方案设计是尽快解决问题的最佳路径之一。

总之,理论基础要有,设计考虑要到,测试实验要全,如此,结果可能才好!

-

数字威廉希尔官方网站 和模拟威廉希尔官方网站 的隔离探讨2013-04-19 0

-

数字威廉希尔官方网站 为什么是低电平有效的多2016-10-03 0

-

电平特性数字威廉希尔官方网站 中有哪几种电平2021-07-21 0

-

数字威廉希尔官方网站 设计2009-08-26 2833

-

数字威廉希尔官方网站 图符号解析2011-07-23 13970

-

数字威廉希尔官方网站 比模拟威廉希尔官方网站 的优点2019-05-16 18425

-

模拟威廉希尔官方网站 和数字威廉希尔官方网站 的区别2019-07-30 33292

-

数字威廉希尔官方网站 中尖峰电流的形成原理解析2019-11-06 9359

-

数字威廉希尔官方网站 和模拟威廉希尔官方网站 怎么区分2020-08-30 21598

-

数字威廉希尔官方网站 电平标准全解析2020-11-29 4842

-

数字威廉希尔官方网站 的电平标准与接口设计的详细资料概述2021-01-08 492

-

数字威廉希尔官方网站 中最基本的门威廉希尔官方网站2022-09-16 3609

-

数字威廉希尔官方网站 和模拟威廉希尔官方网站 的区别2023-02-13 13080

-

图解数字威廉希尔官方网站 基础2023-06-19 1787

-

数字威廉希尔官方网站 是什么2023-11-06 2329

全部0条评论

快来发表一下你的评论吧 !