混合键合,成为“芯”宠

电子说

描述

来源:半导体行业观察 ,作者杜芹DQ

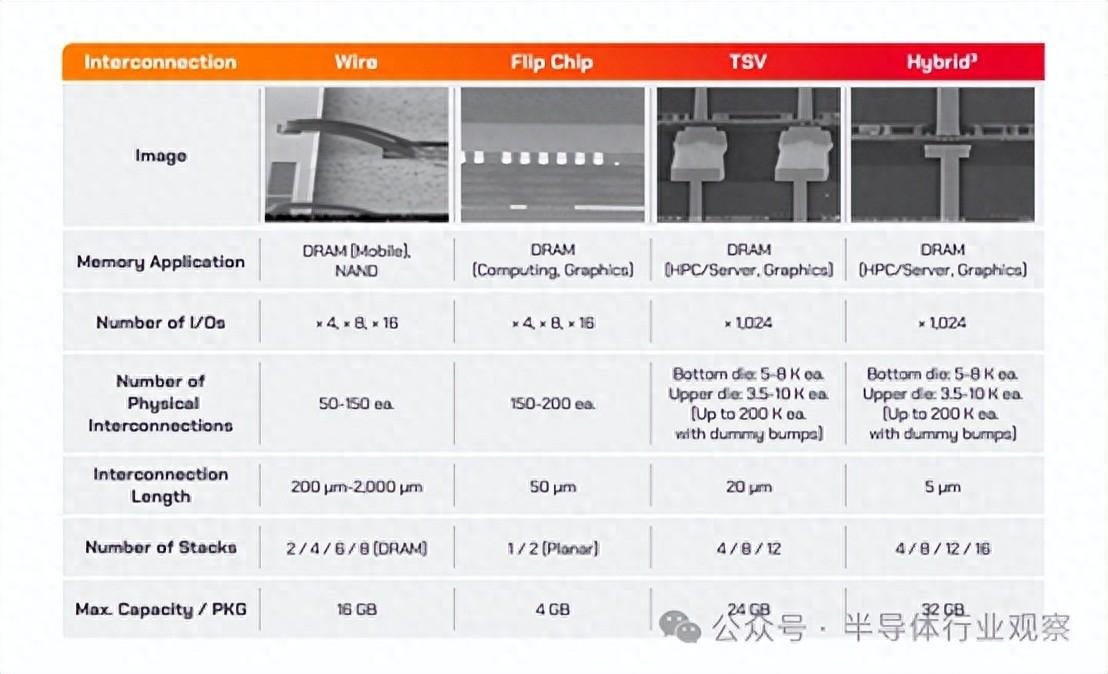

随着摩尔定律逐渐进入其发展轨迹的后半段,芯片产业越来越依赖先进的封装技术来推动性能的飞跃。在封装技术由平面走向更高维度的2.5D和3D时,互联技术成为关键中的关键。面对3D封装日益增长的复杂性和性能要求,传统互联技术如引线键合、倒装芯片键合和硅通孔(TSV)键合等,正逐步显露其局限。在这种背景下,混合键合技术以其革命性的互联潜力,正成为行业的新宠。

四大主要的互联技术

(图源:SK海力士)

混合键合,或称为Hybrid Bonding,主要有两种使用方式。第一种是晶圆到晶圆,用于CIS 和NAND,在这些领域,混合键合已经证明了其效率。铜混合键合最早出现在2016年,当时索尼将这项技术用于CMOS图像传感器;另一种是裸片到晶圆混合键合,这比晶圆间键合更加困难,但这种工艺变化对于逻辑和高带宽内存 (HBM) 很有意义。

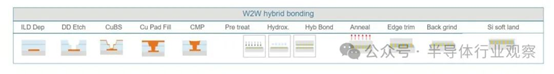

晶圆对晶圆(Wafer-to-Wafer,W2W)混合键合的步骤流程(来源:应用材料)

裸片对晶圆(Die-to-Wafer,D2W)混合键合的步骤流程(来源:应用材料)

混合键合技术具有以下特点:1)它允许不同的芯片层,如存储器层和逻辑层,在无需通过硅通孔(TSV)的情况下直接互连,显著提高信号传输速度并降低功耗;2)通过芯片和晶圆之间的直接铜对铜键合,最大限度地缩短导线长度;3)与传统TSV技术相比,混合键合减少了层间物理连接的需求,使芯片设计更紧凑,有利于实现更高性能和密度。据悉,在应用混合键合时,1平方毫米的面积内可连接10,000至100,000个通孔;4)混合键合还可减少芯片内部的机械应力,提高产品的整体可靠性,同时支持更高的数据传输速度和更低的能耗。

混合键合已成为芯片盖楼、未来3D封装的一项关键技术,是实现高性能、高密度和低功耗芯片设计的关键技术之一。在这样的背景下,晶圆厂、存储厂、设备厂,都盯上了混合键合。

混合键合的先行者们

混合键合技术已成为晶圆制造业的共识,行业巨头如台积电、三星和英特尔正在竞相推进5纳米及更先进制程技术的开发。在这一进程中,混合键合技术显得尤为关键,被视为高端制造的必由之路。

台积电:唯一实现混合键合商业化的公司

在混合键合领域,全球排名第一的晶圆代工公司台积电最有发言权。台积电是迄今为止唯一一家将混合键合商业化的芯片公司。台积电的3D封装-SoIC就是使用的混合键合技术,该服务名为3DFabric,已应用于AMD V-Cache。

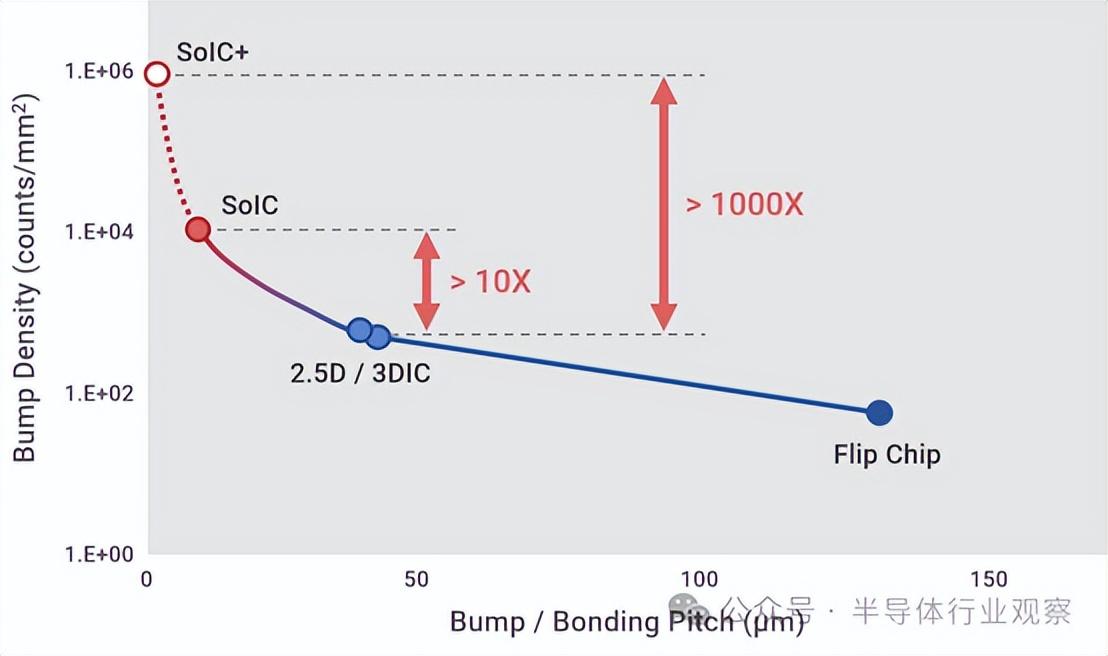

据台积电的公开资料显示,凭借创新的键合方案,SoIC技术为芯片 I/O 提供了强大的键合间距可扩展性,从而实现了高密度芯片间互连。键距从低于10 µm的规则开始。与当前业界最先进的封装解决方案相比,短芯片到芯片连接具有更小的外形尺寸、更高的带宽、更好的电源完整性 (PI)、信号完整性 (SI) 和更低的功耗。

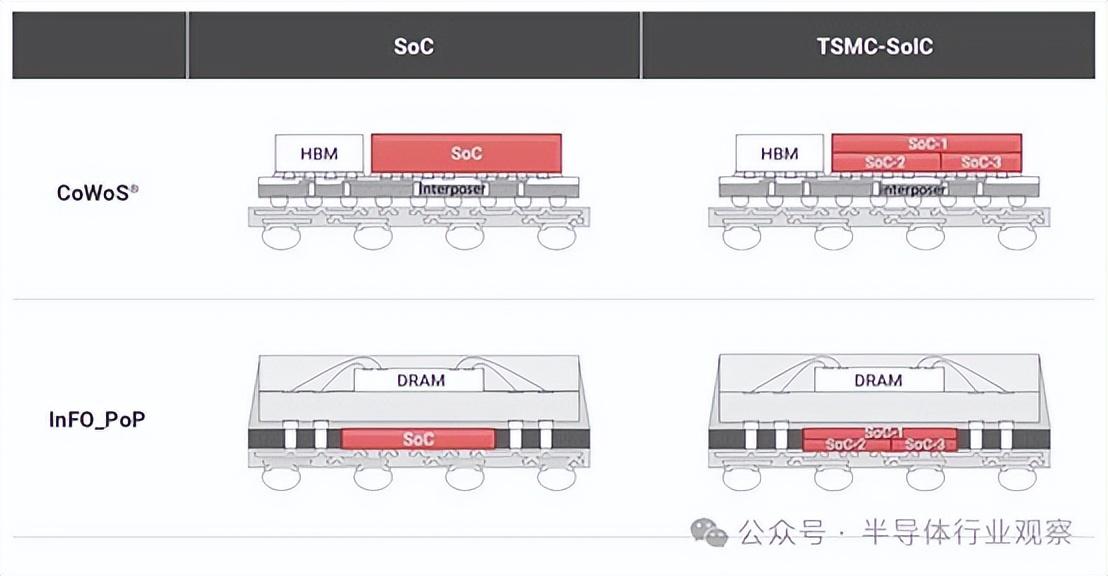

台积电展示的SoC-Exceptional-scalability

(来源:台积电)

台积电的SoIC技术将同构和异构小芯片集成到单个类似 SoC 的芯片中,该芯片具有更小的占地面积和更薄的外形,可以整体集成到先进的 WLSI(又名 CoWoS 服务和 InFO)中。从外观上看,新集成的芯片就像通用的SoC芯片一样,但嵌入了所需的异构集成功能。

SoIC与SoC的外观对比

(来源:台积电)

三星:积极引入混合键合

三星电子正开始认真引入混合键合,三星“一条腿”是为了增强其代工能力,另一条腿是在HBM上发力。

据业界2月1日消息,Besi Semiconductor和应用材料正在三星电子天安园区安装混合键合相关设备。天安园区是三星电子的先进封装生产基地。该设备预计将用于 X-Cube 和 SAINT 等下一代封装解决方案。据业内人士透露:“据我所知,该设备用于非内存封装。”

据了解,三星电子的最新投资主要是为了加强其先进封装能力。三星电子正准备推出采用混合键合的 X-Cube。业界预测,混合键合也可以应用于三星电子计划从今年开始推出的Saint平台。该公司计划提供3D封装服务,例如Saint-S(将SRAM堆叠在逻辑芯片上)、Saint-L(将逻辑芯片堆叠在逻辑芯片上)以及Saint-D(将DRAM芯片堆叠在逻辑芯片上)。

业界预测,三星电子对混合键合设施的投资可能会赢得英伟达和AMD等大客户的青睐。这是因为这些无晶圆厂客户的AI芯片中所用的CoWoS封装对混合键合的需求正在增加。

另一方面,据三星电子执行副总裁兼 DRAM 产品与技术团队负责人 SangJoon Hwang 在三星博客上发表的社论博客文章,三星的HBM4 将于 2025 年推出。HBM4内存将采用一些针对高热性能进行优化的技术,例如非导电膜(NCF)组装和混合铜键合(HCB)。

英特尔:混合键合呼之欲出

在晶体管诞生75周年的2022年IEDM会议上,英特尔就展示了其采用混合键合技术,致力于将封装技术密度提升10倍的雄心。英特尔计划将这一技术应用于其3D封装技术Foveros Direct,该技术已在去年实现了商业化推广。

在今年的ECTC上,英特尔发表了一篇有关混合键合技术的论文。图左侧的技术称为 Foveros,凸块间距为50微米,每平方毫米大约有400个凸块。未来,英特尔的目标是将凸块间距缩小至约10微米,并实现每平方毫米10,000个凸块。

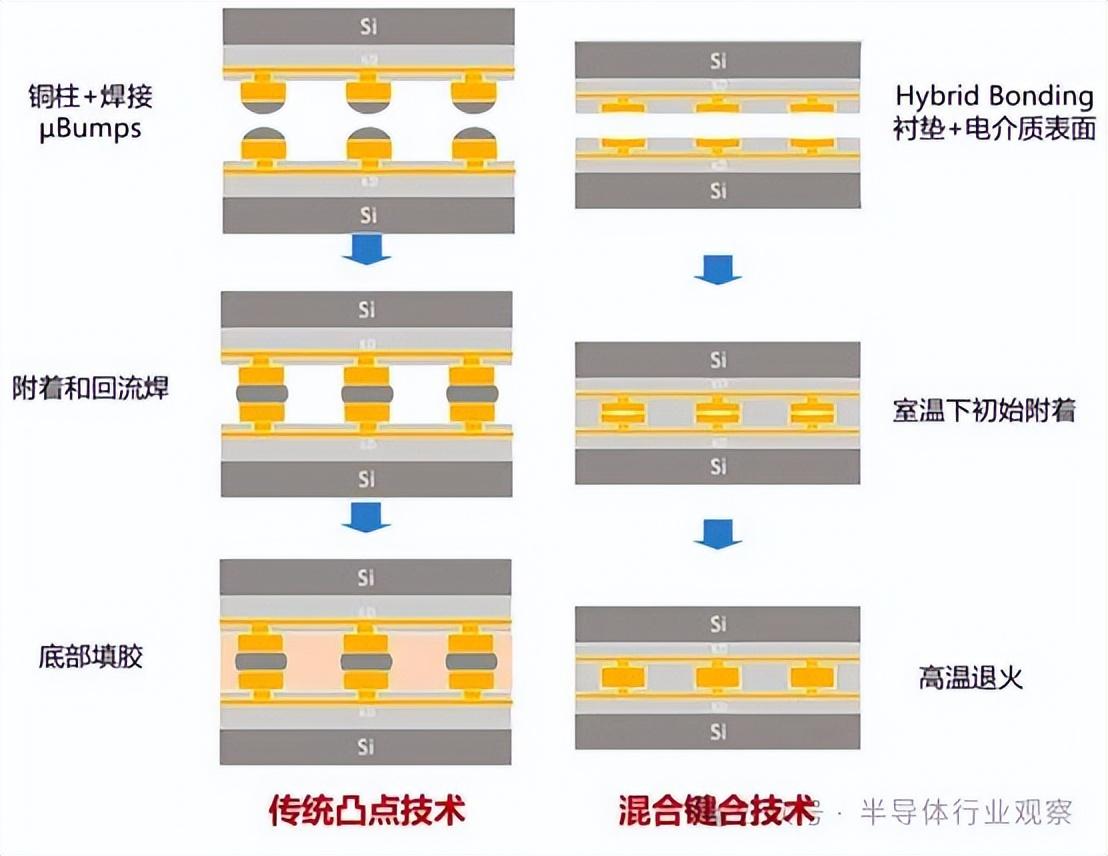

下图比较了传统凸点接合技术与混合接合技术。与底部填充相比,混合键合技术可将互连间距减小至10微米以下,从而实现更高的载流能力、更密集的铜互连密度以及更好的热性能。但是,混合键合技术需要新的制造、处理、清洁和测试方法。

据报道,英特尔有望在2024年率先在其逻辑芯片与互连器之间采用混合键合技术。Foveros Direct预计将采用晶粒对晶圆的混合键合方法,其间距预计在9至10微米之间。相比之下,英特尔的Meteor Lake产品采用热压缩键合(TCB)技术的间距为36微米,而Lakefield产品采用通过硅孔(TSV)的凸块连接技术的间距为55微米。

SK海力士:HBM率先引入混合键合

存储厂商SK海力士也盯上了混合键合。

去年,SK海力士凭借在高带宽存储器(HBM)芯片的领先,成为这一轮AI热潮的重度获利者。但你可能不知道的是,SK海力士在封装技术也有很闻名。例如,SK海力士所开发的CoC(片上芯片)封装技术,能将两个(或更多)芯片电连接在一起,无需 TSV(硅通孔);K海力士还开发了异构集成和扇出RDL技术等先进封装技术。去年,SK海力士正是由于率先在第五代HBM的生产中引入了大规模回流成型底部填充 (MR-MUF) 工艺,从而保持了HBM行业领导者的地位。

SK海力士的MR-MUF技术提高了HBM超过100,000个微凸块互连的质量。此外,该封装技术充分增加了热虚拟凸块的数量,同时由于采用了高导热率的模制底部填充(MUF)材料,因此与竞争对手相比,散热性能更加出色。这一进步帮助SK海力士增加了其在HBM市场的份额,并最终在HBM3领域占据了领先地位。

如今SK海力士正在HBM芯片中积极推进“混合键合”新工艺,以维持其在全球市场的领先地位。那么,为什么HBM要采用混合键合技术呢?

首先让我们再来熟悉下HBM芯片,所谓的HBM,其实就是通过堆叠DRAM层数来提高数据处理速度的存储器。其主要通过TSV+填充物的方式来连接DRAM层。据SK海力士称,HBM芯片目前的标准厚度为720微米(µm)。“当HBM的层数达到12层甚至更多时,可能会出现高度方面的问题,这就需要运用混合键合技术来解决”SK海力士的晶圆键合负责人Kang Ji-ho曾在一次会议上表示。SK海力士预计,2026年左右投入量产的的第六代HBM(即HBM4),其层数要求可高达16层,这对现有封装技术提出了巨大的挑战。

混合键合技术是HBM领域的未来发展趋势。简单来说,如果把HBM想象成一座多层大楼,其中每一层都承载着存储数据的任务,当大楼层数过多时,仅靠传统的通过硅通孔(TSV)+填充物的连接方式不足以维持其稳定且可靠。而混合键合技术就好比在每一层之间涂上了一种特殊的“胶水”,这样就不需要额外的支撑物来固定这些层了,能显著减小芯片的厚度。

简而言之,通过混合键合技术,他们能够制造出既高效又小巧的高层内存芯片。混合键合也被称为是“梦想封装技术”。

SK海力士率先宣布在今年将混合键合应用于HBM4产品,继续引领HBM技术发展,这将为HBM4产品的性能和功耗带来革命性的提升。

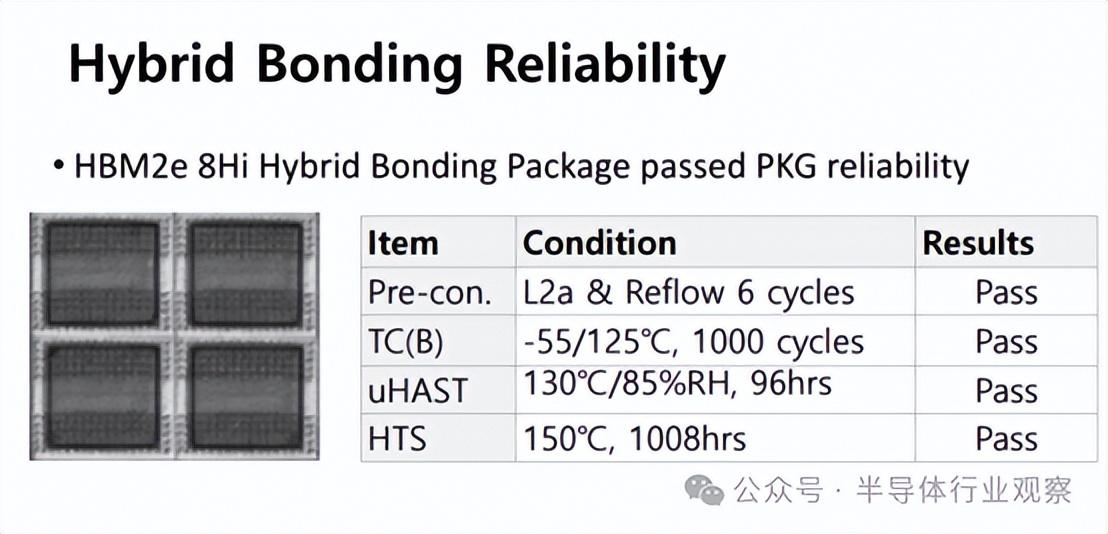

目前,SK海力士取得了一定的进展。就在去年12月份在美国举行的全球半导体会议IEDM 2023上,SK海力士透露了其已确保HBM制造中使用的混合键合工艺的可靠性。该公司报告称,其第三代HBM产品(HBM2E)采用了8层堆叠DRAM,并且在采用混合键合工艺后顺利通过了所有可靠性测试。在这次测试中,SK海力士对HBM在高温环境下的使用寿命进行了评估,并检查了产品在客户焊接芯片过程中可能出现的潜在问题,涵盖了四个主要方面。虽然本次测试是在第三代产品上进行的,其要求远低于HBM4规格,但这也展示出了混合键合的潜力。

使用SK海力士混合键合的HBM2E可靠性测试结果

据报道,SK海力士预计将在2025至2026年间实现其混合键合技术的商业化。最新的韩国媒体消息指出,SK海力士近期与台积电共同发起了名为“One Team Strategy”的联盟,两家将共同研发第六代HBM(高带宽存储器)芯片,即HBM4。在这一合作中,台积电预计将承担HBM4芯片部分工艺的制造任务,特别可能包括关键的封装工艺,以增强产品的兼容性和性能。对此,SK海力士方面表示:“对于联盟的具体情况,公司不予置评。”

设备厂商,混合键合的“卖铲人”

混合键合技术,不是易事。其面临的主要技术挑战是:以经济成本实现无缺陷的铜对铜接合,并且芯片对芯片的对准误差几乎为零。这需要对上下游工艺以及设备设计进行重大修改。在此过程中,集成流程开发和协同优化在这里发挥着关键作用。

在执行芯片或晶圆间的混合键合时,必须保证它们的表面达到接近原子层级的极致清洁度,并进行至关重要的步骤——精确地对齐并键合二氧化硅绝缘层与铜接触点。这一过程需要极度洁净和高精度的键合设备。首先,需要利用清洁和等离子体激活设备为键合做好充分准备。紧接着,在第二阶段,使用键合机器精确地将集成威廉希尔官方网站 放置到晶圆上。考虑到这些设备的高端精密性要求,它们的成本相对较高,与前端制造设备的价格不相上下。根据Besi的报价,每台键合设备的成本在200万至250万欧元之间。

在混合键合领域,主要的设备供应商包括应用材料公司(Applied Materials)、KLA Tencor、Lam Research、ASM Pacific Technology(ASMPT)和BE Semiconductor Industries(BESI)。正如淘金时代的铲子、筛网对淘金者至关重要一样,混合键合设备是芯片制造商实现技术突破的基础工具。它们的设备精度、可靠性和创新程度直接关系到芯片制造商是否能在激烈的市场竞争中胜出。

由于与英特尔和台积电的长期合作关系,荷兰后端专家Besi目前在芯片对晶圆混合键合领域处于有利地位。据其首席执行官布里克曼表示,八年前台积电要求Besi公司开始为其技术开发键合机。“台积电在整个学习曲线过程中帮助了我们,”他在去年接受New Street Research公司Pierre Ferragu采访时说。“我们处于一个独特的情况,拥有正确的客户。从一开始我们就一直在选择赢家。与应用材料的合作在理解洁净室环境的要求方面极为有帮助。”

Besi和应用材料在混合键合领域有着密切的合作。自2020年10月以来,Besi和 Applied 公司通过在新加坡建立卓越中心 (CoE) 来进行技术开发。纵观两家公司的混合键合产品组合,Besi主要是批量生产混合键合芯片贴装设备,而Applied则生产从电介质沉积设备到等离子体设备和化学机械抛光(CMP)设备等各种设备。应用材料公司的Insepra SiCN和 Catalyst CMP系统可实现与新材料的最先进的混合键合并增强表面处理。如前文所述的三星的产线也是Besi和应用材料共同作用的结果。据Besi透露,建设一条清洁和键合生产线的总成本约为500万到600万欧元。应用材料公司和Besi各自占据其中的一半,具体取决于应用领域——存储器或逻辑芯片。

2021年,在COVID危机期间的半导体热潮中,Besi宣布,英特尔和台积电都承诺购买50台混合键合机。订单真正开始增长是在2023年,所以这些计划似乎有些延迟,但Besi表示它已经有能力每年生产180台混合键合机。如果这个产能得到充分利用,将意味着额外的4亿欧元销售额。

奥地利的EV Group多年来提供了一种用于清洁芯片和晶圆并为放置系统做准备的等离子体激活系统。EVG与ASM Pacific合作,后者提供键合机。EVG已经在混合晶圆对晶圆键合市场上证明了自己,在这个市场上领先,拥有数百台机器。几乎所有手机中的传感器都经过了EVG设备的晶圆对晶圆过程。在高端CMOS传感器市场,EVG正在与日本的TEL竞争。

混合键合,已成为芯片发展的重要趋势。目前的首要任务是,行业需要共同努力,推动芯片到晶圆混合键合技术的大规模生产。随着越来越多的企业投身于这一创新领域,我们有理由相信混合键合技术将在不久的将来迎来突破性的发展。

展望未来,随着高速通信需求的不断增长,铜互连将无法满足传输需求,光互连技术将成为未来发展的一大选择。

-

混合威廉希尔官方网站 内引线键合可靠性研究2010-05-31 594

-

铜混合键合的发展与应用2023-05-08 1283

-

Chiplet混合键合难题取得新突破2023-06-20 597

-

混合键合的发展趋势和挑战2023-07-15 1780

-

什么是混合键合?为什么要使用混合键合?2023-11-22 4923

-

消息称三星正在整合混合键合技术2024-02-18 709

-

混合键合技术大揭秘:优点、应用与发展一网打尽2024-02-18 2838

-

混合键合技术:开启3D芯片封装新篇章2024-08-26 939

-

混合键合的基本原理和优势2024-10-30 630

-

三维堆叠封装新突破:混合键合技术揭秘!2024-11-13 707

全部0条评论

快来发表一下你的评论吧 !