基于UVM的基带射频接口威廉希尔官方网站 的验证

电子说

描述

随着SoC基带芯片设计规模高度集成化,验证周期将不断增加,占整个研发阶段的70%[1]。为了使基带芯片验证更具高效性,采用了当前主流的UVM验证方法学。UVM验证方法学[2]是由Accellera在2011年正式推出的,创建的验证平台不仅提供很多可用接口,而且多样化的Cadence VIP还为UVM环境搭建提供了必要的组件。因此可以实现高覆盖率的功能验证,使仿真验证时间大幅减小。

基带射频接口威廉希尔官方网站 ,是一种将基带芯片和射频芯片连接起来的数字串行接口。这种数字串行接口不仅节省硬件资源,而且可以通过载波聚合的方式使基带达到较高的上下行空口峰值传输速率。由于复杂的私有化协议接口,必须搭建一种合适的验证平台,快速全面地验证射频接口威廉希尔官方网站 的功能。本文将使用UVM验证方法学对基带射频接口威廉希尔官方网站 模块进行验证,验证方式将全面覆盖射频收发通路的所有功能点。

1UVM验证平台

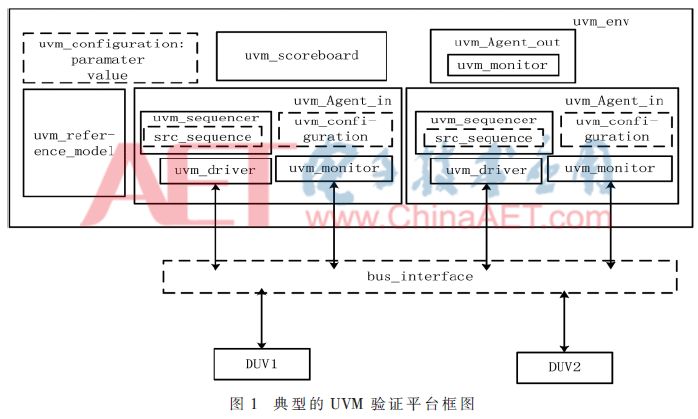

基于UVM特性的验证设计(Design Under Verification),以System Verilog[3]硬件验证语言为基础,通过UVM库[4]调用各类验证组件,使验证工作分工明确。这个UVM库主要包含以下几部分:第一,层次化的验证结构。代理器(Agent)主要集合驱动器等模块;驱动器(Driver)负责将生成的激励按照规则加入到DUT的管脚或者内部;监测器(Monitor)检测DUV 的内部信号以及输出,实现多种监视操作;计分板(Scoreboard)对DUV值和Model预期的值作比较;参考模型(Reference model)使用SystemVerilog建立的和DUT相关的模型,输出期望值。第二,UVM序列器(Sequencer)[5]提供仲裁序列(Sequence)模块,使驱动器得到transaction类型数据包。第三,提供知识产权核(VIP),保证UVM环境中的各个组件快速集成。

典型的UVM验证平台如图1所示。在验证环境中,uvm_env包含了全部的验证组件,两个验证设计通过总线接口跟平台相连。验证平台按照自上而下的结构规范,从env顶层例化了五个模块,两个输入代理器模块,一个输出代理器模块,一个参考模型模块和一个计分板模块。输入代理器模块先对验证环境进行配置,然后通过序列器模块将激励源传送至驱动器模块,驱动器模块将数据通过interface传送至从端接收者,而监测器可以采集驱动器给验证设计的数据信号。输出代理监测器模块实时采样验证设计的输出信号,将采集到的结果放在计分板模块,并跟参考模型模块的输出信息进行比对,减小验证的错误率,降低验证风险。

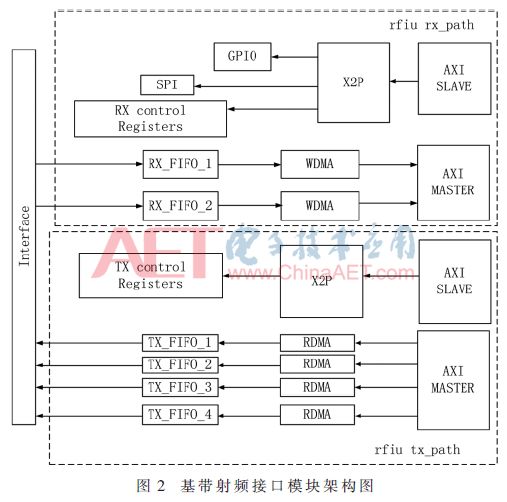

2基带射频接口威廉希尔官方网站 模块

基带射频接口模块包含射频接口的接收通路模块和发送通路模块。基带射频接口模块架构图如图2所示。此射频接口模块采用AXI标准总线协议,通过X2P转接桥将从机地址、数据信号传输至配置模块。其中接收通路的定时使能配置通过GPIO输出,SPI通过配置读写寄存器控制外部射频芯片,接收通路状态是由接收控制寄存器模块配置,在可配置的TBU时间点上打开和关闭射频接收。基带射频接口接收的数据流通过两个FIFO进行缓存,再使用两组DMA将数据流通过AXI主机搬到基带芯片中的存储器。发送通路过程跟接收通路过程互逆,发送状态通过发送控制寄存器进行配置,在可配置的TBU时间点上打开和关闭射频发送,基带芯片主机存储器的数据流通过AXI总线并使用4组DMA缓存至4个FIFO中,最终发送到射频芯片。在射频接口收发过程中,DMA搬数任务完成后发出中断,中断传入ARM处理器,使ARM处理器循环响应,配置多次任务。如果要对FIFO的数据重新缓存,就必须清空FIFO,在可配置的TBU时间点上对寄存器复位,将输出的数据从现在的采样点写到FIFO的起始地址上。

基带射频接口采用多模式多带宽的数据接口支持相应的接口速率,其中CMOS TDD(互补金属氧化物半导体时分双工)模式使用两组12 bit数据线,数据传输采用半双工方式,一个时钟周期可以发送双天线符号数据。在CMOS FDD(互补金属氧化物半导体频分双工)模式下,数据传输速率是CMOS TDD模式数据吞吐率的2倍。而LVDS(低电压差分信号)模式数据传输速率是CMOS TDD模式数据吞吐率的4倍。

1搭建基于UVM的基带射频接口威廉希尔官方网站 验证平台

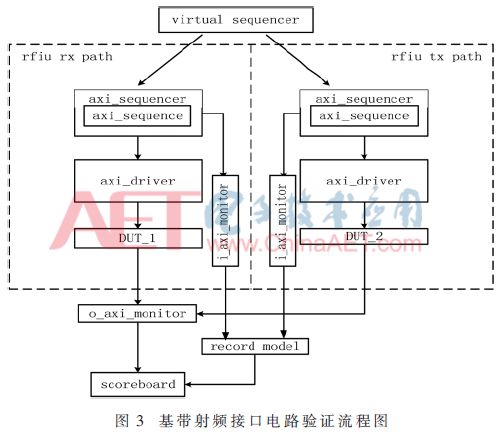

3.1 基带射频接口威廉希尔官方网站 验证流程

基带射频接口采用AXI总线机制分别对基带射频的接收通路模块和发送通路模块进行验证,验证流程如图3所示。在验证环境中将软件接口数据包放置于virtual sequener,通过AXI接口传送给axi _sequencer,驱动器会得到axi_sequence产生的激励信号,这些激励信号分别作用于接收通路的验证设计和发送通路的验证设计。同时例化的两个axi_monitor不仅监视驱动器给射频接收和发送验证设计的数据流,而且可以监测record model,这个record model模型通过MATLAB实现跟射频接口同样的数据传输功能,并把数据信息放入计分板。另一个axi_monitor监测射频接收和发送通路数据信息传送至计分板的情况,一旦record model和监控产生的数据信息都传输到计分板,计分板将会比对两者数据,从而判断仿真是否异常。

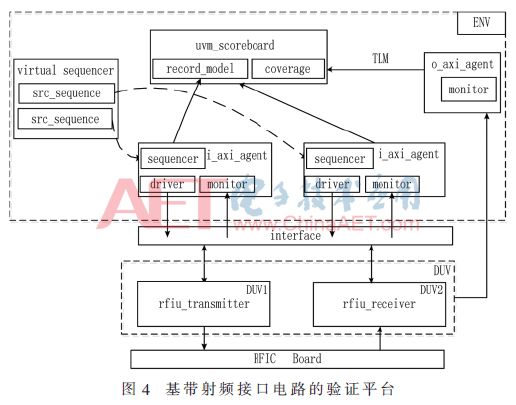

3.2 基于UVM的基带射频接口威廉希尔官方网站 验证平台

基带射频接口威廉希尔官方网站 的验证平台如图4所示。这个待测的验证设计主要是发送模块和接收模块,通过接口将验证对象与验证向量连接起来,而验证向量是为了实现跟待测对象相同的功能。其中验证环境中的Agent是由VIP提供,剩余组件需自行设计。验证环境通过顶层env例化两个i_axi_agent,这两个i_axi_agent包含其他验证组件,并将内部的sequencer、driver以及monitor通过build_phase进行创建,使得各个验证组件能够紧密连接起来。这两种i_axi_agent组件包分别作用于射频接口的发送模块和接收模块,目的是为了使配置的active和passive模式能够对interface上的数据信息进行驱动和监测。o_axi_agnet例化模块中的monitor可以监视到测试对象发出的激励数据流,通过TLM接口机制传送到uvm_scoreboard。与此同时,由Matlab封装的record_model模型,通过passive模式占用的moitor去监测收发模型数据流,监测抽取的模型数据流要与DUV产生的激励数据信息进行对比。最终对比的数据流信息通过uvm_scoreboard计分板得出结论,以此判断基带射频接口在收发过程中的数据信息是否完备,统计覆盖率的要求是否达标。

基带射频接口内部的各个寄存器模块是通过APB总线传输地址和数据,而主机转接桥X2P作为通用IP给寄存器分配可用的地址空间。这些寄存器模型可以在内部通过多次例化,主要为射频的收发通路提供使能信息。而DMA模块是为了让射频收发模块的激励信息搬至正确的memory中,一旦搬完有限帧数据流,就会产生中断信息,中断信息会进入ARM处理器,内核发出指令阻止射频收发。SPI模块的引入能够使射频收发正常读写FIFO,同时为外部的射频子板提供模式切换功能。但是基带射频接口内部的模式切换却要采用mode寄存器模块。而这些寄存器模块都是为了给射频收发通路提供随机约束,得到满足要求的激励。

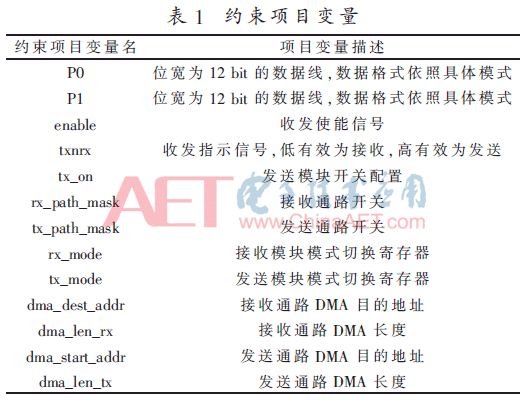

射频收发通路的随机约束信息需要通过ARM处理器的软件环境进行配置,将约束项目存放在transation数据包中,使数据激励能够成为驱动射频收发通路的条件,便于射频收发模块正常工作。同时这些约束项目申明了约束变量,变量列表如表1所示。

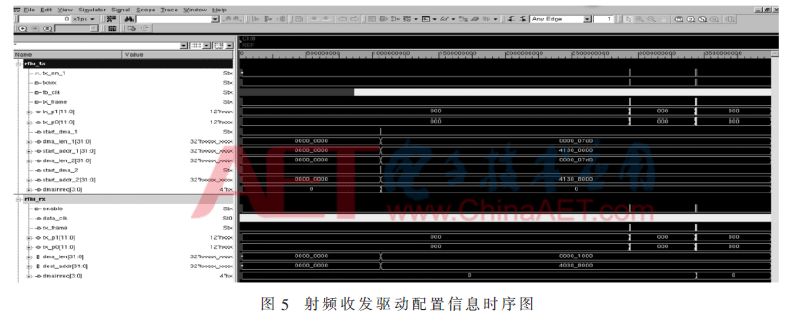

axi_sequencer将激励源传输给驱动器axi_driver,axi_driver需要进行软件配置才能够驱动待测模块。生成射频收发驱动配置信息的时序图如图5所示。软件配置环境如下:(1)对射频通路进行初始化,将接收和发送通路都打开,rx_path_mask设置为3 bit,tx_path_mask设置为15 bit。在此还应进行模式切换,分别对rx_mode和tx_mode进行软件配置选择接口是工作在CMOS TDD模式、CMOS FDD模式还是LVDS模式下。(2)时钟频率配置为了控制外面LPCU模块来满足符合要求的相应带宽的接口频率。(3)配置接收和发送通路使能信息,enable提供接收通路数据源的起始信息,tx_on提供发送通路数据源的位置信息,txnrx则为RFIC仿真模型提供发送通路使能信号。(4)输入DMA地址和DMA长度,使基带芯片的memory能够发送或接收数据,一旦数据流信息获取完毕发出中断dmareq,通知微处理器(arm)等待下次帧数据处理,只有当使能信息enable、tx_on、txnrx变成低电平,数据传输才能结束。(5)配置SPI读写寄存器,控制外部射频子板的模式切换,跟基带射频接口模式保持一致。

record model作为MATLAB封装下的模型,这个模型包含了收发数据源模块、数据格式转换模块、定时寄存器模块、时钟源模块以及收发数据寄存器模块,收发数据寄存器模块的数据流会通过scoreboard调用的写函数存入FIFO中,然后调用比较函数将存入FIFO的数据流与DUV中的数据流进行比对,若比对一致,则验证通过;否则,验证失败。之所以采用这样的比较方式,是因为在复杂的数据比对中更加提高验证的准确性,并使参考模型合理化分析射频接口威廉希尔官方网站 功能的完备性与可靠性。

3.3 验证结果

本次验证主要以RFIU TDD 20 M测试例为例,对射频收发的功能点进行测试,对各个功能点对应的功能覆盖率进行统计,得到射频收发模块功能覆盖率为100%,并分别对射频收发通路的RTL进行代码覆盖率统计,得到代码覆盖率为100%。通过UVM验证,对比计分板上的数据和record_model参考模型的数据,发挥monitor自动监测的作用,监测到数据比对的一致性为100%。其余几种测试例的功能覆盖率能达到100%,并在计分板上得出的数据比对度为100%,从而可以说明射频接口收发模块的功能需求都已达到。

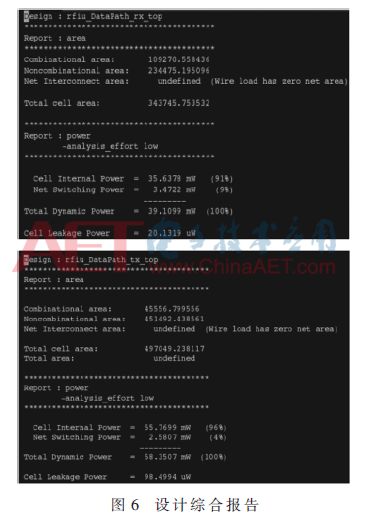

根据Synopsys的Design Compile工具对射频接口威廉希尔官方网站 的RTL代码进行综合,得到射频接收通路的约束面积为0.3 mm2,功耗为39 mW;射频接口威廉希尔官方网站 发送通路的约束面积为0.5 mm2,功耗为58 mW。设计综合报告如图6所示。

4结束语

UVM作为数字IC验证最前沿的方法学,尽管前端仿真搭建平台的周期较长,但是执行效率很高,明显缩短整个研发的验证时间。本文利用AXI总线验证组件搭建基于UVM的基带射频接口威廉希尔官方网站 验证平台,实现了射频接口收发模块功能,在一定范围内,控制了约束面积和功耗,有利于整个基带芯片顺利量产。同时将这种验证架构用在基带芯片其他模块上,能够提高验证效率,并使基带射频接口威廉希尔官方网站 的UVM验证平台发挥着重要的指导作用。在数字接口设计中具有重要的应用价值。

-

IC验证"为什么要学习UVM呢"2020-12-01 0

-

IC验证"UVM验证平台"组成(三)2020-12-02 0

-

IC验证"一个简单的UVM验证平台"是如何搭建的(六)2020-12-04 0

-

IC验证"UVM验证平台加入factory机制"(六)2020-12-08 0

-

IC验证“UVM验证平台加入objection机制和virtual interface机制“(七)2020-12-09 0

-

数字IC验证之“UVM”基本概述、芯片验证和验证计划(1)连载中...2021-01-21 0

-

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...2021-01-21 0

-

如何去设计一种射频前端到基带(SoC)的接口?2021-05-25 0

-

什么是uvm?uvm的特点有哪些呢2022-02-14 0

-

基于UVM的CPU卡芯片验证平台2017-01-07 811

-

基于UVM的验证平台设计研究2017-01-07 810

-

基于UVM的CAN模块自验证方法2017-01-08 754

-

UVM验证平台执行硬件加速2017-09-15 1188

-

ASIC芯片设计之UVM验证2022-11-30 1513

-

fpga验证和uvm验证的区别2024-03-15 1618

全部0条评论

快来发表一下你的评论吧 !