Xilinx首次亮相的Virtex UltraScale+ HBM FPGA

电子说

描述

早在2016年Xilinx就提出了开发Virtex UltraScale+ HBM FPGA器件,在上周举办的硅谷大会上Xilinx首次亮相了Virtex UltraScale+ HBM XCVU37P FPGA器件,Xilinx已经对其进行了测试,支持全速460Gbytes/sec的带宽通信,此外它的资源也是相当的丰富:

-

2852K 系统逻辑单元

-

9Mbits BRAM资源

-

270Mbits 的UltraRAM资源

-

9024 DSP48E2 slices

-

集成8GB HBM DRAM

-

96 Gbps和32.75Gbps GTY SerDes 收发器

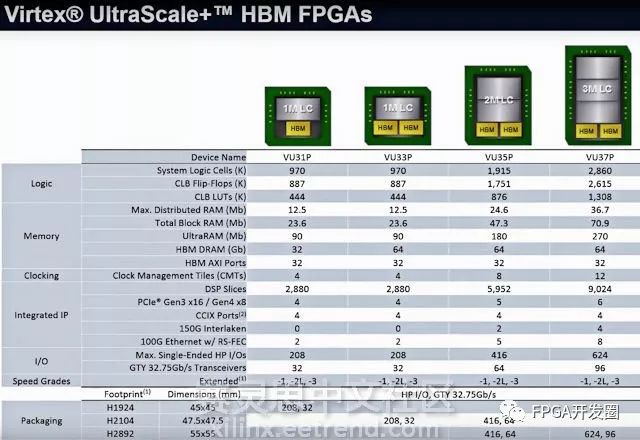

图1:Xilinx推出的Virtex UltraScale+ HBM系列FPGA

如图1所示Xilinx推出的Virtex UltraScale+ HBM系列FPGA共包括四款,分别是VU31P、VU33P、VU35P和VU37P,每款器件都集成了32或64位HBM DRAM以及超过1000 I/O接口,那什么是HBM呢?HBM(High Bandwidth Memory)是一种新型的3D内存技术,采用垂直堆叠的方式实现高速数据传输,以创新性的小尺寸为用户带来真正振奋的性能,同时其抄低功耗和节约空间的特性受到业界的广泛关注。

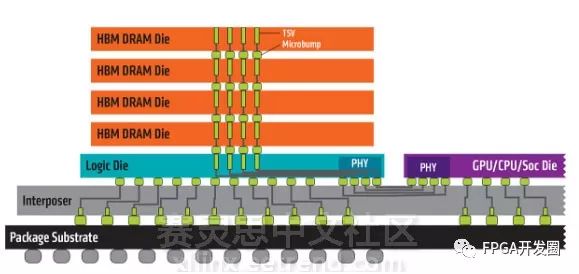

图2:HDM与GPU/CPU/SoC集成方式

随着人工智能、5G通信、大数据、云计算等应用的出现,人们对于通信带宽的要求也在不断的提高,这些应用需要高吞吐、低延迟、高密度部署等特性,传统的DDR SRAM技术不能满足人们对带宽的需求,每秒增加1GB的带宽都将会产生更多的功耗,其技术发展已经进入了瓶颈期。HBM则就像摩天大厦中的楼层一样可以垂直堆叠。基于这种设计,信息交换的时间将会缩短,此外它重新调整了内存的功耗效率,使得每瓦带宽比相对于最先进的GDDR5高出了3倍多,即功耗降低3倍多。

Xilinx首次亮相的Virtex UltraScale+ HBM FPGA:

Xilinx最新推出的Virtex UltraScale+ HBM FPGA是基于UltraScale架构,采用16nm FinFET+工艺技术,集成最多高达8GB的HBM Gen2内存,可提供高达460GB/s的数据通信带宽。Xilinx All Programmable 3D IC 使用堆叠硅片互联 (SSI) 技术,它打破了摩尔定律的限制并且实现了一系列有助于满足最严格设计要求的功能。

最后虽然HBM技术能给我们提供更高的通信带宽,但是它还处在初级发展阶段,比如HBM需要更高的工艺技术因此会大幅度提升成本、大量的DRAM堆叠无疑会产生大量的热,如何散热也是极大的挑战。此外目前只有在高带宽通信应用中HBM才具有显著的优势,但是这应该是半导体行业发展的必然趋势。

-

赛灵思公司宣布其Virtex UltraScale+ FPGA面向首批客户开始发货2019-07-30 2542

-

全新 Virtex UltraScale+ FPGA 评估套件加速高带宽应用2017-01-13 3074

-

12V输入的Xilinx Virtex Ultrascale FPGA电源参考设计2018-08-29 0

-

赛灵思推出全球最大容量的FPGA – Virtex UltraScale+ VU19P2020-11-02 0

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 0

-

Xilinx Virtex Ultrascale FPGA MGT电源解决方案2022-09-21 0

-

Xilinx Virtex Ultrascale FPGA 电源解决方案2017-02-16 1463

-

基于Xilinx 16nm Virtex UltraScale+器件VU9P的异构计算实例2018-06-28 29295

-

Virtex UltraScale+ FPGA收发器的演示2018-11-28 2399

-

Xilinx 16nm Virtex UltraScale+ FPGA器件的功能2018-11-27 3977

-

Xilinx 16nm Virtex UltraScale+ FPGA的展示2018-11-27 3582

-

Xilinx Virtex UltraScale+ HBM FPGA2018-11-22 4095

-

Virtex UltraScale FPGA产品简介资料说明2019-02-19 981

-

xilinx推出全球最大容量FPGA— Virtex UltraScale+器件2019-08-24 3682

-

Virtex UltraScale+ FPGA数据手册:DC和AC开关特性2023-09-13 242

全部0条评论

快来发表一下你的评论吧 !