不用处理器就可以控制FPGA总线的方法你知道吗?

电子说

描述

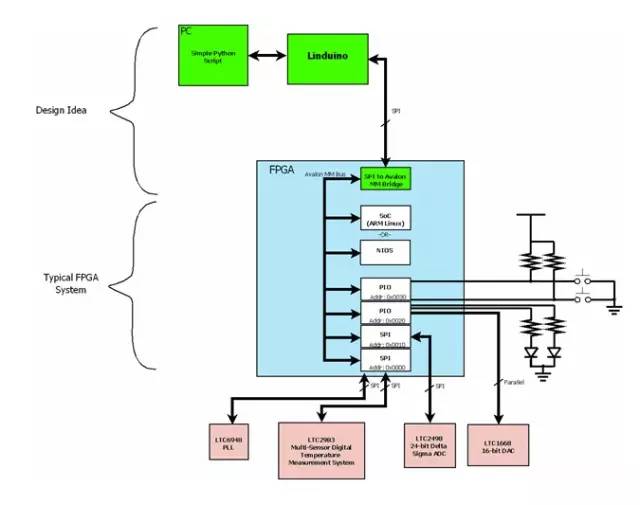

许多FPGA设计使用嵌入式处理器实现控制。典型的解决方案是使用Nios这样的软处理器,虽然内置硬处理器的FPGASoC也变得很流行了。图1显示的是一个典型的Altera FPGA系统,其中包含了处理器和通过Altera的Avalon内存映射(MM)总线连接的各种外设。这些处理器极大地简化了终端应用,但要求很强的编程背景和复杂的工具链知识。这将妨碍调试,特别是当硬件工程师不想求助软件工程师,只需要一种简单的方式读写外设时。

图1:使用Avalon内存映射总线连接的典型Altera FPGA系统。

本设计实例使用Altera的SPI Slave to Avalon MM桥实现了一种挂接到Avalon总线的简单方法。这种技术有两个优势:它不会影响原始系统设计,桥可以与嵌入式处理器共存。对于图1所示的系统来说,这种SPI桥允许工程师直接控制LTC6948小数分频锁相环的频率、设置LTC1668数模转换器的电压、读取LTC2498模数转换器的电压或读取LTC2983的温度,就像处理器那样。

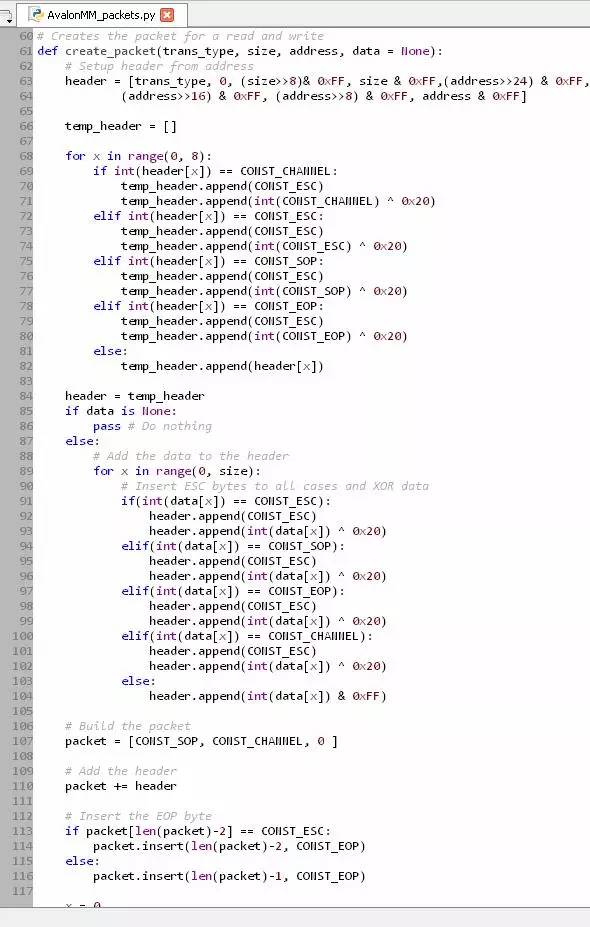

图2:高亮部分+例子代码+反向工程=Python脚本。

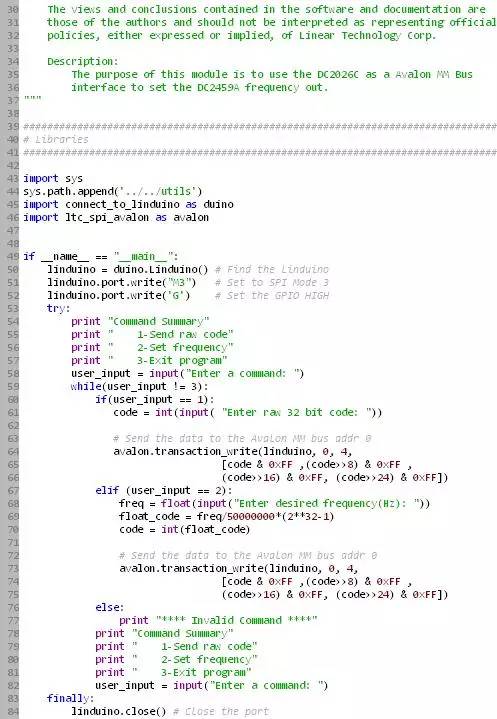

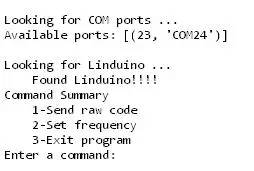

Altera为SPI-Avalon MM桥提供了参考设计。遗憾的是,相关文档非常少,并且将Nios处理器用作SPI主器件。这其实有违使用SPI桥的初衷,因为Nios可以直接连接Avalon MM总线。实用性的SPI主器件是凌力尔特公司的Linduino微控制器,它是Arduino处理器的的克隆版本,不过增加了连接LT演示板的接口等额外功能。其中一个额外功能是电平转换SPI端口。当连接电压低至1.2V的FPGA I/O组时这个电平转换功能特别有用。Linduino固件可以用来接受来自虚拟COM端口的命令,并将命令翻译成SPI处理内容。 在对Altera设计例子进行反向工程后(图2)就能得到一个Python库,接着创建SPI桥可以接受的数据包。这些数据包随后被翻译成Linduino命令。Python脚本随后允许硬件工程师完全控制整个项目,无需重新开发接口协议。LinearLabToolsPhython文件夹中提供了帮助LTC1668数模转换器控制数字图案发生器频率的Python脚本例子。图3显示了演示装置。

图3:插入FPGA威廉希尔官方网站 板(左)的DC2459数模转换器演示板(右)。

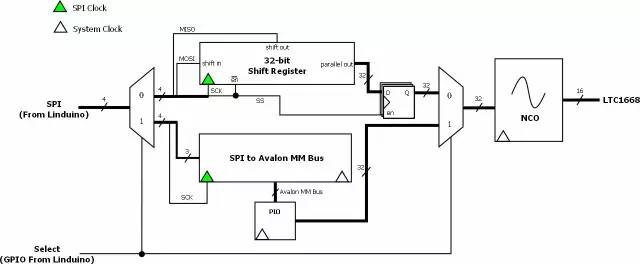

图4显示了系统框图。注意,数字控制振荡器(NCO)可以由移位寄存器或PIO内核进行控制。移位寄存器用于调试,因为它可以直接控制NCO。将GPIO线置高将激活SPI-Avalon桥,进而控制Avalon总线上的32位PIO端口。PIO输出随即用于控制NCO频率。

图4:FPGA系统框图。

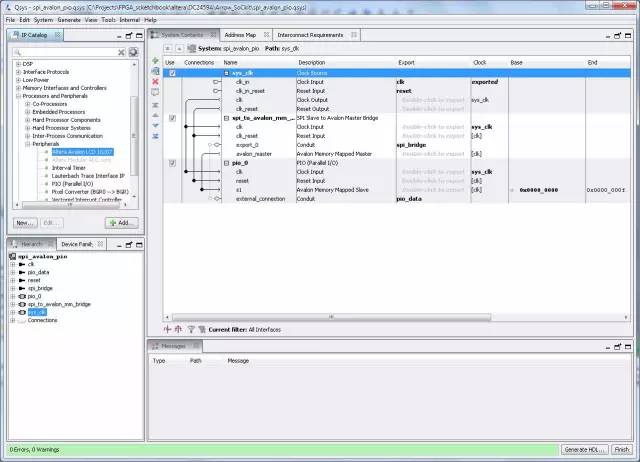

借助基本的一些系统操作,可以将额外的外设内核连接到总线上。为了帮助系统设计,Altera提供了一款名为Qsys的工具,它提供了连接各个IP的图形用户界面(GUI)。Qsys可以将GUI设计的系统(图5)翻译为HDL。外设地址是完全可配置的。在这个案例中,PIO被设为基地址0x0。

图5:Qsys GUI。

当设计在FPGA中实现后,LinearLabTools中提供的Python库包含的两个函数就能连接到设计:

transaction_write(dc2026, base, write_size, data) transaction_read(dc2026, base, read_size)

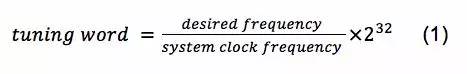

这些函数的第一个参数是Linduino的串口实例。第二个参数是Avalon总线上的外设地址。这两个函数分别用于接收和返回字节列表。当读写IP时这两个函数具有一定的灵活性。为了设置给定例子的NCO,只需要transaction_write一个函数。公式1用于确定调节字。

要将NCO设为1kHz并具有50MSPS采样率,调节字的值需要设为85899或0x00014F8B,并按4个字节一起传送。这样,将数模转换器设为1kHz的Python代码是: transaction_write(linduino_serial_instance, 0, 0, [0x0, 0x01, 0x4F, 0x8B])

图6:Python Avalon总线例子。

图6中的Python脚本描述了用于配置NCO的简单文本接口。值得一提的是:SPI桥使用SPI模式3。这是通过不断的试错,并通过分析Altera例子中的Nios处理器的SPI接口验证后才确定的模式。 本设计实例提供了一种无需使用嵌入式处理器就能控制系统的方法,它能帮助硬件工程师在不打扰软件工程师的情况下搞定一个项目,并且对硬件设计的影响最小。

-

调节多核处理器硬件适应软件设计方法2008-09-25 0

-

数字处理器使用步骤2011-01-07 0

-

【每日一贴日志】亲爱的,你知道吗?2013-09-29 0

-

【FPGA干货分享六】基于FPGA协处理器的算法加速的实现2015-02-02 0

-

流水线操作,应用处理器,应用处理器的结构和原理是什么?2010-03-26 1234

-

无线充电IC你都知道吗2017-01-22 1171

-

6 LX9 FPGA就可以实现开源的“J Core”处理器?2017-02-08 487

-

不用那么麻烦,从iPhone上就可以知道你的电池是否需要更换2017-02-28 24932

-

基于FPGA和多DSP的多总线并行处理器设计2017-10-19 792

-

关于变压器的这些冷知识,你知道吗?2020-02-04 4600

-

关于STM32的这几个寄存器, 你知道吗?2020-03-06 10147

-

应用处理器芯片行业科普2022-01-25 534

-

不使用处理器控制FPGA总线2023-04-08 1052

-

什么是专用处理器?专用处理器的设计方法和工具介绍2023-07-17 1486

-

LED视频处理器是怎么工作的,你知道吗?2023-12-13 1418

全部0条评论

快来发表一下你的评论吧 !