如何走出摩尔定律困境?摩尔定律领域的困境与研究方向详细概述

电子说

描述

计算机体系结构顶会ISCA-18上周结束,图灵奖得主John Hennessy和David Patterson发表特邀报告,展望体系结构新的黄金时代。本届会议近1/3的论文关于神经网络加速器,专用领域架构和软硬件协同设计是最受关注的议题。谷歌、Facebook等非传统硬件公司的存在感也愈发强烈。加州大学圣芭芭拉分校(UCSB)谢源课题组神经网络架构研究团队博士后胡杏、邓磊、谢新峰、谷芃和刘浏对大会技术趋势做了总结。

ISCA是计算机体系结构领域的顶级会议,本届ISCA的亮点无疑是新当选的图灵奖得主、体系结构领域的两位宗师级人物John L. Hennessy和David A. Patterson做的特邀报告。

本文将先从两位图灵奖得主的报告讲起,总结会议关键技术趋势,展现与会专家的观点与评论,最后对论文接收和子领域热度等会议情况进行介绍。

从这届会议中可以发现四大关键技术趋势,

专用架构与软硬件协同设计将是未来专有化架构研究趋势,也将是走出摩尔定律困境一个富有前景的方向;

神经网络加速器开始从设计走向落地;

由于Meltdown和Spectre,硬件安全性得到更多关注。安全领域的研究方法除软件、系统,也需要从体系结构的层面来进一步加强;

RISC-V为敏捷开发提供了可能,未来可能成为开源硬件的基础。

如何走出摩尔定律困境?Keynote演讲人、Facebook Research的Kim Hazelwood博士半开玩笑说,这届ISCA每个keynote前面都要放这张slide,表明了领域的困境与研究方向

Turing Lecture:体系结构迎来新的黄金时代

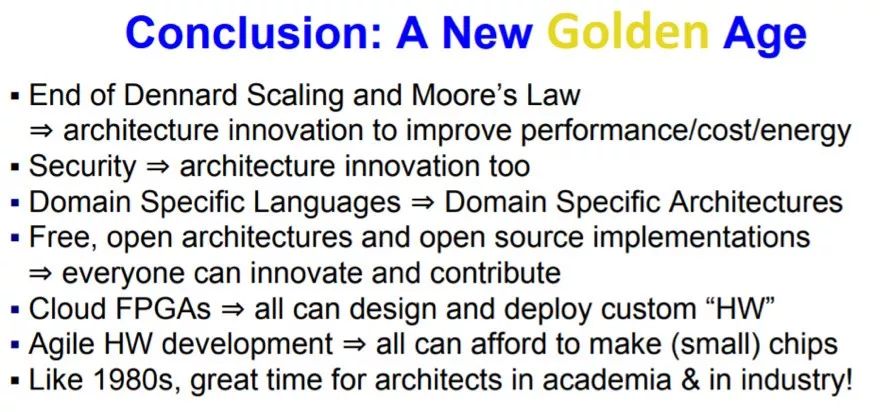

在本次大会的图灵讲座(Turing Lecture)上,2017年荣获图灵奖的John L. Hennessy和David A. Patterson首先简要回顾了计算机体系结构的发展史,总结了目前体系结构研究的两大挑战:通用处理器性能提升的停滞和体系结构安全的问题。

两位演讲者提及到上世纪80年代是体系结构发展的黄金时期,诸如RISC、超标量处理器(superscalar)、多层缓存(multilevelcaches)、预测技术(speculation)、编译器优化(compileroptimization)等等体系结构创新,使得计算机性能每年提升约60%。在上世纪90年代到21世纪初,由于体系结构创新的放缓,计算机性能的提升主要依赖于工艺技术的进步、更高的时钟频率和更大的缓存。

目前,随着摩尔定律(Moore’s Law)和登纳德缩放比例定律(Dennard Scaling)的放缓甚至停滞,单处理器核心的性能每年的提升已降为3%左右。与此同时,近来的计算机漏洞幽灵(Spectre)和融毁(Meltdown),均利用了体系结构设计的缺陷,而体系结构的安全性问题在近几十年来没有得到体系结构研究者和设计者的足够关注。

David Patterson(左)与John Hennessy(右)和与图灵像合影;旁边展示了本届ISCA赞助商,谷歌、微软、亚马逊、Facebook等非传统硬件厂商的存在感在增强

对于这些挑战,两位演讲者总结了体系结构新的机遇:(1)软硬件协同设计(Hardware/Software Co-Design)和高层专用语言(High-Level and Domain-Specific Languages);(2)计算机体系结构安全性的提升;(3)开源体系结构设计(Free and Open Architectures and Open-Source Implementations);(4)创新的敏捷芯片开发(Agile Chip Development)。

这其中(1)强调了专用体系结构(Application Specific IC/Architecture)和专用编程语言(Domain Specific)的开发,对于提升特定领域性能、功耗和开发效率的重要性,尤其是神经网络(neural network)、图计算(graph computation)等新兴且需要高性能计算的领域。(2)强调了安全应该和性能同样地受到体系结构设计研究的重视,尤其是防止信息泄露和边信道攻击(Side-channel attack)。(3)强调了体系结构设计开源,尤其是指令集架构(Instruction Set Architecture)开源的重要性。两位演讲者介绍了他们近几年在RISC-V方面所作的工作。最后,(4)强调了怎样缩短芯片开发的时间和成本这两个核心要素。他们认为敏捷开发(Agile development process)可以使得较小的研究开发组可以反复迭代地在短时间内廉价地开发产品原型。最终的目标是体系结构的研究者可以利用这种开发方式,得以流片(tape-out)验证有价值的设计方案。

非硬件公司存在感增强,机器学习影响架构和编程语言

在keynote方面,本次大会邀请了Kim Hazelwood(Facebook Research),Kunle Olukotun(斯坦福大学)以及Doug Burger(Microsoft Research),分别针对Facebook的机器学习、软件2.0(机器学习怎样影响架构和编程语言)和数据流架构(Explicit Dataflow Execution)进行了介绍。

值得一提,本次大会同时颁发了 Eckert-Mauchly Award,这是计算机体系结构领域最崇高的奖项,此前John Hennessy和David Patterson也先后获得过这一荣誉。

今年Eckert-Mauchly Award的获奖者是华盛顿大学(University of Washington's Paul G. Allen School of Computer Science & Engineering)的Susan Eggers教授,基于她对同步多线程体系结构和多核共享和一致性问题的贡献。她也是首位获此殊荣的女性。Susan Eggers本身经历比较传奇,她在本科拿到经济学学士后,在其他领域工作了十年才转到计算机领域,47岁时博士毕业到华盛顿大学开始教职生涯。

此外,Gabriel Loh本次因在三维堆叠架构领域的杰出贡献,获得Maurice Wilkes奖,Wilkes奖每年一次,主要表彰推动体系结构工业发展的个人。Gabriel Loh于 2010年加入AMD,2013年成为AMD Fellow。

谢源课题组与Gabriel Loh(后排右数第六位)合影,后排右一是谢源教授

技术趋势预测:专用领域架构全栈设计和软硬件协同,神经网络加速器从设计到落地

1、专用领域语言 (Domain Specific Language) 与专用领域架构(Domain Specific Architecture)计算模型与架构硬件能力的抽象至关重要。

针对专用领域或者应用的架构设计仍是今年ISCA的一大焦点,随之而来的是专用领域语言与硬件的设计又被带入了大众的视野。随着专用领域架构的发展,对这些架构进行支持的编程语言也受到了广泛的关注。这种考虑专用应用领域的架构与语言的软硬件协同设计方法将会是未来专有化架构研究的一个趋势,以及这将成为走出摩尔定律带来的困境的一个富有前景的方案。

在图灵奖演讲中,2017年图灵奖获得者John Hennessy教授指出了,随着摩尔定律的终结,我们需要新的计算机架构研究方法。他预言,计算机架构团队纵向整合的时代即将复兴,体系结构设计者将如过去一样,不仅需要了解底层器件,工艺,以及威廉希尔官方网站 的知识,也需要有着对编程语言以及编译器的了解。John在总结中慷慨激昂地提到:“一切旧的东西又是新的!(Everything old is new again!)”

John Hennessy在演讲中指出,随着摩尔定律的终结,我们需要新的计算机架构研究方法。图片来自ACM Twitter

在ISCA第二天的keynote中,来自斯坦福大学的Kunle Olukotun教授介绍了他们对于软件2.0时代的计算机系统研究。他们指出了神经网路应用对计算机硬件设计带来了极其难得的机遇,最重要的是,该应用对于硬件的一些正确性指标有着相对强大的容错能力,比如内存一致性与计算精确度。同时,在他的演讲中,Kunle也强调了全栈优化的重要性。在他们的研究中,他们提出了若干并行计算的模式,并针对这些专用模式进行专用领域硬件的设计,极大提升了在专用领域硬件的性能,以及通过开发专用领域语言减轻了软件开发者在新兴架构上开发高性能程序的压力。

专用领域带来了新的机会,这些新的机会帮助我们设计新硬件,也让软件开发变得更加高效。从这些研究中,我们也看到了软硬针对专用协同设计的未来!

2、神经网络加速器从设计到落地:加速器落地真实物理系统及全系统优化

纵观近两年神经网络加速所采用的模型压缩算法,主要包括对于神经元状态和权重连接参数的稀疏化和低比特量化,以及加速器硬件优化策略,主要包括处理单元数据复用、存储计算一体化、存储器优化等,对加速器性的提升几乎已经做到了极致的优化。从最初的纯硬件优化到如今的算法和硬件协同优化,使得神经网络加速器的优化空间逐渐收缩,基于现有方法和技术很难再实现大幅度的性能改善。在这样的情况下,未来会逐渐发生从如何设计加速器到如何使用加速器的转变,从设计加速器本身到设计全系统,并最终落地现实应用场景。

一方面,需要尽快构建神经网络加速器的编程抽象模型、编程语言和编译器,从而促进加速器的模块化、标准化和易用性;另一方面,需要根据不同应用场景,选择对应特性的加速器进行真实物理系统设计、优化和实现,从而促进加速器落地于现实生活。正如两位图灵奖获得者JohnL. Hennessy and David A. Patterson在演讲中提到的两大热点:专用域架构(Domain-specific Architecture)和专用域语言(Domain-specific Language),接下来学术界和产业界会更加关注上层语言的设计和开发。

同时,在移动平台分会场,来自康奈尔大学的Mark Buckler和来自罗彻斯特大学的Yuhao Zhu在演讲中均展示了如何把神经网络加速器作为一个IP模块进行移动视觉系统设计和优化。由此可见,神经网络加速器的标准化或开源化,对于加速器的推广和应用至关重要。

3、安全性受到关注。安全领域的研究方法除软件,系统,也需要从体系结构的层面来进一步加强

针对最近的体系结构安全性问题(Meltdown& Spectre Design Flaws),本次大会的专家讨论(panel discussion)邀请了5位专家和教授:Mark Hill作为主持人,Paul Kocher, Ruby B. Lee, Simha Sethumadhavan和Timothy Sherwood作为嘉宾对安全问题展开了讨论。Paul指出了现有系统设计主题思想是面向性能,而缺乏安全性分析和设计。虽然性能的量化指标丰富且成熟,但安全性指标的量化体系并没有建立,比如缓存行为,预测器,debug模式,以及功耗,内部传感器等等对安全性的影响。由于量化分析方法的缺乏,加上微体系结构设计本身对软件开发者不开放,导致系统构建时存在一些错误的安全性假设,也无法做性能和安全性的联合优化和管理。Ruby Lee,Samira和Tim都认为体系结构社区需要对安全性投入更多关注,设计安全性能感知的计算机体系结构十分重要。

4、RISC-V为敏捷开发提供了可能,未来可能成为开源硬件的基础

从两位图灵奖得主的演讲当中,我们可以看到RISC-V作为开源精简指令集对专用领域架构的重要性。随着数据中心定制化硬件的普及,例如谷歌TPU和微软Brainwave,硬件架构师不能仅模拟单节点而把问题留给流片后的测试,也需要模拟定制化部分。然后缺少高效和可扩展的模拟环境阻碍着新一代Warehouse-Scale Computers (WSCs) 的发展。

来自加州大学伯克利Krste Asanovi教授团队的FireSim填补了这一项空白;也正是主推RISC-V的团队。通过利用云端FPGA,FireSim结合基于RISC-V的Rocket Chip和cycle-accurateC++ switch模型可以模拟多达4096个核心和16TB存储器。

同样是来自伯克利的另一项工作,针对GarbageCollection设计了硬件加速器,并且集成到RocketChip 当中。整个系统从JavaVM到Linux再到FPGA全面地展示了端到端模拟能力。同时,在关于RISC-V对计算机体系结构研究的workshop(CARRV)当中,基于RISC-V 的工具链在包括模拟器,加密,和数字信号处理中都影响着学界和业界。

大会概况:28%的论文有关神经网络加速器,清华大学入选一篇

1、神经网络加速依旧火热

神经网络加速器依旧持续火热,除两个机器学习系统分会场外,还分布于云数据中心、新型应用加速、新型计算范式、内存持久性、新型存储器、移动平台等各大分会场。

神经网络加速器共计接收18篇论文(28%),从研究内容可分为:DNN推理加速(10篇)、移动系统(3篇)、脉冲神经网络(2篇)、DNN训练加速(1篇)、GAN加速(1篇)、编程指令集架构(1篇)。

论文主要来自于美国,包括微软、伊利诺伊大学香槟分校(UIUC)、威斯康星大学、密歇根大学、康奈尔大学、罗彻斯特大学、乔治亚理工学院、加州大学圣地亚哥分校(UCSD)、加州大学伯克利分校(UCB)、佛罗里达大学、ARM、高通(Qualcomm)、英伟达(NVIDIA)等,4篇来自于亚洲:清华大学、首尔国立大学(SNU)和新加坡国立大学(NUS),2篇来自于欧洲加泰罗尼亚理工大学(UPC)。

本届大会对于DNN推理阶段的加速优化呈现多样化,以DNN推理加速的10篇论文为例,3篇针对稀疏网络(解决自动语音识别系统中由于网络裁剪导致的分类置信度下降和执行时间增长的问题;通过预测零状态输出神经元从而去除与其相关的冗余计算)、3篇针对低比特量化网络(利用数据量化后状态有限的特性从而共享重复的神经元激活状态和权重参数状态,达到减小计算的目的;设计支持量化比特数可变的加速器方案,提高对量化网络支持的通用性)、2篇进行SRAM缓存计算(Processing in SRAM)、1篇进行eDRAM刷新优化(对于生命周期较短的数据不进行刷新,从而极大降低功耗)、1篇面向FPGA数据中心(提升数据中心对于用户推理需求的响应时间)。

2、机器学习与系统得到深入探讨

机器学习与系统设计之间的关系也在此次大会中进行了深入的探讨,主要包括两个方向:1)为机器学习应用构建加速系统;2)使用机器学习方法加速系统设计。大会第一天keynote由Kim Hazelwood介绍Facebook在第一个技术方向的尝试和探索。Kim认为除计算瓶颈外,存储瓶颈和软件瓶颈也是系统构建时要考虑的关键因素。AIDArchworkshop讨论了第二个技术方向。DanielSchanwz 教授和Cliff Young介绍了体系结构领域中使用机器学习方法来优化系统设计,以及软硬件联合优化的重要性和可能性。

3、基础框架和模拟器

DNN加速器模拟:来自Gerogia Tech和NVIDIA Research的团队在这次ISCA tutorial公布了两个支持快速高效DNN加速器设计的工具:MAESTRO和MAERI。MAESTRO是针对不同卷积dataflow的分析工具。用户可以通过改变loop-ordering,loop unrolling, spatial tiling和temporal tiling来模拟不同的dataflow,并且能在用户定义的处理单元数目和缓存大小下估计运行时间和能耗。参数化和模块化的DNN加速器生成器MAERI可以输出RTL,并且通过ASIC或者FPGA设计流程估计性能功耗和面积。目前MAERI支持卷积,LSTM,pooling,和全连接层,已经完整的DNN模型运行。

GPU模型。AMD Research在gem5中扩展了APU模型。该模型使用基于GCN gen3ISA 的GPU时序并且支持开源Radeon OpenCompute Platform (ROCm)。用户可以在gem5APU 模拟器上运行C++,OpenMP,HIP,和OpenCL编写的应用,包括传统的GPU workloads和机器学习应用。由于APU中GPU直接与主存交互,针对GPU的访存优化得以更方便在gem5中验证。除此之外,来自康奈尔大学的研究人员在workshop中展示了在gem5中基于RISC-V的多核心模拟器。

4、其他方向

对于编程语言的动态功能以及系统进行从体系结构层面进行支持,在今年ISCA的论文中受到了广泛的关注。在编程语言的动态功能支持上,来自UCB的Martin Maas等人展示了针对Java内存管理中垃圾回收的硬件优化。对于系统层面的支持,本次ISCA录用文章的关注点仍然在内存,包括内存模型,虚拟内存,内存一致性,内存持久性(Memory Persistence)。

除此之外,新型互连架构也受到了一定程度的关注,这些互连架构有一些关注于芯片间的互连,另一些则关注分布式系统中的网络互联。最后,关于资源分配,一个传统操作系统最关键的任务之一,来自UIUC的Josep Torrellas教授等人提出了基于健壮控制理论(Robust Control Theory)的分层资源控制方法,极大提升资源分配的效率。

综上所述,在今年ISCA中,从体系结构对于操作系统以及编程语言的支持,尤其是内存系统的支持,仍然有广泛的关注。这其中的许多研究,都围绕着基于加速器的异构系统以及基于持久性内存的系统所带来的问题。我们期待这些研究对于实际的新兴架构部署能提供强有力帮助。

-

晶圆和摩尔定律有什么关系?2011-12-01 0

-

介绍28 nm创新技术,超越摩尔定律2012-08-13 0

-

摩尔定律也适用于EPON芯片商用之路?2011-09-27 0

-

半导体行业的里程碑“摩尔定律”竟是这样来的2016-07-14 0

-

摩尔定律推动了整个半导体行业的变革2019-07-01 0

-

摩尔定律还能走多远看了就知道2021-02-01 0

-

摩尔定律在测试领域有哪些应用?2021-04-13 0

-

请问摩尔定律死不死?2021-06-17 0

-

摩尔定律,摩尔定律是什么意思2010-02-26 1592

-

摩尔定律_摩尔定律是什么2012-05-21 2788

-

摩尔定律的历程2017-10-24 2353

-

摩尔定律是什么_摩尔定律提出者及含义2018-03-09 30471

-

什么是摩尔定律?2023-08-05 5219

-

摩尔定律为什么会消亡?摩尔定律是如何消亡的?2023-08-14 2680

-

功能密度定律是否能替代摩尔定律?摩尔定律和功能密度定律比较2024-02-21 734

全部0条评论

快来发表一下你的评论吧 !