Wishbone部分地址译码的实现

电子说

描述

很多总线标准中,从设备必须译码所有的地址,这称为全地址译码。比如在PCI总线中,每一个从设备都必须具有32位的地址输入,并对这32位的地址进行译码以确定如何响应主设备的请求。

片上总线规范比如Wishbone规范支持部分地址译码。在部分地址译码总线规范中,从设备只需要译码自己所使用的地址空间。比如如果一个从设备只有4个地址,它就只需译码2比特地址而不是32位地址。这样做的好处是:地址译码速度快,地址译码逻辑少,从设备可自由定义地址总线宽度。

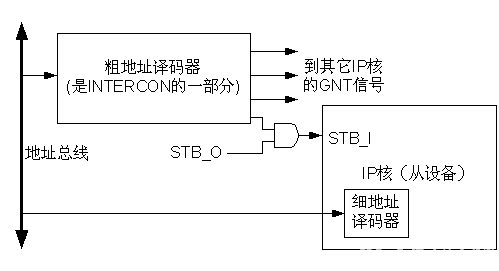

图26 Wishbone部分地址译码的实现

Wishbone部分地址译码的实现如图26所示。对于图中所示IP核,我们假设其只有4个地址,对应4组寄存器。地址译码器首先译码出其地址并给出选择信号,该选择信号与共享总线的STB_O相与输入到IP核的STB_I。而地址总线的最低2位被直接连接到IP核,IP核再根据这两位译码出当前操作选中的是具体哪个寄存器。

Wishbone共享总线示例中的仲裁器可以设计如下:

//the ACMP0 is for slave0: Flash

//the ACMP1 is for slave1: SRAM

module address_decoder2S(addr_i,ACMP0,ACMP1);

input [31:0]addr_i;

output ACMP0,ACMP1;

parameter ADDR_LOW_S0=32'b0;

parameter ADDR_HIGH_S0=32'h1FFFFF;//2M space for Slave 0;

//the rest of the space for Slave 1,so we do not need a dummuy slave;

assign ACMP0=addr_i<=ADDR_HIGH_S0;

assign ACMP1=~ACMP0;

endmodule

-

51单片机P0口已用作地址\数据总线,还能用来当做普通I\O使用吗?2015-09-26 0

-

什么是差分地址呢?2016-07-01 0

-

请问AD5933威廉希尔官方网站 设计需要把模拟部分和数字部分地隔离吗?2018-10-17 0

-

IO接口地址译码威廉希尔官方网站2009-03-25 4936

-

I/O地址译码实验2009-03-25 4282

-

地址译码威廉希尔官方网站 设计实验报告2018-03-02 11123

-

英国计划在部分地区开展自动驾驶公交车和出租车服务试验2018-12-09 952

-

AT&T宣布其5G网络已在美国12个城市的部分地区上线2018-12-19 802

-

AT&T在美国部分地区提供5G移动网络服务2018-12-24 3242

-

Verizon已正式在芝加哥和明尼阿波利斯的部分地区部署了5G移动服务2019-04-08 576

-

沃达丰新西兰部分地区启用5G,计划采用诺基亚设备进行升级2019-12-12 2646

-

部分地区直接将4G套餐下架?你被5G了吗?2020-11-02 2055

-

Verizon在另外四个城市的部分地区点亮了其5G网络2020-12-18 1501

-

亚马逊部分地区iOS应用商店首次亮相新的App图标2021-03-02 2358

-

Verizon宣布在克利夫兰的部分地区推出5G家庭互联网服务2021-03-19 1493

全部0条评论

快来发表一下你的评论吧 !