采用VHDL语言实现SDRAM与双口RAM的数据传输系统设计

描述

RAM(随机存取存储器 是一种在电子系统中应用广泛的器件,通常用于数据和程序的缓存。随着半导体工业的发展,RAM获得了飞速的发展,从RAM、DRAM(Dynamic RAM,即动态RAM)发展到SDRAM(Synchronous Dynamic RAM,即同步动态RAM),RAM的容量越来越大、速度越来越高,可以说存储器的容量和速度已经成为半导体工业水平的标志。

1、任务背景

SDRAM具有大容量和高速的优点,目前其存取速度可以达到100~133MHz,单片容量可以达到64Mbit或更高,因此在需要高速、大容量存储器的系统中得到广泛应用,如应用在目前的计算机内存中。但是SDRAM的控制比较复杂,其接口不能直接与目前广泛应用的普通微处理器例如MCS-51系列、MOTOROLA 68000系列 连接,这样就限制了SDRAM在微处理器系统中的应用。

我们的任务是设计一个通用微处理器,它要具有语音、数据、图像等多种处理功能,并具有RS232、USB等多种接口,另外由于多个通道的数据都需要进行缓存和处理,因此高速大容量的缓存是此系统必须的,所以选用了SDRAM作为缓存器件。来自多个输入通道的数据在采集后需要暂时存储在SDRAM中,处理后的数据也需要存储在SDRAM中,再输出到输出通道中。在SDRAM与多个输入输出通道之间,采用多个双口RAM作为接口器件。输入通道采集的数据首先存储在双口RAM中,采集满后,通过若干条指令将RAM中的数据转移到SDRAM中的一定位置中,将SDRAM中的数据转移到RAM中也只需要若干条指令来完成。这样通过几条指令来设置RAM起始地址、SDRAM起始地址、传送数据长度、传送数据方向之后,SDRAM与RAM之间数据传送就完全可以通过硬件实现,不必占用微处理器的指令时间。

2、SDRAM简介

SDRAM具有多种工作模式,内部操作是一个非常复杂的状态机。SDRAM的管脚分为以下几类:

(1) 控制信号:包括片选、时钟、时钟有效、行/列地址选择、读写选择、数据有效;

(2) 地址:时分复用管脚,根据行/列地址选择管脚控制输入地址为行地址或列地址;

(3) 数据:双向管脚,受数据有效控制;

根据控制信号和地址输入,SDRAM包括多种输入命令:① 模式寄存器设置命令;② 激活命令;③ 预充命令;④写命令;⑤ 读命令;⑥自动刷新命令;⑦ 自我刷新命令;⑧突发停止命令;⑨ 空操作命令。

根据输入命令,SDRAM状态在内部状态间转移。内部状态包括:①模式寄存器设置状态;②激活状态;③预充状态;④写状态;⑤读状态;⑥自动刷新状态;⑦自我刷新状态;⑧节电状态。

3、SDRAM接口状态机设计

根据系统的要求,采用固定型号SDRAM,我们对SDRAM的操作进行了以下简化:

(1) 不考虑随机存取模式,只采用突发读写数据模式,固定突发数据长度为2;

(2) 固定SDRAM读命令输入到数据输出延时时钟周期为2;

(3) 刷新模式仅采用自我刷新模式,不采用自动刷新模式;

(4) SDRAM的初始化、节电模式由微处理器控制;

(5) SDRAM为16位数据总线,RAM为32位数据总线,SDRAM进行一次突发操作,RAM进行一次读写操作,以实现速度匹配;

(6) SDRAM和RAM读写地址采用递增模式,连续变化。

其中,初始化、自我刷新、电源关断、读操作、写操作、预充等状态又分别各由一组子状态组成。

为充分利用SDRAM的高速存取特性,读、写时序必须仔细设计,应基本可以实现每个时钟周期进行一次数据存取。如下图所示。

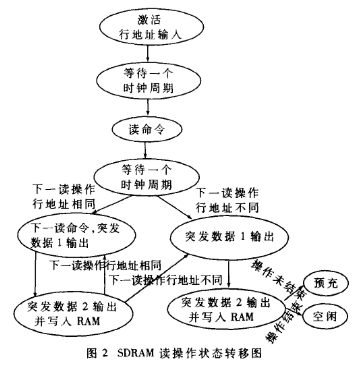

3.1 SDRAM读操作时序设计

当数据转移方向为从SDRAM到双口RAM时,如果SDRAM读操作行地址未发生变化,可以满足每时钟周期输出一次数据的高速操作。但是当SDRAM行地址发生变化时,必须返回预充状态,由于从SDRAM的读命令输入到SDRAM数据输出之间有2个时钟周期的延时,所以判断下一读操作的行地址是否发生变化必须提前两个周期判断。如下图所示。

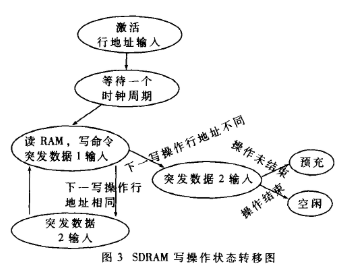

3.2 SDRAM写操作时序设计

当数据转移方向为从双口RAM到SDRAM时,如果SDRAM写操作行地址未发生变化,可以满足每时钟周期写入一次数据的高速操作。但是当SDRAM行地址发生变化时,必须返回预充状态,由于从SDRAM的写命令输入到SDRAM数据输入之间没有延时,所以判断下一写操作的行 地址是否发生变化无需提前判断,因此写操作状态转移图比读操作部分简单。

在所设计的读、写操作时序中,SDRAM地址、数据、控制信号和RAM部分的地址、数据、读写控制信号均由有限状态机产生,因此在状态转移过程中还必须仔细考虑RAM部分输出控制信号的时序关系。

4、VHDL实现

硬件描述语言VHDL(Very=high Speed IC HARDWARE DESCRIPTION Language)是一种应用于威廉希尔官方网站 设计的高层次描述语言,具有行为级、寄存器传输级和门级等多层次描述,并且具有简单、易读、易修改和与工艺无关等优点。目前VHDL语言已经得到多种EDA工具的支持,综合工具得到迅速发展,VHDL语言的行为级综合也已经得到支持和实现,因此利用VHDL语言进行威廉希尔官方网站 设计可以节约开发成本,缩短周期。在VHDL语言输入中也有多种形式,例如可以支持直接由状态转移图生成VHDL语言。因此在设计SDRAM状态转移图后,可以直接产生VHDL程序,在功能仿真正确后,可以进行综合、FPGA布局布线和后仿真。

以上介绍了一种应用于通用微处理器系统中的SDRAM与双口RAM之间的数据转移接口控制威廉希尔官方网站 ,由VHDL语言设计,用XILINX公司4000系列FPGA实现,目前该威廉希尔官方网站 硬件实现和微处理器系统已经通过验证,证明可将SDRAM作为高速、大容量存储器应用在简单电子系统中。

责任编辑:gt

-

基于PCI总线的数据传输系统2011-04-25 1681

-

基于双端口RAM的双DSP系统搭建2016-05-04 0

-

基于SDRAM的u***与pc之间数据传输资料2017-11-27 0

-

VHDL语言实现多DSP局部总线与VME总线接口设计2019-04-12 0

-

SDRAM与双口RAM数据转移接口控制威廉希尔官方网站2019-06-10 0

-

如何采用FPGA和CMOS数字传感器实现图像数据传输的图像监测系统?2021-05-26 0

-

数据传输的通信系统设计2009-06-13 539

-

基于FPGA的双口RAM实现及应用2010-02-11 551

-

基于USB2.0的红外数据传输系统的设计与实现2010-03-13 1629

-

SDRAM接口的VHDL设计方案2011-06-01 652

-

VHDL语言实现DDR2 SDRAM控制2011-09-01 1018

-

基于VHDL的SDRAM接口设计2011-11-11 1580

-

SOPC实现的PCI总线高速数据传输系统2012-02-10 1480

-

DDR SDRAM是拥有着双倍数据传输率的SDRAM2020-07-16 2255

-

基于双口RAM和SN74LVTH245A芯片实现长距离数据传输系统的设计2021-03-19 3951

全部0条评论

快来发表一下你的评论吧 !