浅析PCIE总线信号分布及使用情况

电子说

描述

PCI-Express简称PCI-E于2001年春季由Intel公司提出。随后在2001年底,包括Intel、AMD、DELL、IBM在内的20多家业界主导公司开始起草新技术的规范,并在2002年底完成,对其正式命名为PCI Exress 。

PCI-Express的接口根据总线带宽不同而有所差异,包括X1、X4、X8以及X16(X2)模式用于内部接口而非插槽模式。较短的PCI-Express卡可以插入较长的PCI-Express插槽中使用。

PCI-E 1X的网卡

PCI-E 4X的双端口网卡

PCI-E 16X的显卡

PCI-Express接口连接器

PCIe电源有+12V、+3.3Vcc和+3.3Vaux。其中+12V主要给PCIe设备(如显卡)提供更大的供电能力(PCIe3.0的插槽最大有150w)。

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。因为Vaux在多数情况下并不会被移除,因此当PCIe设备的Vcc恢复后,该设备不用重新恢复使用Vaux供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

PCIe链路的最大宽度为×32,但是在实际应用中,×32的链路宽度极少使用。在一个处理器系统中,一般提供×16的PCIe插槽,并使用PETp0~15、PETn0~15和PERp0~15、PERn0~15共64根信号线组成32对差分信号,其中16对PETxx信号用于发送链路,另外16对PERxx信号用于接收链路。除此之外PCIe总线还使用了下列辅助信号。

1PERST#信号

该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设备将进行复位操作。

2REFCLK+和REFCLK-信号

在一个处理器系统中,可能含有许多PCIe设备,这些设备可以作为Add-In卡与PCIe插槽连接,也可以作为内置模块,与处理器系统提供的PCIe链路直接相连,而不需要经过PCIe插槽。PCIe设备与PCIe插槽都具有REFCLK+和REFCLK-信号,其中PCIe插槽使用这组信号与处理器系统同步。

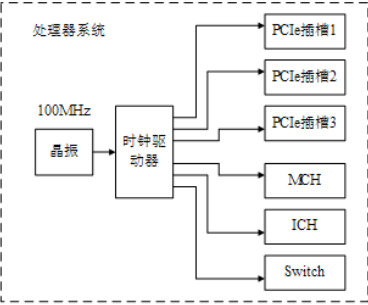

在一个处理器系统中,通常采用专用逻辑向PCIe插槽提供REFCLK+和REFCLK-信号,如下图所示。其中100Mhz的时钟源由晶振提供,并经过一个“一推多”的差分时钟驱动器生成多个同相位的时钟源,与PCIe插槽一一对应连接。

参考时钟与PCIE插槽的连接

PCIe插槽需要使用参考时钟,其频率范围为100MHz±300ppm。处理器系统需要为每一个PCIe插槽、MCH、ICH和Switch提供参考时钟。而且要求在一个处理器系统中,时钟驱动器产生的参考时钟信号到每一个PCIe插槽(MCH、ICH和Swith)的距离差在15英寸之内。通常信号的传播速度接近光速,约为6inch/ns,由此可见,不同PCIe插槽间REFCLK+和REFCLK-信号的传送延时差约为2.5ns。

当PCIe设备作为Add-In卡连接在PCIe插槽时,可以直接使用PCIe插槽提供的REFCLK+和REFCLK-信号,也可以使用独立的参考时钟,只要这个参考时钟在100MHz±300ppm范围内即可。内置的PCIe设备与Add-In卡在处理REFCLK+和REFCLK-信号时使用的方法类似,但是PCIe设备可以使用独立的参考时钟,而不使用REFCLK+和REFCLK-信号。

在PCIe设备配置空间的Link Control Register中,含有一个“Common Clock Configuration”位。当该位为1时,表示该设备与PCIe链路的对端设备使用“同相位”的参考时钟;如果为0,表示该设备与PCIe链路的对端设备使用的参考时钟是异步的。

在PCIe设备中,“Common Clock Configuration”位的缺省值为0,此时PCIe设备使用的参考时钟与对端设备没有任何联系,PCIe链路两端设备使用的参考时钟可以异步设置。这个异步时钟设置方法对于使用PCIe链路进行远程连接时尤为重要。

在一个处理器系统中,如果使用PCIe链路进行机箱到机箱间的互连,因为参考时钟可以异步设置,机箱到机箱之间进行数据传送时仅需要差分信号线即可,而不需要参考时钟,从而极大降低了连接难度。

3WAKE#信号

当PCIe设备进入休眠状态,主电源已经停止供电时,PCIe设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe设备提供主电源Vcc。在PCIe总线中,WAKE#信号是可选的,因此使用WAKE#信号唤醒PCIe设备的机制也是可选的。值得注意的是产生该信号的硬件逻辑必须使用辅助电源Vaux供电。

WAKE#是一个Open Drain信号,一个处理器的所有PCIe设备可以将WAKE#信号进行线与后,统一发送给处理器系统的电源控制器。当某个PCIe设备需要被唤醒时,该设备首先置WAKE#信号有效,然后在经过一段延时之后,处理器系统开始为该设备提供主电源Vcc,并使用PERST#信号对该设备进行复位操作。此时WAKE#信号需要始终保持为低,当主电源Vcc上电完成之后,PERST#信号也将置为无效并结束复位,WAKE#信号也将随之置为无效,结束整个唤醒过程。

PCIe设备除了可以使用WAKE#信号实现唤醒功能外,还可以使用Beacon信号实现唤醒功能。与WAKE#信号实现唤醒功能不同,Beacon使用In-band信号,即差分信号D+和D-实现唤醒功能。Beacon信号DC平衡,由一组通过D+和D-信号生成的脉冲信号组成。这些脉冲信号宽度的最小值为2ns,最大值为16us。当PCIe设备准备退出L2状态(该状态为PCIe设备使用的一种低功耗状态)时,可以使用Beacon信号,提交唤醒请求。

4SMCLK和SMDAT信号

SMCLK和SMDAT信号与x86处理器的SMBus(System Mangement Bus)相关。SMBus于1995年由Intel提出,SMBus由SMCLK和SMDAT信号组成。SMBus源于I2C总线,但是与I2C总线存在一些差异。

SMBus的最高总线频率为100KHz,而I2C总线可以支持400KHz和2MHz的总线频率。此外SMBus上的从设备具有超时功能,当从设备发现主设备发出的时钟信号保持低电平超过35ms时,将引发从设备的超时复位。在正常情况下,SMBus的主设备使用的总线频率最低为10KHz,以避免从设备在正常使用过程中出现超时。

在SMbus中,如果主设备需要复位从设备时,可以使用这种超时机制。而I2C总线只能使用硬件信号才能实现这种复位操作,在I2C总线中,如果从设备出现错误时,单纯通过主设备是无法复位从设备的。

SMBus在x86处理器系统中得到了大规模普及,其主要作用是管理处理器系统的外部设备,并收集外设的运行信息,特别是一些与智能电源管理相关的信息。PCI和PCIe插槽也为SMBus预留了接口,以便于PCI/PCIe设备与处理器系统进行交互。

5JTAG信号

JTAG(Joint Test Action Group)是一种国际标准测试协议,与IEEE 1149.1兼容,主要用于芯片内部测试。目前绝大多数器件都支持JTAG测试标准。JTAG信号由TRST#、TCK、TDI、TDO和TMS信号组成。其中TRST#为复位信号;TCK为时钟信号;TDI和TDO分别与数据输入和数据输出对应;而TMS信号为模式选择。

JTAG允许多个器件通过JTAG接口串联在一起,并形成一个JTAG链。目前FPGA和EPLD可以借用JTAG接口实现在线编程ISP(In-System Programming)功能。处理器也可以使用JTAG接口进行系统级调试工作,如设置断点、读取内部寄存器和存储器等一系列操作。除此之外JTAG接口也可用作“逆向工程”,分析一个产品的实现细节,因此在正式产品中,一般不保留JTAG接口。

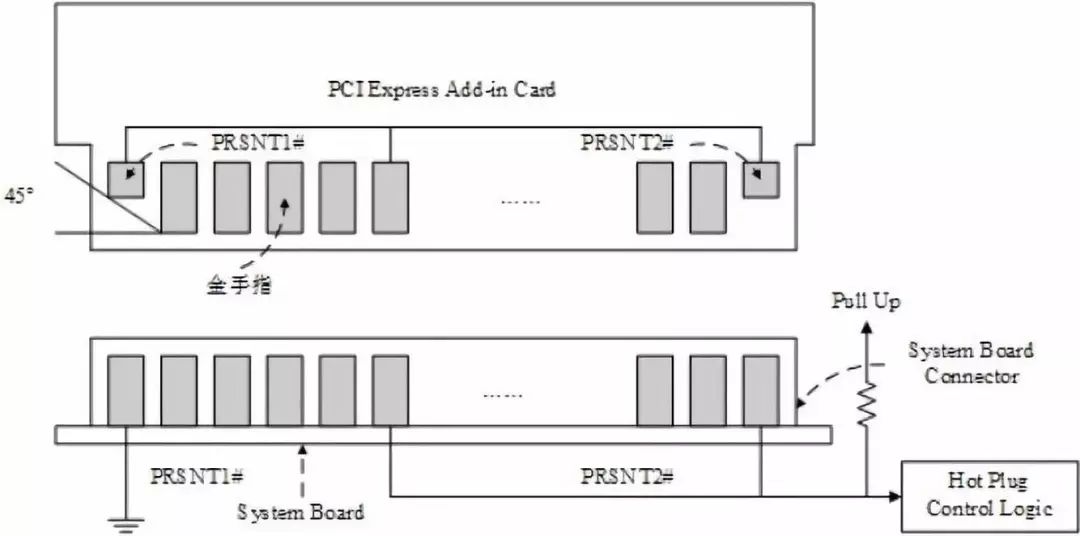

6PRSNT1#和PRSNT2#信号

PRSNT1#和PRSNT2#信号与PCIe设备的热插拔相关。在基于PCIe总线的Add-in卡中,PRSNT1#和PRSNT2#信号直接相连,而在处理器主板中,PRSNT1#信号接地,而PRSNT2#信号通过上拉电阻接为高。PCIe设备的热插拔结构如下图所示。

PCIE设备的热插拔

如上图所示,当Add-In卡没有插入时,处理器主板的PRSNT2#信号由上拉电阻接为高,而当Add-In卡插入时主板的PRSNT2#信号将与PRSNT1#信号通过Add-In卡连通,此时PRSNT2#信号为低。处理器主板的热插拔控制逻辑将捕获这个“低电平”,得知Add-In卡已经插入,从而触发系统软件进行相应地处理。

Add-In卡拔出的工作机制与插入类似。当Add-in卡连接在处理器主板时,处理器主板的PRSNT2#信号为低,当Add-In卡拔出后,处理器主板的PRSNT2#信号为高。处理器主板的热插拔控制逻辑将捕获这个“高电平”,得知Add-In卡已经被拔出,从而触发系统软件进行相应地处理。

不同的处理器系统处理PCIe设备热拔插的过程并不相同,在一个实际的处理器系统中,热拔插设备的实现也远比图43中的示例复杂得多。值得注意的是,在实现热拔插功能时,Add-in Card需要使用“长短针”结构。

如上图所示,PRSNT1#和PRSNT2#信号使用的金手指长度是其他信号的一半。因此当PCIe设备插入插槽时,PRSNT1#和PRSNT2#信号在其他金手指与PCIe插槽完全接触,并经过一段延时后,才能与插槽完全接触;当PCIe设备从PCIe插槽中拔出时,这两个信号首先与PCIe插槽断连,再经过一段延时后,其他信号才能与插槽断连。系统软件可以使用这段延时,进行一些热拔插处理。

以上信号中,REFCLK-/REFCLK+ 差分信号;PERST复位信号;WAKE#信号;PRSNT1#和PRSNT2#信号;这些信号是必须存在的。

SMCLK;SMDAT;JTAG(TRST#、TCK、TDI、TDO、TMS);这些是扩展功能,可有可无。

下图为PCIE插槽的管脚信号排布。

PCIE管脚信号排布

好啦,以上就是凡亿为大家整理的关于PCIE总线的知识,凡亿PCB将持续为你带来更多精彩的PCB设计专业知识。

-

rtthread编译后如何查看堆栈空间使用情况?2024-03-05 0

-

CUBEIDE运行完可以看RAM的使用情况,运行中可以实时查看RAM的使用情况吗?2024-03-12 0

-

linux的系统内存使用情况查看2019-07-15 0

-

如何查看RAM使用情况?2019-08-05 0

-

Android应用的内存使用情况检查方法2020-03-30 0

-

ucosiii堆栈使用情况检测使用率100%?2020-04-20 0

-

电池使用情况统计信息2021-12-31 0

-

SoC如何查看内存使用情况2023-09-19 0

-

主流GPS芯片使用情况2017-11-27 3705

-

单片机整体的CPU使用情况详细介绍2020-11-25 980

-

STM32/KEIL/MDK 查看 FLASH 和 RAM 使用情况2021-12-02 1028

-

Windows查看电源使用情况2022-01-05 2019

-

LPC86x上的开关矩阵使用情况2023-08-17 239

-

LPC86x ACMP使用情况2023-08-17 279

-

LPC86x ADC使用情况2023-08-16 238

全部0条评论

快来发表一下你的评论吧 !