FPGA内部可编程逻辑CLB资源分析

电子说

描述

一. 概述

这里以7系列的FPGA为例,先从整体上去了解一下FPGA内部可编程逻辑资源的结构。了解FPGA器件的内部资源与结构有利于我们优化设计与评估设计资源。

现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。下图是一个抽象的结构图,相同资源以列方式排布。这篇文章主要讲解CLB资源。

二. CLB资源介绍

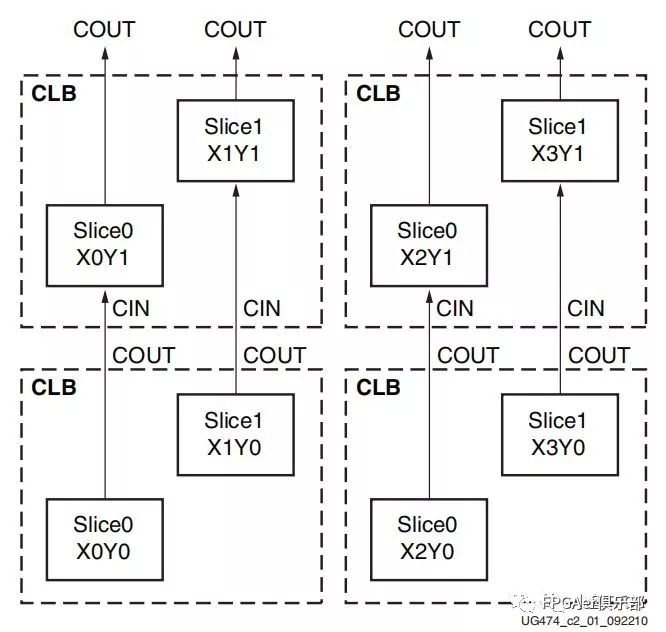

CLB资源的分布以纵向相连,如下图所示。每个CLB由两个Slice组成。同一个CLB里面的两个Slice之间没有互连线。

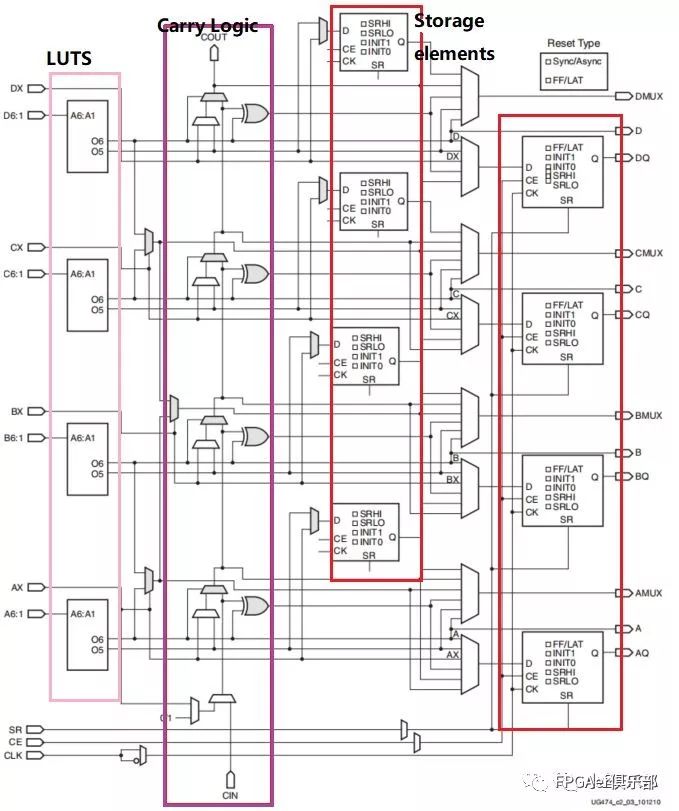

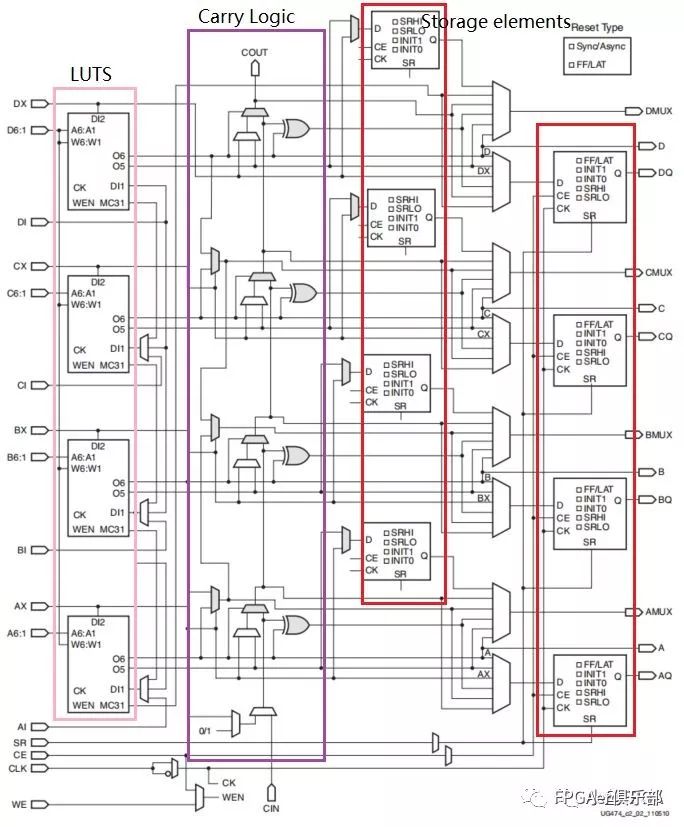

每个Slice里面有4个6输入的LUT(look-up tables(查找表))和8个存储单元(Storage)以及进位逻辑(Carry Logic)和多路选择器(Multiplexers)。同时Slice有两种。

普通的Slice叫SLICEL,威廉希尔官方网站 结构如下,最左边一列就是4个LUT,第二列为Carry Logic,以及红色框框出来的存器单元。

第二种Slice叫SLICEM,威廉希尔官方网站 结构如下。除了LUTS与SLICEL的LUTS不同之外,其余结构都一样。这就是SLICEM与SLICEL之间的区别,利用SLICEM的LUTS还可以构成RAM,ROM,以及Shift Registers(移位寄存器)。

一个CLB里面含有一个SLICEM和SLICEL或者含有两个SLICEL。

Slice就是通过LUTS以及Carry Logic和Multiplexers之间的互连来形成组合逻辑,再通过Storage elements构成寄存器以形成时序逻辑。

同时借助SLICEM的LUTS,还可以构成RAM,ROM,Shift Registers资源。

下表是一个CLB可以拥有的资源数以及可以形成大小为多少的RAM与Shift Registers。我们可以借助这些信息去评估设计需要多少资源和选择什么型号的FPGA器件。

-

什么是可编程逻辑2009-05-29 0

-

可编程逻辑器件2014-04-15 0

-

什么是PLD(可编程逻辑器件)2009-06-20 26248

-

可编程逻辑器件FPGA/CPLD结构与应用2016-12-11 765

-

基于FPGA进行可编程逻辑设计2017-09-12 891

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 908

-

关于可编程逻辑推动基于MCU的设计的分析和应用2019-08-28 2985

-

FPGA面向汽车电子的可编程逻辑解决方案2021-01-20 818

-

可编程逻辑阵列fpga和cpld说明2021-03-30 881

-

FPGA CPLD可编程逻辑器件的在系统配置方法2021-09-18 788

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 2841

-

fpga是什么架构2024-03-14 922

-

现场可编程门阵列是什么2024-03-16 2462

-

现场可编程门阵列简介2024-03-27 550

-

现场可编程门阵列的原理和应用2024-03-27 689

全部0条评论

快来发表一下你的评论吧 !