深度解析ug1292:降低布线延迟

电子说

描述

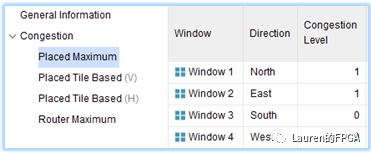

当设计出现布线拥塞时,通常会导致布线延迟增大,从而影响时序收敛。布线拥塞程度可通过如下两种方式获取:

-布线阶段的log文件中会显示拥塞程度

-对于place_design或route_design生成的dcp文件,可通过如下命令获取

生成的拥塞报告如下图所示。要格外关注拥塞程度(Congestion Level)大于4的区域。

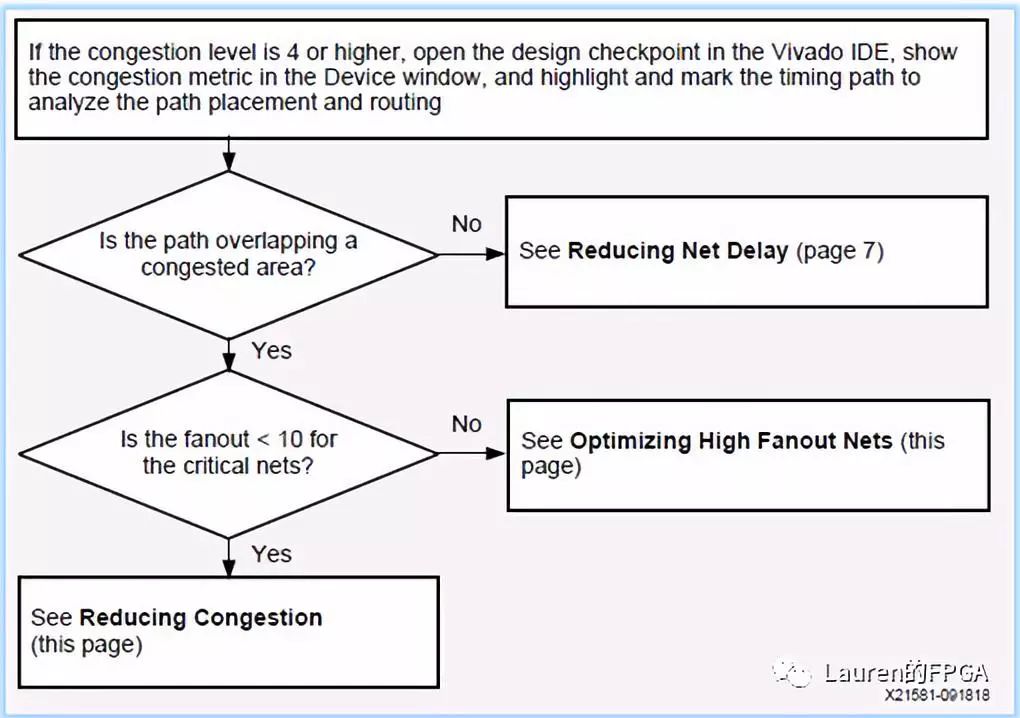

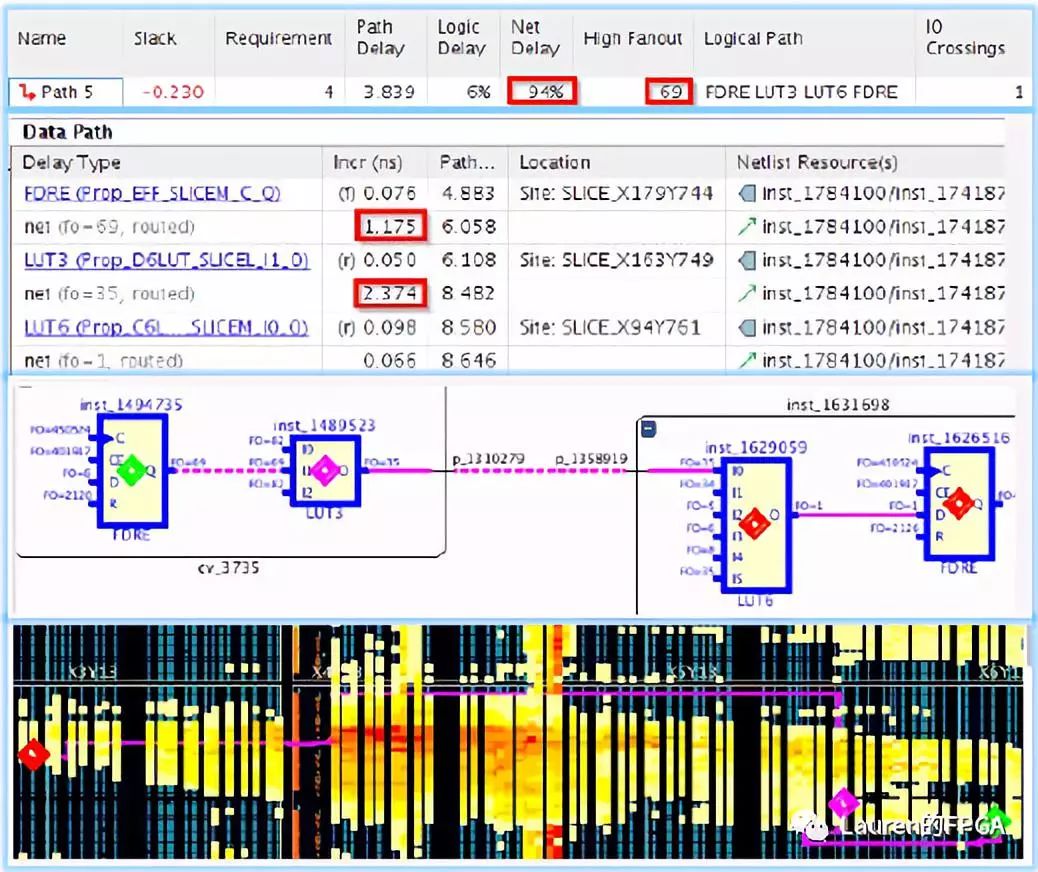

对于拥塞程度大于4的情形,可采用如下流程加以改善并降低布线延迟。在如下的案例中,可以看到布线延迟占到了总延迟的94%,据此,可断定布线延迟是导致时序违例的根本原因。从布线结果看,在拥塞区域出现了绕线。

图片来源:page 6, ug1292

图片来源:page 6, ug1292

降低拥塞程度可改善布线质量。Xilinx建议采用如下方法以改善布线拥塞。

(1)当整体资源利用率达到70%~80%时(对于多die芯片,这个数值是指每个SLR的资源利用率),需要砍掉一些模块以降低资源利用率。尤其要避免LUT/BRAM/DSP/URAM利用率同时出现大于80%的情形。如果BRAM/DSP/URAM这些Block利用率无法降低,那么要确保LUT利用率低于60%。

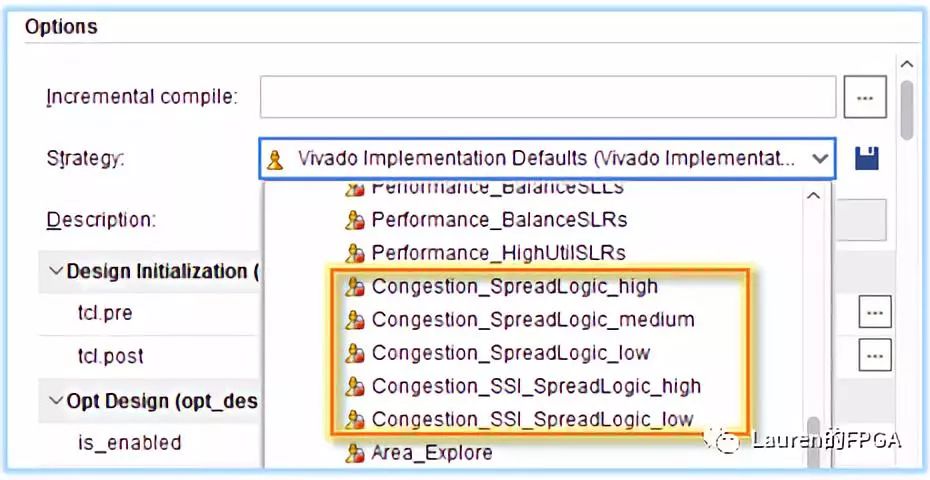

(2)执行place_design时,尝试将-directive设置为AltSpreadLogic*或SSI_Spread*或将Implementation的策略设置为Congestion_*,如下图所示。

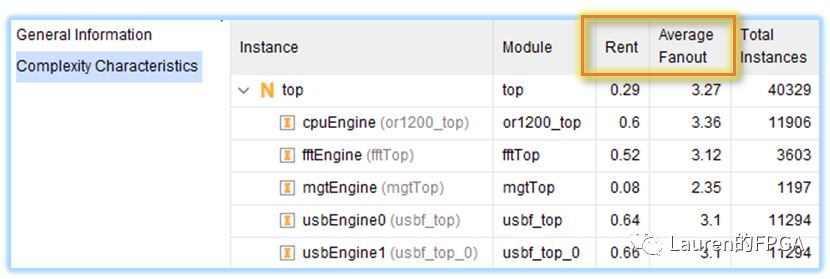

(3)通过如下命令分析设计复杂度,找到设计中出现拥塞的模块(Rent值大于0.65或AverageFanout大于4)。之后,对这些模块实施模块化综合,其中的综合策略设置为ALTERNATE_ROUTABILITY。

生成设计复杂度报告:

对拥塞模块采用模块化综合技术:

(4)降低拥塞区域MUXF*和LUT-Combining的使用率,具体方法有时可通过report_qor_suggestions获得。但采用模块化综合技术是一个值得一试的方法。

(5)在布线区域内非关键的高扇出网线上引入BUFG,可通过如下命令实现。

(6)从之前低拥塞的布线或布局结果中继承DSP/BRAM/URAM的布局。这可通过如下脚本实现。

优化高扇出网线:

(1)在RTL层面,基于设计层次复制寄存器降低扇出,或者在opt_design阶段通过-hier_fanout_limit选项降低扇出。

(2)在phys_opt_design(布局之后)阶段通过-force_replication_on_nets对关键的高扇出网线通过复制寄存器降低扇出。

-

深度解析降低EMI的办法2018-06-11 0

-

怎么降低延迟?2018-10-29 0

-

AUTOSAR架构深度解析 精选资料推荐2021-07-28 0

-

C语言深度解析2023-09-28 0

-

LM1292 pdf,LM1292 datasheet2008-09-17 1487

-

综合布线常用术语解析2010-04-14 749

-

ug1292时序收敛快速参考手册2018-10-09 3388

-

ug1292深度解析2018-10-12 3659

-

深度解析ug1292建立时间违例分析流程2018-10-19 5539

-

浅谈ug1292中的降低逻辑延迟的解决方案2018-10-27 7169

-

UG1292使用之初始设计检查使用说明2018-10-30 3391

-

DC1292A-设计文件2021-04-12 281

-

DC1292A DC1292A评估板2021-09-03 83

-

AD1292R芯片手册2023-04-07 391

-

UltraFast设计方法时序收敛快捷参考指南(UG1292)2023-09-15 203

全部0条评论

快来发表一下你的评论吧 !