嵌入式逻辑分析仪的工作原理以及应用解析

嵌入式技术

描述

逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,最主要作用在于时序判定。由于逻辑分析仪不像示波器那样有许多电压等级,通常只显示两个电压(逻辑1和0),因此设定了参考电压后,逻辑分析仪将被测信号通过比较器进行判定,高于参考电压者为High,低于参考电压者为Low,在High与Low之间形成数字波形。逻辑分析仪与示波器相同,是通过采集指定的信号,并通过图形化的方式展示给开发人员,开发人员根据这些图形化信号按照协议分析出是否出错。尽管图形化的显示已经给开发人员带来不少的方便,但是人工将一串串信号分析出来不仅麻烦而且极易出错。在这个科技高速发展的社会,一切都在追求高效率。自动化、智能化已经成为协议分析的发展方向。在这个思想的指引下各种测试仪器的协议分析功能出现并发展起来。目前大多数开发人员通过逻辑分析仪等测试工具的协议分析功能可以很轻松的发现错误、调试硬件、加快开发进度,为高速度、高质量完成工程提供保障。逻辑分析仪的工作过程就是数据采集、存储、触发、显示的过程,由于它采用数字存储技术,可将数据采集工作和显示工作分开进行,也可同时进行,必要时,对存储的数据可以反复进行显示,以利于对问题的分析和研究。

ELA的工作原理及特点

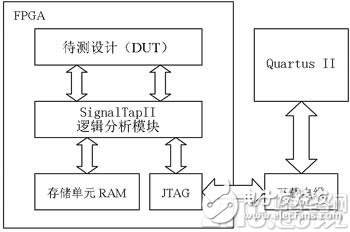

一个嵌入式系统装置一般都由嵌入式计算机系统和执行装置组成,嵌入式计算机系统是整个嵌入式系统的核心,由硬件层、中间层、系统软件层和应用软件层组成。执行装置也称为被控对象,它可以接受嵌入式计算机系统发出的控制命令,执行所规定的操作或任务。执行装置可以很简单,如手机上的一个微小型的电机,当手机处于震动接收状态时打开;也可以很复杂,如SONY智能机器狗,上面集成了多个微小型控制电机和多种传感器,从而可以执行各种复杂的动作和感受各种状态信息。嵌入式逻辑分析仪的组成框图如图1所示,主要分为硬件部分和软件部分。硬件部分由待测设计(DUT)、嵌入到FPGA中的ELA IP核、RAM存储单元以及JTAG接口组成;软件部分由用户设计软件和集成在其中的ELA在线调试软件组成。ELA的工作原理为:设置ELA在线调试软件中需要监测的信号、触发逻辑、采样深度和时钟信号等各项参数;把设置好的ELA文件与用户设计编译综合后一起下载到FPGA中;运行ELA,如果满足触发条件,ELA就在时钟的上升沿对被测信号采样,并储存在RAM存储单元中。

图1嵌入式逻辑分析仪的组成框图

嵌入式逻辑分析仪能够方便地对设计进行在线调试,及时发现系统内部所存在的问题,无须对设计文件进行任何修改就可以得到内部节点或者I/O引脚的状态。例如,SignalTap II支持多达1024个通道,采样深度高达128Kb,时钟支持超过200MHz,每个分析仪均有10级触发输入/输出,从而增加了采样的精度。

ELA在FPGA测试中的应用

嵌入式逻辑分析仪在FPGA的测试中应用极为广泛,能够对系统实时监测。设计中所使用的FPGA芯片为Altera公司Cyclone系列中的EP1C12Q240C8,它支持SignalTap II,有12 060个逻辑单元,存储位的大小为239 616,能够较好的支持各种复杂的设计。

ELA的应用设计流程如下。

1 Stp文件的创建

在交通灯控制器的设计完成并编译综合后,即可创建一个SignalTap II文件(stp文件)。通常有两种方式来建立stp文件,一是直接建立stp文件,并利用SignalTap II Editor配置逻辑分析仪的各项参数;二是利用MegaWizard Plug-in Manager生成和配置stp文件。如图2所示。

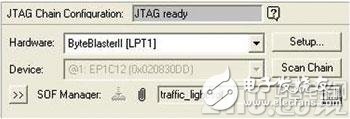

图2 Stp文件的载入

2 ELA的设置

将stp文件加入到设计中后,就可以对其进行设置,流程如下。

①添加被测信号。通过Node Finder中的SignalTap II Filter查找设计中所有预综合和布局布线后的信号,选择需要观察的信号,在本设计中,可以全部选定。

②设置采样时钟。在设置采样时钟时,可以使用其中任何一个信号作为采样时钟,但不能用布局布线后的信号,为获得更准确的采样数据,采样时钟应选择全局时钟。

③确定采样深度。SignalTap II的采样深度最大可达128Kb.在选择采样深度时,必须考虑到FPGA的内存大小,此处选择1Kb的采样深度。

④设置缓冲获得模式。通过设置缓冲获得模式,用户可以指定在SignalTap II触发前和触发后所捕获的数据量,缓冲获得模式主要有环形模式和分段缓冲模式。在此选择环形模式的预触发位置。

⑤设置触发条件。SignalTap II支持基本触发和高级触发的功能。在基本触发中,它支持10级触发级数,对于每一级触发,可以根据设计的需要设置不同的触发电平。

本设计对SignalTap II的设置如图3所示,其中采样深度为1Kb,缓冲获得模式选择环形模式的预触发位置,触发条件为基本触发;此外,采样时钟选择为全局时钟。这些设置能够准确地对本设计进行在线调试,有效地监测内部信号。

图3 SignalTap II设置窗口

3设计下载

当设置完stp文件并编译综合后,软件将ELA IP嵌入设计里面,同设计一起下载到FPGA中。在器件列表中,逻辑分析仪会自动探测编程硬件,如果在保存设计前已经选好了FPGA中所使用的芯片,就会自动给出已经选好的器件,若没有选择,则需要在器件列表中选择。当器件连接成功,在SOF(SRAM Object File)管理器中选择需要下载的SOF文件,单击下载按钮即可将设计下载到FPGA中,如图4所示。

图4设计下载窗口

4在线调试

在线调试即利用JTAG接口将数据上传到调试软件中,根据实时运行的结果来对设计进行调试。本设计所实现的功能是在时钟信号的控制下,根据当前的状态决定下一个时钟周期的输出,即红灯、绿灯和黄灯的开启。

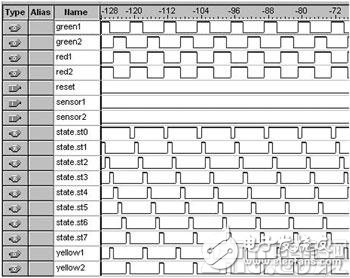

图5 SignalTap II数据窗的实时监测信号

设计中所得到的波形如图5所示,从图5中可以看出,对于第一组灯,在state.st3时,黄灯开启,绿灯及红灯都关闭,一个时钟周期后,跳转到state.st4,黄灯关闭,同时红灯开启;四个时钟周期后,跳转到state.st0,红灯关闭,同时绿灯开启,黄灯继续关闭;三个时钟周期后,再次跳转到state.st3,黄灯开启,绿灯关闭;一个时钟周期后,跳转到state.st4,黄灯关闭,红灯开启。对于第二组,其红绿灯的转换也是一样的不断循环,这样就实现了红绿黄灯的交替变化。

在线调试得到的波形与交通灯控制器设计中所要求的功能完全吻合,在上述调试过程中,嵌入式逻辑分析仪对内部的8个状态能够很好的监测,保证了设计的正确。

在调试过程中,用户可以很方便的开始或暂停ELA,对内部信号进行分析。如果需要修改设置,如采样深度或触发条件,只需停止运行ELA,完成修改后重新编译综合即可,缩短了调试时间。

-

第10章 SignalTapⅡ嵌入式逻辑分析仪的使用 96页 1.9M2016-09-27 0

-

逻辑分析仪工作原理2018-04-02 0

-

如何利用最新的逻辑分析仪解决复杂高速嵌入式系统的棘手问题?2021-04-14 0

-

为什么嵌入式逻辑分析仪可以加速SoPC设计?2021-04-26 0

-

逻辑分析仪的应用分析2008-11-27 960

-

使用逻辑分析仪调试定时问题2010-08-06 419

-

嵌入式逻辑分析仪在FPGA设计中的应用2010-08-06 367

-

逻辑分析仪的工作原理2008-11-27 3265

-

基于NiosⅡ的嵌入式高速逻辑分析仪2009-10-06 831

-

嵌入式逻辑分析仪在FPGA测试中的应用2011-03-15 819

-

逻辑分析仪在嵌入式开发调试中的应用2011-11-07 604

-

逻辑分析仪的工作原理和结构2020-07-10 1535

-

业界首款:嵌入式接口逻辑分析仪PGY-LA-EMBD2020-11-12 2177

-

逻辑分析仪如何使用 逻辑分析仪使用教程2023-09-19 2927

全部0条评论

快来发表一下你的评论吧 !