用于完善智能电表设计的FPGA到ASIC研究

嵌入式技术

描述

许多嵌入式系统设计首先使用 FPGA 来实现。这可能是为了更快地进行原型设计或提供软件开发平台。有时,生产开始后,FPGA 仍保留在设计中。但通常情况下,计划是将 FPGA(或多个 FPGA)转换为 ASIC 以进行批量制造。

人们很容易认为这种转换几乎是自动的。只需使用 ASIC 库重新编译经过验证的 FPGA RTL 代码,验证生成的网表,然后将文件发送到后端设计车间。但要获得结果,过程可能没那么简单,特别是如果有机会将多个芯片整合到 ASIC 中或需要混合信号功能时。

近,智原科技参与了这样一个智能电表的FPGA到ASIC转换项目。该设计说明了转换过程中的许多重要细微差别。这表明寻找合适的转化合作伙伴的重要性。

智能电表设计

乍一看,电表很简单。它监控客户场所入口处的电力线电压和电流,并记录输送的累积能量(在美国通常以千瓦小时为单位)。传统上,这项任务是由相当聪明的电动机驱动机械计数器来完成的。

但智能电表则不同。智能电表消除了机电移动部件,对电压和电流进行采样并以数字方式累加它们的乘积。它还提供了一种远程阅读的方式,消除了人们拿着铅笔和剪贴板挨家挨户走动的情况。在我们正在讨论的设计中,还有其他功能,例如如果电表检测到异常电压或电流事件,则切断客户驻地的电源并向网络控制中心故障。

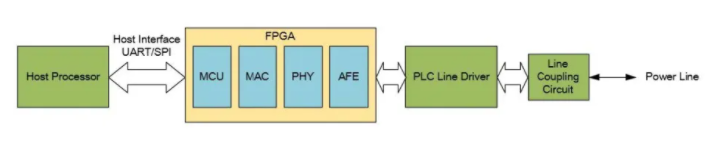

由于智能电表的大部分功能都在软件中,因此硬件相对简单,且大多与I/O相关(图1)。在客户的原型中,硬件包括主机处理器、充当 I/O 集线器的 FPGA、各种传感器、主要通过串行接口连接的显示器,以及用于返回网络的电力线通信 (PLC) 的子系统控制中心。后一个元素被证明是设计的重要组成部分。

图 1客户的初始设计包括 FPGA 和外部主机 CPU。实现 EMI 和 ESD 合规性是整个设计过程中关注的一个问题。智原科技

PLC 接口需要独特的媒体访问控制器 (MAC)、物理层接口 (PHY) 和模拟前端 (AFE)。在原型设计中,所有这些功能都在FPGA中实现。然而,PLC 接口还需要外部线路驱动器和电源线耦合器。

FPGA 到 ASIC 转换的主要目标是降低成本,部分是通过消除一些外部组件来实现的。然而,在具有挑战性的使用环境中满足静电放电 (ESD) 和电磁干扰 (EMI) 抗扰度规范的需求(对于基于 FPGA 的 AFE 来说是一个真正的难题)也给设计团队带来了沉重的压力。

转换过程

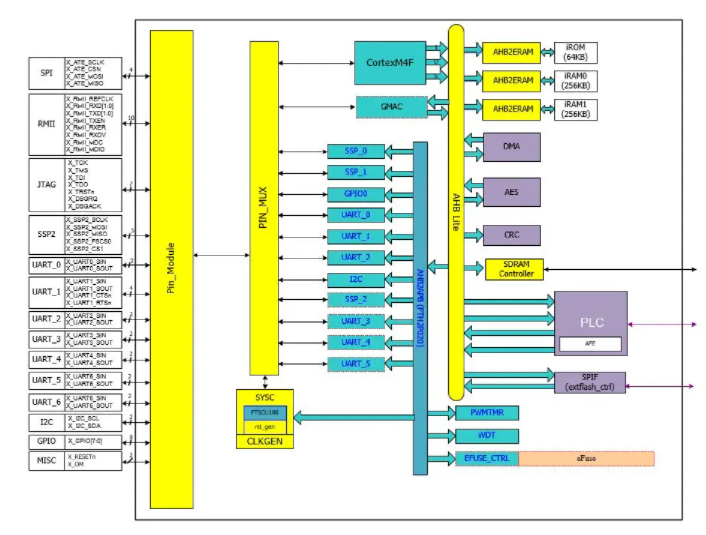

FPGA 到 ASIC 的转换过程远非自动化,而是涉及设计服务公司和客户之间的大量交互。结果是基于 ARM 的混合信号 ASIC 设计减少了芯片数量(图 2)。

图 2 ASIC 设计包括内部 CPU、外部控制信号的复杂复用以及电力线通信接口的模拟前端。智原科技

法拉第首先评估智能电表架构。我们决定,除了实现 FPGA 作为 I/O 集线器和 PLC 接口的现有功能外,ASIC 还可以承担主处理器的功能。这导致了基于 ARM Cortex-M4F CPU 内核、AHB-Lite 系统总线和 ARM 外设总线的相当传统的架构。

系统总线将接口连接到内部存储器以及主要子系统。其中包括千兆位 MAC、DMA 控制器,以及 CRC 控制器和 AES 加密引擎(因为数据完整性和安全性对此应用至关重要)。

大量的 I/O 引脚通过复用连接到外设总线。该设计包括用于 CPU 的内部 ROM 和 SRAM、内部电子保险丝及其控制器,以及用于外部 SDRAM 和串行闪存的接口。

汇聚IP

智原与客户共同选择和配置 ASIC IP。这样就可以简单地用 Faraday、ARM 或第三方 ASIC IP 模块替换 FPGA 中的许多模块。剩余的 HDL 逻辑被转换为 ASIC,Faraday 用等效的 ASIC IP 替换了 FPGA 锁相环、SRAM 和 I/O 实例。

PLC 接口对于转换过程至关重要,尤其是将模拟前端集成到 ASIC 中。这是一项具有挑战性的模拟设计,因为不存在可以明显满足严格的 ESD 和 EMI 要求的现成 IP。因此,法拉第模拟设计团队决定为该模块创建新的设计。

Faraday 执行了 SoC 和时钟分配的终集成以及基本功能验证,以确保所有部件正常工作并相互通信。客户进行了应用程序驱动的验证和软件集成。法拉第随后进行了物理设计和签核验证。

再次,在验证过程中,PLC 接口是一个特例。确保 ESD/EMI 合规性的方法是将物理芯片放在测试台上。我们没有把赌注押在整个生产运行上,而是决定对 AFE 进行测试芯片,并将其放在穿梭运行中,以实现晶圆厂的快速周转。

智原与客户约定,如果测试芯片通过合规性测试,客户将支付测试芯片的费用。如果设计失败,法拉第将纠正设计,并为纠正后的测试芯片提供班车。尽管如此,初的测试芯片还是通过了,这让客户大大放心了。

全面的合作

Faraday 现在向客户批量提供成品、组装和测试的 SoC。

这种智能电表设计表明,FPGA 到 ASIC 的转换不是一个按钮过程,也不是一种发送文件后就忘记的合同关系。特别是当存在独特的功能块、特殊的电气要求或将多个芯片整合到一个 ASIC 中的机会时,该过程成为客户和设计服务公司之间的密切合作。

成功的步是仔细评估设计服务公司的技术、IP 访问、经验以及与客户设计团队一对一合作的意愿。这些因素中的每一个都会对关系的结果产生影响,就像这个智能电表一样。

-

ASIC到FPGA的原型验证代码转换技术2011-03-25 1156

-

到底什么是ASIC和FPGA?2024-01-23 0

-

智能电表的陷阱2010-04-22 0

-

从ASIC到FPGA的转换系统时钟设计方案2011-03-02 0

-

cogoask讲解fpga和ASIC是什么意思2012-02-27 0

-

人工智能实现的流派 FPGA vs. ASIC看好谁?2016-12-23 0

-

PTC用于智能电表的保护应用2017-08-01 0

-

智能电表市场2018-10-18 0

-

ASIC到FPGA的代码是怎样进行转换的?2021-05-08 0

-

从FPGA到ASIC,异曲同工还是南辕北辙?2023-03-28 0

-

面向ASIC和FPGA设计的多点综合技术2009-12-26 643

-

ASIC和FPGA的优势与劣势2011-03-31 5633

-

什么是FPGA原型验证?如何用FPGA对ASIC进行原型验证2023-04-10 1514

-

FPGA和ASIC的区别与联系2023-08-14 3210

-

智能电表如何选型? 如何选到合适的电表?2024-11-29 205

全部0条评论

快来发表一下你的评论吧 !