卫星导航系统基带伪码完整系统解决方案

嵌入式设计应用

描述

项目背景及可行性分析

1.项目名称、项目的主要内容及目前的进展情况

项目名称:卫星导航系统基带伪码的频域快捕获;

项目的主要内容:利用FPGA设计实现GNSS信号的频域快速捕获算法。

目前的进展情况:拥有成熟的算法结构和仿真测试结果,开始着手相关模块的实现。

2.项目关键技术及创新点的论述

创新点(1):基于FFT,在频域计算伪码序列的循环相关值。在每一个多普勒频移,对所有码延迟同时计算出相关结果。和传统的直接计算本地与接收信号相关值的方法相比,运算时间短。对C/A码来说,只需接收到一个伪码周期(1ms)的信号,就可估计出码相位;传统的串行相关,每次最多移动半个码片,完成一次相关运算,搜索整个码周期需要最少移动 2046次。

创新点(2):FFT运算要求满足所用数据的个数为2的整数次幂,一般情况下A/D不能满足在一个码周期内采样点数符合2的整数次幂。本项目通过一种平均下采样技术,来完成数据的匹配。

创新点(3):采样数据为一个码周期时,通过处理单边带数据的办法可以减少一半的运算量。虽然通过IFFT后只能找到前一半的点,但这些点包含了几乎全部信息。

关键技术(1):FFT的实现

关键技术(2):平均下采样完成数据匹配

3.技术成熟性和可靠性论述

目前通过MATLAB在通用PC机上完成该算法,证明该算法不仅可以有效地捕获到卫星导航信号,而且速度较传统的方法相比有很大提高,在一定程度上降低计算的工作量和复杂度。

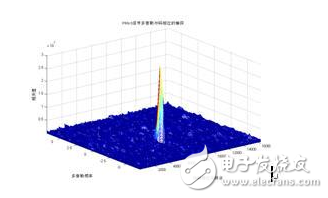

下图为实际卫星捕获结果示意图:

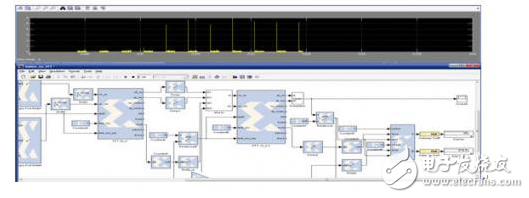

为了能够实现算法在FPGA平台的顺利移植,利用System Generator在Simulink下的进行了部分硬件协同仿真工作。开发板为合众达公司的seed-fem025,FPGA芯片为Virtex-4 SX25。由于整套系统硬件协同仿真所需的硬件资源不足,所以硬件协同仿真分模块进行。

软件仿真的结果如下图:

团队成员均有比较扎实的数字威廉希尔官方网站 基础知识和FPGA设计功底,以及信号处理方面的专业知识,完全有能力保证该项目的顺利实施,最终完成项目。同时团队成员依托于哈尔滨工业大学通信技术研究所卫星导航技实验室,利用实验室的各种硬件资源,作为项目的物质保证;通信技术研究所早在10年以前就开始了对卫星导航技术的研究,积累了大量成熟的技术。

另外Virtex5系列的FPGA具有丰富的硬件资源,便于实现数字信号处理功能,可以有效地实现大规模的FFT运算,能够实现实时的频域捕获。

项目实施方案

1.方案基本功能框图及描述

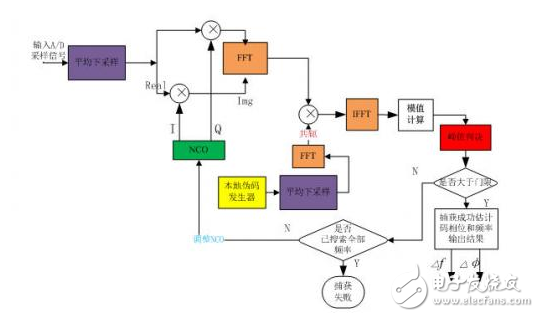

该方案利用FFT,在频域完成接收信号与本地信号的循环相关运算,因此同时计算出所有码相位的相关值,估计接收信号的码相位延迟。

具体过程如下:

(1)中频信号采样后经过数字下变频,经过平均下采样,整合数据,匹配运算点数的要求。将匹配的数据交给FFT模块。其中I、Q两支路分别作为FFT的实部和虚部进行复数FFT运算。

(2)在FFT单元中,对进来的数据做分段处理,分段的长度L就决定一次并行运算的长度,与捕获概率、捕获时间有很大的关系。

(3)对本地产生的扩频码,同样进行平均下采样数据匹配后进行FFT运算,并取其复共轭。

(4)把数据段和地址段的FFT结果相乘,然后进行IFFT运算。

(5)对IFFT的结果取模值,存储结果。

(6)对结果进行捕获判决,找出累加后一帧中最大点与设定的门限比较,如果高于门限值,进行一次捕获检验。

(7)如果低于门限,调整NCO调整频率,重复上面的步骤

2.需要的开发平台

所需开发平台为XUPV5-LX110T,因为用频域捕获算法需要大点数的FFT变换支持。

3.方案实施过程中需要开发的模块

本方案进行的频域捕获主要分为,顶层模块,下采样模块、FFT模块、PRN序列产生模块、复数乘法器模块、NCO模块、峰值判决模块、频率搜索模块。

4.系统最终要达到的性能指标

在SNR为-19dB的条件下,捕获伪码序列,码相位的估计结果在0.5个码片范围内,以满足后续跟踪模块的启动条件。

需要的其它资源

1.测试设备

在方案实施过程中,需要Xilinx内嵌的逻辑分析仪;思博伦的导航卫星信号源;Simulink以及System generator。

2.仿真、开发工具

ISE集成平台,Matlab和simulink,System generator,Synplify Pro综合工具,以及仿真工具Modelsim。

-

全球四大卫星定位系统#导航系统 #gps导航系统#北斗导航系统#风雷仪表 2023-10-27

-

瑞萨车载导航系统解决方案2015-01-09 0

-

什么是北斗卫星导航系统?2019-08-23 0

-

全球卫星定位导航系统由什么组成?2019-09-29 0

-

什么是汽车的导航系统2010-03-12 625

-

汽车导航系统解决方案2016-11-23 1019

-

盘点北斗卫星导航系统在各行业的应用2018-09-03 28179

-

全球卫星导航系统的IP解决方案2018-11-21 4360

-

北斗卫星导航系统全球组网今年将完成2020-02-24 3049

-

北斗卫星导航系统的发展近况2020-11-17 6077

-

浅谈北斗三号卫星导航系统2021-03-26 1534

-

北斗卫星导航系统再立新功!2021-01-28 3003

-

卫星导航系统与LoRa无线通信如何相互结合2022-01-27 2230

-

北斗系统助农民颗粒归仓 北斗卫星导航系统助力智慧农业2022-06-21 4474

-

北斗三号卫星导航系统采用了哪些先进技术,你知道吗?2024-01-16 1114

全部0条评论

快来发表一下你的评论吧 !