dma控制器的基本功能(控制原理及结构组成)

控制/MCU

描述

DMA控制简介

DMA(Direct Memory Access)控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。它之所以属于外设,是因为它是在处理器的编程控制下来 执行传输的。

DMA控制器结构

一般而言,DMA控制器将包括一条地址总线、一条数据总线和控制寄存器。高效率的DMA控制器将具有访问其所需要的任意资源的能力,而无须处理器本身的介入,它必须能产生中断。最后,它必须能在控制器内部计算出地址。

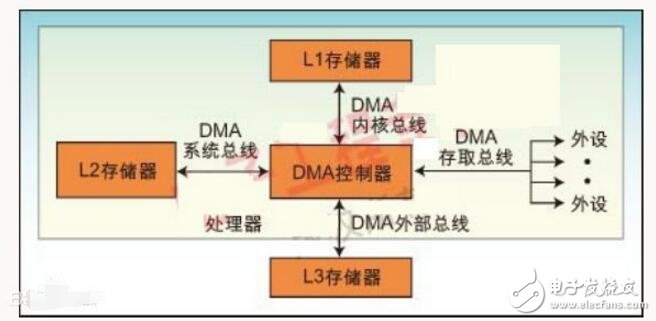

一个处理器可以包含多个DMA控制器。每个控制器有多个DMA通道,以及多条直接与存储器站(memory bank)和外设连接的总线,如图1所示。在很多高性能处理器中集成了两种类型的DMA控制器。第一类通常称为“系统DMA控制器”,可以实现对任何资源(外设和存储器)的访问,对于这种类型的控制器来说,信号周期数是以系统时钟(SCLK)来计数的,以ADI的Blackfin处理器为 例,频率最高可达133MHz。第二类称为内部存储器DMA控制器(IMDMA),专门用于内部存储器所处位置之间的相互存取操作。因为存取都发生在内部 (L1-L1、L1-L2,或者L2-L2),周期数的计数则以内核时钟(CCLK)为基准来进行,该时钟的速度可以超过600MHz。

每个DMA控制器有一组FIFO,起到DMA子系统和外设或存储器之间的缓冲器的作用。对于MemDMA(Memory DMA)来说,传输的源端和目标端都有一组FIFO存在。当资源紧张而不能完成数据传输的话,则FIFO可以提供数据的暂存区,从而提高性能。

因为你通常会在代码初始化过程中对DMA控制器进行配置,内核就只需要在数据传输完成后对中断做出响应即可。你可以对DMA控制进行编程,让其与内核并行地移动数据,而同时让内核执行其基本的处理任务—那些应该让它专注完成的工作。

DMA控制器基本组成

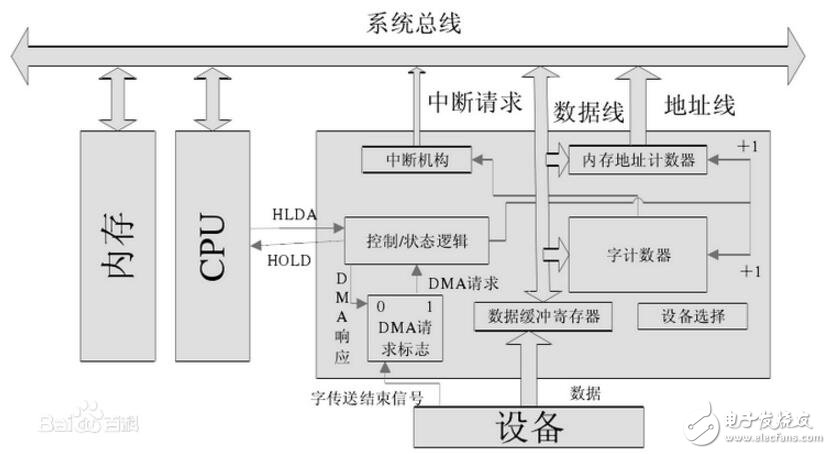

一个DMA控制器,实际上是采用DMA方式的外围设备与系统总线之间的接口威廉希尔官方网站 ,这个接口威廉希尔官方网站 是在中断接口的基础上再加DMA机构组成。习惯上将DMA方式的接口威廉希尔官方网站 称为DMA控制器。

(1)内存地址计数器:用于存放内存中要交换的数据的地址。在 DMA传送前,须通过程序将数据在内存中的起始位置(首地址)送到内存地址计数器。而当 DMA 传送时,每交换一次数据,将地址计数器加“1”,从而以增量方式给出内存中要交换的一批数据的地址。

(2)字计数器:用于记录传送数据块的长度(多少字数)。其内容也是在数据传送之前由程序预置,交换的字数通常以补码形式表示。在DMA传送时,每传送一个字,字计数器就加“1”。当计数器溢出即最高位产生进位时,表示这批数据传送完毕,于是引起DMA控制器向CPU发出中断信号。

(3)数据缓冲寄存器:用于暂存每次传送的数据(一个字)。当输入时,由设备(如磁盘)送往数据缓冲寄存器,再由缓冲寄存器通过数据总线送到内存。反之,输出时,由内存通过数据总线送到数据缓冲寄存器,然后再送到设备。

(4)DMA请求”标志:每当设备准备好一个数据字后给出一个控制信号,使“DMA请求”标志置“1”。该标志置位后向“控制/状态”逻辑发出DMA请求,后者又向CPU发出总线使用权的请求(HOLD),CPU响应此请求后发回响应信号HLDA,“控制/状态”逻辑接收此信号后发出DMA响应信号,使“DMA 请求”标志复位,为交换下一个字做好准备。

(5)控制/状态”逻辑:由控制和时序威廉希尔官方网站 以及状态标志等组成,用于修改内存地址计数器和字计数器,指定传送类型(输入或输出),并对“DMA请求”信号和CPU响应信号进行协调和同步。

(6)中断机构:当字计数器溢出时,意味着一组数据交换完毕,由溢出信号触发中断机构,向CPU提出中断报告。

DMA控制器设置

目前有两类主要的DMA传输结构:寄存器模式和描述符模式。无论属于哪一类DMA,表1的几种信息都会在DMA控制器中出现。当DMA以寄存器模式工作时,DMA控制器只是简单地利用寄存器中所存储的参数值。在描述符模式中,DMA控制器在存储器中查找自己的配置参数。

(1)基于寄存器的DMA

在基于寄存器的DMA内部,处理器直接对DMA控制寄存器进行编程,来启动传输。基于寄存器的DMA提供了最佳的DMA控制器性能,因为寄存器并不需要不断地从存储器中的描述符上载入数据,而内核也不需要保持描述符。基于寄存器的DMA由两种子模式组成:自动缓冲(Autobuffer)模式和停止模式。在自动缓冲DMA中,当一个传输块传输完毕,控制寄存器就自动重新载入其最初的设定值,同一个DMA进程重新启动,开销为零。如果将一个自动缓冲DMA设定为从外设传输一定数量的字到 L1数据存储器的缓冲器上,则DMA控制器将会在最后一个字传输完成的时刻就迅速重新载入初始的参数。这构成了一个“循环缓冲器”,因为当一个量值被写入 到缓冲器的最后一个位置上时,下一个值将被写入到缓冲器的第一个位置上。

自动缓冲DMA特别适合于对性能敏感的、存在持续数据流的应用。DMA控制器可以在独立于处理器其他活动的情况下读入数据流,然后在每次传输结束时,向内核发出中断。

停止模式的工作方式与自动缓冲DMA类似,区别在于各寄存器在DMA结束后不会重新载入,因 此整个DMA传输只发生一次。停止模式对于基于某种事件的一次性传输来说十分有用。例如,非定期地将数据块从一个位置转移到另一个位置。当你需要对事件进 行同步时,这种模式也非常有用。例如,如果一个任务必须在下一次传输前完成的话,则停止模式可以确保各事件发生的先后顺序。此外,停止模式对于缓冲器的初 始化来说非常有用。

(2)描述符模型

基于描述符(descriptor)的DMA要求在存储器中存入一组参数,以 启动DMA的系列操作。该描述符所包含的参数与那些通常通过编程写入DMA控制寄存器组的所有参数相同。不过,描述符还可以容许多个DMA操作序列串在一 起。在基于描述符的DMA操作中,我们可以对一个DMA通道进行编程,在当前的操作序列完成后,自动设置并启动另一次DMA传输。基于描述符的方式为管理 系统中的DMA传输提供了最大的灵活性。

DMA控制原理

DMA(Direct Memory Access,直接内存存取) 是所有现代电脑的重要特色,它允许不同速度的硬件装置来沟通,而不需要依于 CPU 的大量 中断 负载。否则,CPU 需要从 来源 把每一片段的资料复制到 暂存器,然后把它们再次写回到新的地方。在这个时间中,CPU 对于其他的工作来说就无法使用。

DMA 传输将数据从一个地址空间复制到另外一个地址空间。当 CPU 初始化这个传输动作,传输动作本身是由 DMA 控制器 来实行和完成。典型的例子就是移动一个外部内存的区块到芯片内部更快的内存区。像是这样的操作并没有让处理器工作拖延,反而可以被重新排程去处理其他的工作。DMA 传输对于高效能 嵌入式系统 算法和网络是很重要的。

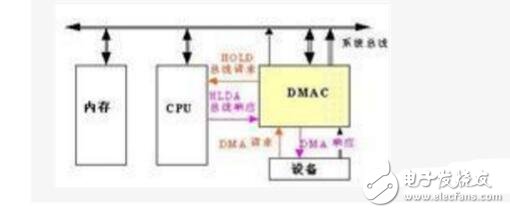

在实现DMA传输时,是由DMA控制器直接掌管总线,因此,存在着一个总线控制权转移问题。即DMA传输前,CPU要把总线控制权交给DMA控制器,而在结束DMA传输后,DMA控制器应立即把总线控制权再交回给CPU。

DMA传输过程

1.DMA请求

CPU对DMA控制器初始化,并向I/O接口发出操作命令,I/O接口提出DMA请求。

2.DMA响应

DMA控制器对DMA请求判别优先级及屏蔽,向总线裁决逻辑提出总线请求。当CPU执行完当前总线周期即可释放总线控制权。此时,总线裁决逻辑输出总线应答,表示DMA已经响应,通过DMA控制器通知I/O接口开始DMA传输。

3.DMA传输

DMA控制器获得总线控制权后,CPU即刻挂起或只执行内部操作,由DMA控制器输出读写命令,直接控制RAM与I/O接口进行DMA传输。

4.DMA结束

当完成规定的成批数据传送后,DMA控制器即释放总线控制权,并向I/O接口发出结束信号。当I/O接口收到结束信号后,一方面停 止I/O设备的工作,另一方面向CPU提出中断请求,使CPU从不介入的状态解脱,并执行一段检查本次DMA传输操作正确性的代码。最后,带着本次操作结果及状态继续执行原来的程序。

由此可见,DMA传输方式无需CPU直接控制传输,也没有中断处理方式那样保留现场和恢复现场的过程,通过硬件为RAM与I/O设备开辟一条直接传送数据的通路,使CPU的效率大为提高。

DMA控制器基本功能

DMA控制器是内存储器同外设之间进行高速数据传送时的硬件控制威廉希尔官方网站 ,是一种实现直接数据传送的专用处理器,它必须能取代在程序控制传送中由CPU和软件所完成的各项功能;它的主要功能是:

(1)DMAC同外设之间有一对联络信号线——外设的DMA请求信号DREQ以及 DMAC向外设发出的DMA响应信号DACK;

(2)DMAC在接收到DREQ后,同CPU之间也有一对联络信号线——DMAC向CPU 发出总线请求信号(HOLD或BUSRQ),CPU在当前总线周期结束后向DMAC发出总线响应信号(HLDA或BUSAK),DMAC接管对总线的控制权,进入DMA操作方式;

(3)能发出地址信息,对存储器寻址,并修改地址指针,DMAC内部必须有能自动加1或减1的地址寄存器;

(4)能决定传送的字节数,并能判断DMA传送是否结束。DMA内部必须有能自动减1的字计数寄存器,计数结束产生终止计数信号;

(5)能发出DMA结束信号,释放总线,使CPU恢复总线控制权;

(6)能发出读、写控制信号,包括存储器访问信号和I/O访问信号。DMAC内部必须有时序和读写控制逻辑。 有些DMAC芯片和模块在这些基本功能的基础上还增加了一些新的功能。如:在DMA传送结束时产生中断请求信号;在传送完一个字节数后输出一个脉冲信号,用于记录已传送的字节数、为外部提供周期性的脉冲序列;在一个数据块传送完后能自动装入新的起始地址和字节数,以便重复传送一个数据块或将几个数据块链接起来传送;产生两个存储器地址,从而实现存储器与存储器之间的传送以及能够对I/O设备寻址,实现I/O设备与I/O设备之间的传送以及能够在传送过程中检索某一特定字节或者进行数据检验等等。

- 相关推荐

- DMA控制器

-

新型可通信智能断路器控制器基本功能有什么?2020-03-10 0

-

MCU的基本功能有哪些呢2021-11-03 0

-

PLC的基本功能与特点解析2022-02-16 0

-

dma控制器由什么组成?2017-12-07 3679

-

dma控制器由什么组成2017-12-07 5556

-

控制器的功能2018-11-24 78482

-

设备控制器基本功能2018-11-24 21453

-

dma控制器的组成2019-04-01 11056

-

机器人控制器的主要功能_机器人控制器存在的问题有哪些2020-08-18 7557

-

控制器的常见种类及基本功能2022-01-07 16832

-

控制器的种类和功能有哪些2022-01-23 11601

-

NXP新能源汽车整车控制器基本功能 整车控制器系统结构框图2022-12-28 1229

-

控制器的基本功能是什么2023-02-24 20390

-

控制器的基本功能 控制器的组成部件有哪些2024-02-01 3891

-

可编程逻辑控制器的基本功能2024-06-03 847

全部0条评论

快来发表一下你的评论吧 !