基于FPGA的扫频信号源的研究与设计

FPGA/ASIC技术

描述

基于FPGA的扫频信号源的研究与设计

扫频技术是电子测量中的一种重要技术,广泛用于调频放大器、宽频带放大器、各种滤波器、鉴相器以及其他有源或无源网络的频率特性的测量。扫频信号源是整个测量系统设计的关键环节之一,随着被测量的频率和精度要求的不断提高,由传统的晶体振荡器设计的扫频信号源已不能满足要求。因此,近年来出现一种直接数字频率合成技术(DDS),它采用数字威廉希尔官方网站 合成所需波形,具有精度高、产生信号信噪性能好、频率分辨率高、转换速度快等优点。本文设计的扫频信号源是基于DDS技术,并在Altera公司的EP2C20上实现逻辑综合、布局布线、时序仿真及功能验证。DDS威廉希尔官方网站 、扫频信号的控制及显示威廉希尔官方网站 均集成在FPGA中实现了片内集成,不仅减小了威廉希尔官方网站 尺寸,而且还增强了抗干扰性,使可靠性得到了进一步的提高。该扫频信号源克服了传统扫频信号源威廉希尔官方网站 复杂、价格昂贵、体积庞大等缺点,具有扫频和点频两种频率输出方式及测频、扫速控制等功能。

1 扫频技术的原理

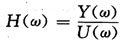

将正弦信号加入线性时不变系统,其稳态响应是与输入信号相同频率的正弦量,但它的幅值和相位则决定于具体系统的动态特性。为此,就需要分析在正弦信号作用下,一定频率范围内系统的输出量和输入量的幅值比和相位的变化规律,即系统的频率特性。一个系统输出量与输入量之比称为频率响应函数。即:

其中,频率响应的模A(ω)=∣H(ω)∣是表征输出与输入的幅度之比,称为系统的幅频特性。频率响应的相位φ(ω)= ∠H(ω)是表征输出与输入的相位之差,称为系统的相频特性。

为了测量系统的频率响应,可以对系统采用逐点扫描的方法,也可以采用扫频的方法。采用扫频的方法通常需要利用扫频信号发生器产生一定频率范围的扫频信号,并将这一信号加到被测系统的输入端。同时,测出该系统对应的扫频输出。则测出的输出信号与对应的输入信号幅度之比就是系统的幅频特性。输出信号与对应的输入信号的相位之差就是系统的相频特性。

2 基于DDS技术扫频信号源的设计与实现

2.1 DDS扫频信号源系统组成原理

扫频信号源是扫频仪的重要组成部分,用于产生测试的正弦扫频信号。其输出的扫频信号应是等幅的,扫频范围应是可调的,扫频规律可以是线性扫频或对数扫频。本系统以FPGA为平台,运用DDS技术实现扫频信号源。与传统的频率合成器相比,DDS是实现电子设备全数字化的一个关键技术。DDS中主要包括频率控制寄存器、相位累加器和正弦计算器3部分。其中,频率控制寄存器用来装载并寄存用户输入的频率控制字。相位累加器则根据频率控制字在每个时钟周期内进行相位累加,得到正弦波的相位值;正弦计算器则计算数字化正弦波的幅度。DDS输出的一般是数字化的正弦波,因此还需经过D/A转换器和低通滤波器才能得到一个可用的模拟信号。

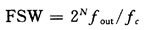

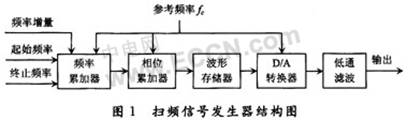

本文设计的以FPGA为实现平台的DDS扫频信号源原理图如图1所示,DDS所产生的是固定频率的信号,其频率控制字FSW与输出信号,fout和参考频率的fc之间的关系为:

扫频信号源只需在DDS原理图的基础上增加频率累加器,每来一个时钟脉冲,频率累加器根据起始频率和频率增量产生瞬时频率,然后经过相位累加器运算输出扫频信号的瞬时相位,以此相位值寻址正弦值存储表,通过查表得到与相位值对应的幅度量化值;在下个周期来临时,频率累加器一方面将在上一个时钟周期作用后所产生的新的频率数据反馈到频率加法器的输入端,以使频率加法器继续累加,频率累加的瞬时值与上一个周期相位累加器反馈到相位加法器输入端的数据累加,然后再依此周期累加的相位值重新寻址正弦值存储表,得到对应的幅度量化值。

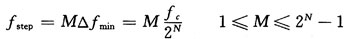

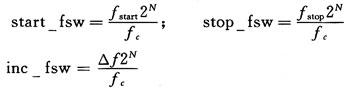

扫频信号源频率分辨率fstep直接取决于DDS的频率最小分辨率△fmin计算公式如下:

扫频信号源需要给定起始频率,fstart终止频率fstop和每个周期的频率增量△f,扫频信号源的起始频率控制字start_fsw、终止频率控制字stop_fsw和频率增量控制字inc_fsw分别为:

2.2 相位累加器的设计

相位累加器由加法器和寄存器构成。加法器完成加法,寄存器将加法器的结果加以保存作为下一次相加用,周而复始直到加法器出现溢出。

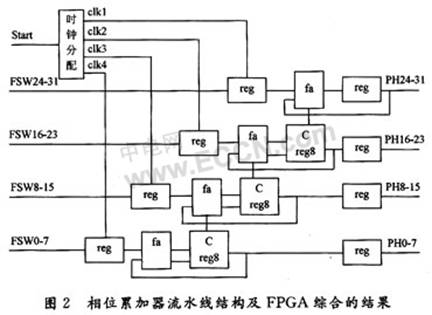

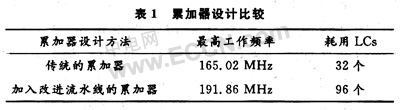

在研究过程中,取相位累加器的输出位数是32位,而对于“一次多位”的加法器来讲,最长的延迟来自进位的脉冲通过所有阶段的时候。目前已经采取了许多技术来缩短这一进位延迟,由于在老一代FPGA中没有提供内部快速进位逻辑,可以通过跳跃进位、先行进位和进位选择加法器来提高加法运算的速度,但是在现代FPGA系列中都具有特别快的“脉冲进位逻辑”,所以本设计采用进位流水线技术,这样不但提高了累加器的运算速度,而且降低了设计复杂度。流水线技术是将一个算术操作分解成一些基本操作以达到提高工作速度的一种技术,因此流水线加法器可以作为提高加法器速度的首选。本设计将32位累加器分成4条流水线,每条流水线完成8位的加法运算,流水线的进位进行级联。采用流水线结构可以提高器件的运算速度。

由于频率控制字只在频率控制字更新后的前4个周期变化,以后各个周期不再变化。基于这种情况,可以对累加器进行改进,从而节省部分存储器。改进的流水线的结构图及在FPGA中综合结果如图2所示。

当频率控制字开始变化时,DDS控制器发送控制信号Start,开始输出控制信号,第一个时钟上升沿到来,将clk1置高,频率控制字FSW的低8位写入第一级流水线的寄存器,第二个时钟上升沿到来,写入FSW的次低8位,以此类推,第四个时钟周期上升沿到来,完成数据输入。在以后的周期内,这些数据将保持不变,直至下一次数据刷新。所以,此流水线设计不仅提高了速度,而且相对减少了寄存器的数量。在EP2C20中实现累加器,采用流水线累加器与传统的累加器速度和资源比较如表1所示。

仿真结果表明,采用进位级联的流水线技术,既能保证较高的资源利用率,又大幅度提高了系统性能和速度。

2.3 ROM压缩算法

在设计中为节省ROM的空间,尽量节省芯片资源,通常累加器的寄存器输出只有其高K位被用于频率合成,其余的较低的N-K位则舍弃不用,这就是所谓的相位截断。在实际应用中,还希望进一步节约ROM的占用,而ROM压缩最简单的方法是利用正弦信号的对称性,利用一个象限的信号通过地址变换来表示全部的正弦信号。

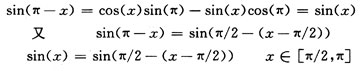

sin(x)函数在0~2π区间内,它是关于x=π的奇函数。即:

所以只需将0~2π区间的相位编码减去π,求出其幅度值后在加移负号,这样的效果就相当于直接对π~2π区间相位求sin值。这个负号要以数字编码的形式表现出来,所以,π~2π区间的幅度序列是0~π区间幅度序列的补码。在0~π区间,sin(x)函数是关于x=π/2的偶函数。所以:

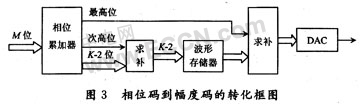

可见,当相位处于π/2~π区间时,将此时的相位编码减去π/2后,在以π/2为模对其求补,这样得到的相位值就是处于0~π/2区间并和原相位值有相同的函数值,在以这个相位码对ROM寻址,得出的幅度就是π/2~π区间对应幅值序列。即ROM中只存储0~π/2的幅度序列,然后通过相位求补,获得0~π的幅度码,通过幅度求补获得π~2π的幅度码。优化后的相位码到幅度码的转化框图如图3所示。

这样就完成了整个波形的拼接,实现用ROM只存储1/4周期波形而可以输出整个周期,减少了ROM的2位地址,ROM表压缩比达到了4:1,且硬件威廉希尔官方网站 比较容易实现。

3 信号调理威廉希尔官方网站

信号调理威廉希尔官方网站 包括低通滤波器和功率放大2部分。

经过D/A转化输出信号含有高频噪声,故要对其进行滤波处理,滤除不需要的频率分量,以便输出频谱纯净的正弦信号。本系统选用7级椭圆低通滤波器,其截止频率为9.8 MHz。功率放大部分是为了提高扫频信号源驱动后级负载的能力。该放大威廉希尔官方网站 选用高速宽带运放MAX 4117及三极管2N2905,2N2219,其带宽可达到300 Mb/s,输入输出阻抗均为50 Ω。

4 系统性能及测试结果

本系统采用Altera公司的EP2C20F484C8为主控制器,D/A转换器选用AD公司的AD9761,AD9761是一个双通道,具有40 MSPS的精度为10位的高速CMOS DAC,并内置2倍数插值FIR滤波器。

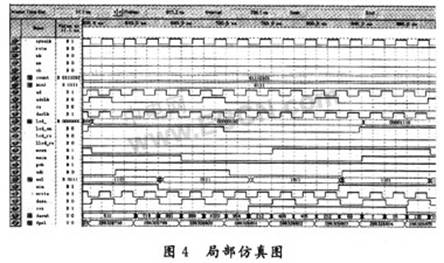

在QuartusⅡ中进行时序仿真,系统的局部仿真结果如图4所示。

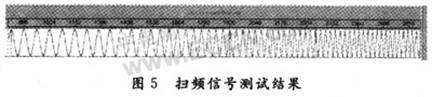

通过QuartusⅡ中的嵌入式逻辑分析仪SignalTapⅡ分析结果如图5所示。

测试结果表明,本系统设计的扫频信号源在线性扫频模式下,完全达到了预期的设计目的。

系统最终在硬件威廉希尔官方网站 中测试结果如下:最大扫频范围:DC~10 MHz,扫频宽度可在此范围内任意设定;最小扫频步长:50 Hz;扫频速度:100 Hz/s;输出波形幅值范围:0~5 V;幅值分辨率:50 mV。

5 结语

本扫频信号源采用DDS技术,完成对相位累加器和相位幅度转化威廉希尔官方网站 的优化设计,与相比利用FPGA芯片将扫频信号源的硬件威廉希尔官方网站 集成在一个片上系统,提高整个系统的工作频率,并减少了寄存器的占用数量。

所有威廉希尔官方网站 模块采用Verilog HDL语言进行RTL级描述,并完成逻辑综合、布局布线、时序仿真及硬件测试,最终在硬件威廉希尔官方网站 上验证了整个系统设计的正确性。测试结果表明,该扫频信号源的时钟频率可以稳定的运行于50 MHz,信号源的频率分辨率可以达到0.1 Hz,扫频范围可以在0~10 MHz之间任意设定,完全满足在中低端扫频仪中应用的要求。

-

基于DDS和FPGA技术的高动态扩频信号源的研究2012-08-17 0

-

基于FPGA和DDS技术的扫频信号源设计2019-07-04 0

-

扫频信号源的制作资料分享2021-05-10 0

-

Agilent 83640B||收购扫频信号源2022-02-22 0

-

基于LabVIEW的低频虚拟信号源设计2010-03-02 675

-

基于FPGA的DDS信号源研究与设计_南楠2016-05-16 497

-

矢量信号源与射频信号源的区别?2018-01-08 27535

-

矢量信号与射频信号源有何区别2020-10-30 1132

-

一文详解射频信号源的工作原理2020-11-19 24504

-

射频信号源的工作原理、组成结构和应用2021-01-06 7347

-

解析射频信号源具体组成部分2021-02-15 3216

-

射频模拟信号源和矢量信号源的区别2022-08-23 3612

-

解析射频信号源三大架构元素部件2022-08-25 2673

-

傻傻分不清?射频模拟信号源和矢量信号源的区别2022-08-23 3432

-

射频信号源的LF源与AM调制信号源是如何调试的呢?2024-01-19 1133

全部0条评论

快来发表一下你的评论吧 !