基于流水线加法器的数字相关器设计

FPGA/ASIC技术

描述

O 引言

数字相关器是扩频通信体制下数字中频接收机核心部件之一,在数字扩频通信系统中应用广泛,但由于受数字信号处理器件速度限制,无法应用于高速宽带通信系统。其中一个重要原因是高位数的加法器进位延迟过大,使得在一个采样时钟节拍内无法完成一次累加运算,而导致相关运算错误。随着FPGA技术的快速发展,器件速度的不断提升,这一问题一定程度得到改善,但仍然无法满足高位数扩频码、高采样速率和大动态范围的数字相关器的工程实现,因此必须采用优化算法最大限度地减少加法器进位操作,从而降低威廉希尔官方网站 延迟对数字相关处理的影响,较为可行的方法是通过流水线加法器构建数字相关器。

1 数字相关器基本模型分析

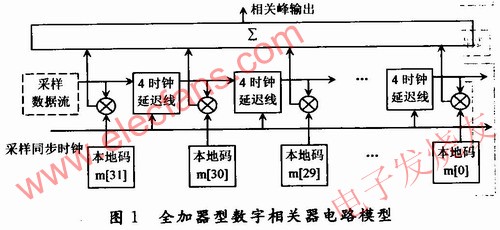

数字相关器类似于匹配滤波器,可以看作乘累加运算器,即输入数据流同本地码在采样同步时钟的驱动下(在一个时钟节拍内)逐级相乘并累加。以32阶数字相关器为例,假定中频信号采样速率是扩频码速率的4倍,输入采样数据流为补码(如果输入码流是2进制码应通过逻辑威廉希尔官方网站 转换成补码),可建立如图1所示威廉希尔官方网站 模型(全加器型)。

图1所构建的数字相关器其特点是模型较为简单,在进行FPGA逻辑威廉希尔官方网站 设计时也较容易实现,同时在输入信号动态范围较小(采样数据流数据带宽较小)的情况下器对硬件资源的消耗也较少(不考虑乘法器消耗的资源)。但是当输入信号动态范围较大时,如采样数据流数据带宽超过8 b,中频信号采样速率超过40 MHz时此模型的缺陷就会暴露出来,其核心问题是∑求和加法威廉希尔官方网站 要在一个时钟节拍内必须完成32个8 b补码数据的加法运算,而FPGA内部门到门的延迟会使每一位加法威廉希尔官方网站 在进行运算时产生一定时间的暂态。当这种暂态逐级累加时就会造成一个时钝单位内无法产生稳定、有效的输出结果,同时如果输入的数据流产生较多的进位,则会使相关结果出错。

由上述可知,图1所描述的相关器威廉希尔官方网站 模型应用在实际的通信系统中会存在隐患,尤其是作为时隙信号同步头字符相关处理时,有可能造成时隙同步的误触发。若作为位同步字符时会造成整时隙的接收数据较高误码。

除此之外,此模型还存在消耗FPGA内部大量乘法器资源的缺点,实际上,数字相关器的每一阶所进行的采样数据流同本地码相乘操作其产生的数据结果并无实际物理意义,而有意义的仅是相乘之后符号,它直接决定了输入码流同本地码匹配的结果。

由表1可见乘法器符号输出的结果实际上是同或运算,即:相同为正,不同为负。因此以乘法器作为相关器符号判决器效率并不高,而且浪费了大量的乘法器资源,完全可以通过组合逻辑判决得到相同的结果。

2 流水线型数字相关器模型

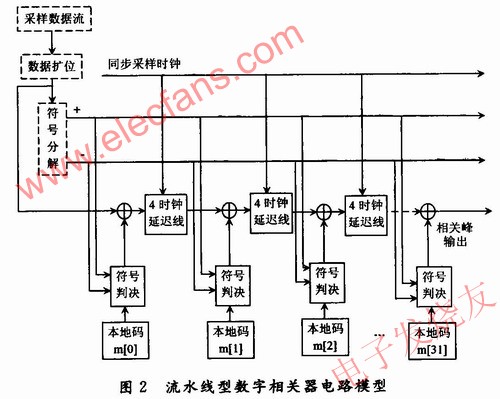

针对全加器型数字相关器的不足,建立基于流水线和符号判决的全新相关器模型,如图2所示。

3 信号处理流程

基于流水线加法器的数字相关器,其信号处理过程可分5个组成部分,即:数据扩位、补码变换、抽取判决、流水延迟和累加传递。

3.1 数据扩位

相关器的设计必须要考虑到数据累加所产生的最大结果,它决定了相关器数据移位寄存器的位宽,无论是全加器型的还是流水型的数字相关器必须对输入数据采取扩位处理。例如:一个32阶8 b输入位宽数字相关器,当输入补码数据流连续的32个码元与本地码符号一一对应,同时每个输入码元的数据绝对值均达到最大值127则累加的结果是25×127,即:数据由8 b扩大到13 b,如果相关器所采用的扩频码位数不是2n也以2n计算。通过上述分析可以得到一个相关器数据寄存器位宽公式:

式中:corro为相关寄存器位宽;indat为采样数据流位宽;n为相关器阶数以2为底数的幂次。确定了数据寄存器的位宽后就必须在数据流输入相关器之前对其进行数据预处理,将数据扩位到最大动态范围,由于输入数据流是补码,因此对正负数的扩位计算不同。下面的Veri-log HDL语言代码描述了一个32阶8 b输入位宽数字相关器扩位威廉希尔官方网站 的算法。

其中:indat为输入采样数据;indat_exp为输入采样数据扩位后的结果。

3.2 补码变换

对于流水线型相关器,需要将每一个采用时钟节拍输入数据流分解成符合相反的数据对,以便于同本地码进行符号判决。处理的方法是在采样时钟的驱动下将输入数据流取反加1,产生其对应的补码数据。下述Verilog HDL代码描述了数字相关器数据变换威廉希尔官方网站 的算法。

3.3 抽取判决

抽取判决的目的有两个,一是使采样数据流降速至码流速率,这样才能与本地码进行符号判决。如采用速率为40 MHz,码流速率为10 MCPS,码长32 b其流水延迟线寄存器的级数为128级,则应采用1/4抽取,即:每4级延迟线寄存器输出1级数据进行符号判决。根据表1构建的组合逻辑算法可知:如果本地码符号为正,则当前时钟采样数据原码输出并同流水线延迟线上寄存的上一阶累加数据相加;如果本地码符号为负,则当前时钟采样数据补码输出并同流水线上寄存的上一阶累加数据相加。

3.4 流水延迟

流水延迟线是流水线数字相关器的核心威廉希尔官方网站 ,其作用是将采样数据流同每一阶本地码进行符号判决并且将累加的结果寄存起来。由于采样数据流的速率是扩频码码速率的整数倍,则流水延迟线寄存器的级数也应是本地码阶数的整数倍。如:采用速率为40 MHz,码流速率为10 MCPS,码长32 b,流水延迟线寄存器的级数为128级。

3.5 累加传递

累加传递是流水线型相关器同全加器型相关器最大的不同之处,也是其克服加法器进位延迟的关键所在。从图1和图2可以清楚地看出全加器型相关器的加法器进位延迟是每个时钟32级加法器的总和而流水线型相关器的加法器进位延迟仅为每时钟1级。因此在同样输入数据的前提下,前者的进位延迟时间(理论上)是后者的32倍,这样两者相关运算结果必然是后者由于暂态数据而造成错误的可能性比前者小得多。但是同全加器型相关器相比,流水线相关器由于采用了累加运算的逐级传递,增加了硬件资源的消耗。因此流水线型相关器是以增加硬件资源为代价换取可靠性和动态范围,而相对当前FPGA技术所能提供的硬件资源而言,多出的资源消耗基本可以忽略不计。

4 结语

目前基于流水线型相关器模型设计的数字相关器已经应用于某高速、宽带扩频通信系统信号处算法设计中,经外场试验检验已达到或超过工程设计要求。随着FPGA处理速度的不断提高,直接通过全加器型相关器实现高速、宽带、线性接收通道扩频通信也会逐渐成为可能,但就目前技术而言,流水线型相关器是实现数字相关技术较为可靠的技术。

- 相关推荐

- 数字相关器

-

求解原理图和PCB,流水线大神帮帮忙2014-12-18 0

-

Verilog流水线加法器always块中应该采用阻塞赋值(=),还是非阻塞赋值(<=)?2016-09-09 0

-

基于流水线加法器的数字相关器设计如何实施?2021-04-06 0

-

请问一下高速流水线浮点加法器的FPGA怎么实现?2021-05-07 0

-

一款32位嵌入式CPU的定点加法器设计2010-07-19 538

-

高速流水线浮点加法器的FPGA实现2010-02-04 2382

-

加法器,加法器是什么意思2010-03-08 5556

-

同相加法器威廉希尔官方网站 原理与同相加法器计算2016-09-13 57595

-

流水线状态机20进制,101序列检测,8位加法器流水线的程序2017-05-24 1299

-

基于流水线加法器的数字相关器设计[图]2018-01-18 429

-

流水线设计的思想介绍与设计实例2019-02-04 8069

-

使用流水线结构设计加法器的方案和工程文件免费下载2020-09-07 807

-

加法器的原理及采用加法器的原因2023-06-09 5162

-

加法器的原理是什么 加法器有什么作用2024-05-23 2969

-

串行加法器和并行加法器的区别?2024-05-23 2550

全部0条评论

快来发表一下你的评论吧 !