基于单片机与FPGA的等精度频率测量和IDDS技术设计方案的实现

FPGA/ASIC技术

描述

电子发烧友网:本系统利用单片机和FPGA有效的结合起来共同实现等精度频率测量和IDDS技术,发挥各自的优点,使设计变得更加容易和灵活,并具有频率测量范围宽、产生的波形频率分辨率高及精度大等特点。系统方便灵活,测量精度和产生的波形分辨率高,能适应当代许多高精度测量和波形产生的要求,可以在各类测量系统和信号发生器中得到很好的利用,频率测量在威廉希尔官方网站 实验、通讯设备、音频视频和科学研究中具有十分广泛的用途。等精度测量技术具有广阔的应用前景,由于其性能的优越性,在目前各个测量领域中都可以发挥着很好的作用,特别是在海洋勘探,太空探索以及各类实验中都得到了应用。

1.DDS信号发生器的实现

使用FPGA与单片机相结合的方式构成DDS信号发生器的核心部分,这是一种从相位概念出发直接合成所需波形的一种新的全数字频率合成技术。其中FPGA完成相位累加、波形地址查找及波形输出等功能,凌阳16位单片机实现频率控制字的输入和液晶显示部分。FPGA与单片机通过串行输入并行输出的方式进行通信。其总体设计框图如图1所示。

1.1 DDS产生原理

图2是一个基本的DDFS结构框图。DDFS 以数控振荡器的方式,产生频率可控制的正弦波、方波、三角波,威廉希尔官方网站 包括了基准时钟源、相位累加器、相位调制器、波形ROM查找表、D/A转换器和低通滤波器等。频率控制字N和相位控制字M分别控制DDS所输出的波形的频率和正弦波的相位。

1.1.1 频率部分

一个N位字长的二进制加法器的一端和一个固定时钟脉冲取样的N位相位寄存器相连,另一个输入端是外部输入的控制字M。这样在每一个时钟到来的时候,前一次相位寄存器中的值和当前的M值相加,作为当前相位寄存器的输出。控制字M决定了相位增量,加法器不断的对相位增量进行线性累加。当产生一次溢出后,完成一个周期性动作,即DDFS合成信号的一个频率周期。

设基准时钟信号为fclk,分频值为N,累加器位数为M,相位累加器步进值为L,根据公式:

设最高频率为20KHz,步进为20Hz,因此累加器位数至少为10位(210=1024>20000/20)。为了保证在最高频率下的波形在一个周期内至少有32个点,因此累加器至少有lO+5=15位。

取晶振频率32.768MHz,可得

1.1.2 相位部分

相位寄存器的输出通过相位调制器与相位控制字K相加,使最终的输出产生一定的相位偏移θ,θ的值与相位控制字K与ROM中的数据有关。我们通过设置两路信号的K值,使两路信号有不同的相位偏移量,从而产生相位差△θ。设A路信号的控制字为K,B路信号的控制字为K’,考虑到FPGA的内部资源,取512个采样点,可得

通常我们只要改变控制字K就可以实现步进调整。

1.2 DDS产生的软件设计

1.2.1 FPGA软件设计

FPGA负责接收由单片机送过来的频率字与相位控制字,同时将波形在ROM中的数据送给DA转换器进行DA转换,输出正弦波、方波、三角波三种波形,通过调节DA转换器的基准电压可调节输出的正弦波、方波、三角波三种波形的幅度,利用按键可以设置一定范围内的频率值和步进值,并能实现波形间的任意切换,实现了频率、步进、幅度的任意调节。

1.2.2 单片机软件设计

单片机软件设计主要是负责接收键盘置入的频率、步进值、选择波形并将其在液晶显示屏中显示和把各种控制信号和数据送到FPGA中。可设置任意频率、任意步进、波形切换等多种输出方式,在此基础上可扩展为任意信号发生器,具体程序流程图如图3:

1.2.3 FPGA与单片机的通信

本系统设计中,FPGA与凌阳单片机采用串行输入并行输出的方式进行通信。使用VHDL语言在EP2C20器件中利用D触发器和移位寄存器接收凌阳单片机发送过来的频率控制字和相位控制字,然后送入相位累加器。在FPGA与凌阳单片机通信中,单片机实行串行输入,不断地向FPGA送频率控制字和相位控制字,送给FPGA实现相位累加。

2.等精度频率计的实现

为了减小误差,得到高的测量精度,我们采用多周期同步测量法,即等精度测量法,通过对被测信号与闸门时间之间实现同步化,从而从根本上消除了在闸门时间内对被测信号进行计数时的 l量化误差,使测量精度大大提高,是在测量领域用得比较多的的一种精度很高的测量方法。

2.1 频率测量总体设计与方案

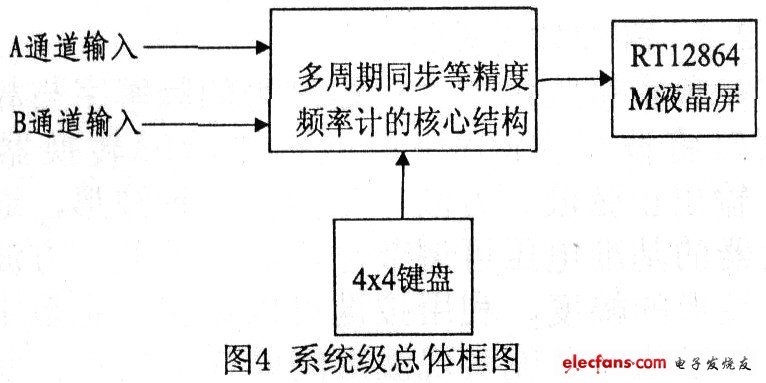

本系统主要是以凌阳单片机和FPGA为核心,多周期同步等精度测量频率计的核心结构用VHDL硬件描述语言对FPGA进行编程,实现频率、周期、脉冲宽度和占空比的测量。而单片机则作为控制部分实现了频率计的控制、扫描和显示,系统级框图如下图4:

本设计频率测量方法的主要测量原理如图5所示,图中预置门控信号GATE是由单片机发出,GATE的时间宽度对测频精度影响较少,可以在较大的范围内选择,只要FPGA计数器在计100M信号不溢出都行,根据理论计算GATE的时间宽度Tc可以大于42.94s,但是由于单片机的数据处理能力限制,实际的时间宽度较少,一般可在l0~0.1s间选择,即在高频段时,闸门时间较短;低频时闸门时间较长。这样闸门时问宽度Tc依据被测频率的大小自动调整测频,从而实现量程的自动转换,扩大了测

频的量程范围;实现了全范围等精度测量,减小了低频测量的误差。

2.2 测频输入级的设计

由于输入的信号幅度不确定、波形不确定、边沿不够陡峭,而FPGA只处理TTL电平的信号,因此我们必须对输入信号进行放大、整形处理。详细设计的威廉希尔官方网站 图如图6所示。

图6放大整形威廉希尔官方网站

2.3 测频的软件设计

2.3.1 FPGA软件设计

此顶层设计图是通过VHDL硬件描述语言在QuartusII 5.1编程环境下实现对数字频率计测量的核心设计图,此设计与外部的凌阳16位单片机SPCE06lA以及输入威廉希尔官方网站 部分、显示威廉希尔官方网站 部分一起构成完整的一个等精度数字频率计的测量系统,精度可以达到设计要求。

2.3.2 凌阳单片机SPCE061A软件设计

SPCE06lA单片机的是对整个系统起到一个控制作用,软件的设计主要是为了实现频率计对频率、周期、脉宽、占空比的测量的切换以及显示,并利用凌阳自带的语音播报功能实现频率测量的实时播报。

3.系统的调试结果与分析

DDS信号发生器的调试结果:通过键盘输入1HZ到4MHZ的正弦波、方波、三角波,设置三种波形的任意步进大小,系统可以产生正弦波、方波、三角波这三种波形,其频率分辨率可以达到O.Oll64153218269HZ,精度O.001%以上。等精度频率计的调试结果:该系统具有能够测量正弦波、方波、三角波三种波形的频率、周期、脉宽和占空比的值,频率的范围可达到0.1HZ~30MHZ,精度达到0.001%以上,同时语音能实时播报待测信号参数。由此可见,整个系统的精度很高,波形分辨率大。

4.结语

采用基于FPGA和凌阳16位单片机的DDS信号发生器设计,不仅控制方便、威廉希尔官方网站 易实现,而且稳定性好、频谱纯净、幅度恒定、失真小、分辨率高;等精度频率计的设计,具有测量精度高、范围宽;测量稳定性好,不随所测信号的变化而变化;使用凌阳16位单片机自带的语音播报功能,不需外加语音芯片,能实时播报测得的频率、周期、脉宽及占空比的大小,使系统变得更加人性化。

-

利用单片机的内部计数器和程序运算功能进行等精度频率测量和显示2009-04-24 1450

-

基于单片机和CPLD的等精度测频系统2010-08-18 474

-

基于FPGA的等精度频率计的设计与实现2008-08-19 0

-

基于Verilog语言的等精度频率计设计2011-03-07 0

-

单片机控制的高精度智能频率计的FPGA 实现2012-08-20 0

-

基于单片机和FPGA的频率特性测试仪的设计方案2019-07-22 0

-

求一款在PCI总线上利用FPGA技术设计PCI总线接口的设计方案2021-04-15 0

-

怎么设计一款基于FPGA和凌阳16位单片机的DDS信号发生器2021-04-30 0

-

单片机实现数字频率计系统功能及指标测量频率范围2021-07-21 0

-

基于单片机的等精度数字测频装置的原理及实现2009-04-25 893

-

单片机控制的高精度智能频率计的FPGA实现2010-07-17 407

-

基于单片机与FPGA的直接频率数字合成器的设计方案2014-01-23 2510

-

基于单片机和FPGA的频率特性测试仪的设计2017-11-24 2481

-

STC15单片机的精度频率计2018-01-27 2601

-

基于51单片机的频率计设计方案2021-06-09 1021

全部0条评论

快来发表一下你的评论吧 !