基于FPGA的采集卡的图像增强算法应用研究

FPGA/ASIC技术

描述

0 引言

图像在采集过程中不可避免地会受到传感器灵敏度、噪声干扰以及模数转化时量化问题等因素影响而导致图像无法达到人眼的视觉效果,为了实现人眼观察或者机器自动分析的目的,对原始图像所做的改善行为,就被称作图像增强技术。因此图像增强技术虽然是改善图像质量的通用方法,但是它也同样带有针对性,它必须是针对某一特定的需要而采用的特定的算法来实现图像质量的改善。

图像增强技术根据各种不同目的而产生了多种算法,根据处理空间的不同把这些算法分为基于空间域的图像增强算法和基于变换域的图像增强算法。基于空间域的图像增强算法又可以分为空域的变换增强算法、空域的滤波增强算法以及空域的彩色增强算法;基于变换域的图像增强算法可以分为频率域平滑增强算法、频率域的锐化增强算法以及频域彩色增强算法。

本论文采用的是空间域图像增强算法,主要利用一定的图像灰度值映射准则来调整图像灰度的动态范围,从而实现图像的增强。

1 图像采集卡总体结构

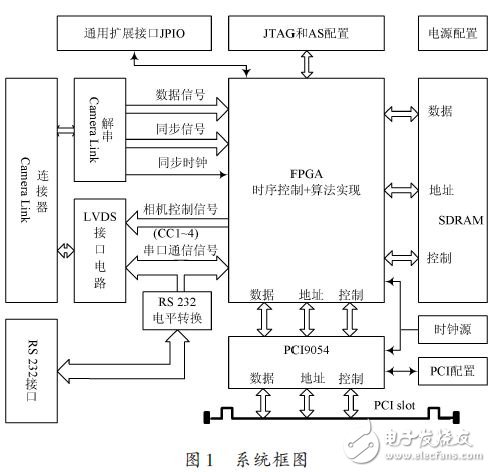

如图1所示,整个采集卡可分成3个子模块,主要有PCI总线部分、FPGA系统部分和外围接口部分。PCI总线部分的主要功能是完成PC机和PCI本地总线上设备的通信,包括PCI总线的通信,本地总线上的总线仲裁、数据传输、中断、中断握手以及PCI9054 芯片的配置功能。

FPGA 系统部分主要实现的是一个FPGA 最小系统。作为PCI9054 本地总线上的设备,FPGA 需要完成和PCI9054本地总线接口之间的通信。同样FPGA也需要具有上电自动配置的功能。外围接口部分主要与FPGA 通信。虽然通过FPGA 产生了各种控制信号,但这些信号在被转换之后才能用于实际的控制。外围接口部分的主要任务就是进行电平转换,以达到实际应用的要求。

2 图像增强算法实现

2.1 图像增强算法设计

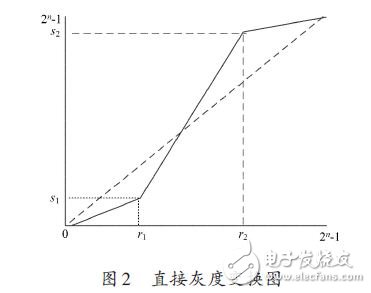

在此,采用基于点操作的增强方法,也称为灰度变换。采用直接灰度变换方法实现增强原图各部分的反差。实际中往往采用增加原图里某两个灰度值间的动态范围来实现。在本设计中,采用图2所示的直接灰度变换的方法,横坐标表示原图像的灰度值,纵坐标表示变换后的灰度值,实线为本论文中讨论的增强对比度变换曲线。虚线表示不做任何变换的曲线图。

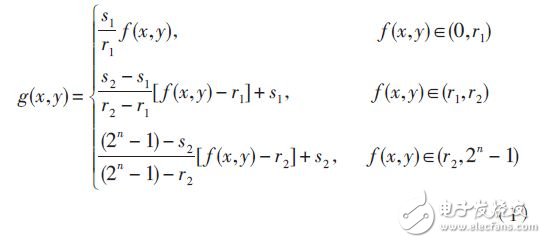

可以看出把原图中的0~ r1 和r2 ~ 2n - 1 间的动态范围明显减小,而原图中灰度值r1 ~ r2 之间的动态范围增加了。其中n 为图像位宽。这样,分段线性变换的数学表达式如下:

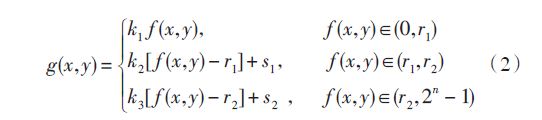

简化表达式,化简如下:

式中参数k1 ,k2 ,k3 可能是一个小数,为了在FPGA 里面能够进行计算,首先需要对这3个参数进行定点化处理。整个定点化的工作被嵌入到驱动程序中,用户只需输入接口数据r1 ,r2 ,s1 和s2 ,驱动程序生成定点化结果k1 ,k2 ,k3 和移位的位数bit1 ,bit2 ,bit3 送入FP-GA.本论文采用定点化方法是,先将小数进行乘2操作(移位操作),如果先到达整数或者大于512提前完成乘2操作,否则对其32次的乘2操作。

2.2 图像增强算法的FPGA实现

利用现场可编程门阵列(FPGA)的并行、实时处理的特性,实现图像增强的片上集成系统(SoC)。系统将图2 中的r1 ,r2 ,s1 和s2 设计成接口参数,用户通过主控计算机的应用程序可以反复配置参数,直到得到预期的结果为止。

2.2.1 FPGA算法的VHDL实现

为了方便阐述,把整个FPGA 实现图像增强算法,分为几个阶段。首先,PC 机通过应用程序送r1 ,r2 ,s1和s2 。而后,由驱动程序中的定点化程序将系数进行定点化,后通过PCI9054把式(2)中k1 ,k2 ,k3 ,r1 ,r2 ,s1 ,s2 和移位参数bit1 ,bit2 ,bit3 送到FPGA的内部寄存器中。这样,FPGA中嵌入的图像增强算法模块就能从SDRAM 中取出原始图像数据进行增强,并把经处理后的图像数据存回SDRAM中。图像增强模块首先取回数据,对取回的数据进行判断,把图像数据分为3个区间。并做相应的减法。结果跟定点后的系数进行定点乘法,之后将结果数据进行移位操作,然后通过累加输出结果。常用的并行处理有两种最基本的连接模式:流水线连接和并行阵列连接。针对该算法,采用流水线连接方式进行。在流水线结构中,一个大任务被分解成复杂性大致相同的小任务,各小任务在流水线上同时执行,整个任务的速度取决于执行时间最长的子任务的执行时间。在本论文设计中把增强算法模块化分成判断模块,减法模块,乘法模块,移位模块和累加模块,并将其进行流水连接。算法逻辑框图如图3所示。

Cyclone器件中的M4K 块支持软乘法器,在设计中采用ALTERA的IP实现。乘法器的IP核如图4所示。

2.2.2 FPGA算法调试结果分析

通过SignalTap抓取图像值为0×08的图像增强算法的调试结果见图5.系数k1 为1,bit1 为4时,图像经算法后的像素值image_data_out为1,符合算法结果正确。

3 结论

本文设计开发了一款以FPGA 为核心控制芯片的嵌入式图像采集卡。采集卡以FPGA 为逻辑和算法实现的核心器件,不仅实现了传统意义上的图像采集,而且实现了CCD 相机控制和激光器同步曝光功能,打破了以往单纯靠增加硬件设备实现同步控制的方法,简化了系统硬件结构并节约系统成本。此外,在系统中嵌入了图像增强算法和采用PCI接口与计算机连接满足了高速采集的要求。根据所选芯片的自身特点,设计了相关的图像增强算法。用VHDL和原理图结合的方法对FPGA 进行编程,实现了图像采集系统的各个功能模块。在FPGA内嵌入了图像增强集成系统,用硬件并行处理实现,经仿真该法效果很好。

-

如何采用FPGA实现图像采集卡的设计?2021-04-29 0

-

基于FPGA高速图像采集卡的研制2009-01-16 652

-

基于FPGA/CPLD和USB技术的无损图像采集卡2009-06-20 1003

-

基于FPGA_CPLD和USB技术的无损图像采集卡2016-06-07 887

-

基于FPGA的图像数据采集卡及其驱动设计2016-08-29 643

-

关于FPGA的图像采集卡的研究与实现2017-08-31 1033

-

如何使用FPGA实现图像数据采集卡及其驱动设计2021-02-03 1198

-

如何选择图像采集卡2023-06-27 985

-

USB图像采集卡是什么2023-07-26 1462

-

图像采集卡与千兆卡的区别2023-12-15 1534

-

机器视觉图像采集卡:关键的图像处理设备2024-02-22 497

-

图像采集卡的选择技巧2024-05-28 454

-

图像采集卡:增强视觉数据采集2024-09-24 306

-

图像采集卡的保养和维护2024-11-21 147

-

如何使用图像采集卡2024-12-13 114

全部0条评论

快来发表一下你的评论吧 !