Xilinx可编程逻辑器件设计与开发(基础篇)连载13:Spartan

FPGA/ASIC技术

描述

2.1.4 BRAM(Block RAM)模块

Spartan-6中的BRAM存储18Kbit数据,能配置成两个独立的9Kbit BRAM或者一个18Kbit BRAM。每个RAM可以通过两个端口寻址,也可以配置成单口RAM。BRAM包含输出寄存器以增加流水线性能。BRAM 在器件中按列排列,其数量取决于Spartan-6 器件的容量。

BRAM 的功能介绍如下。

每个BRAM 的存储容量可达18Kbit。

一个BRAM 可以拆成两个独立的9Kbit,也可以作为一个18Kbit。

每个9Kbit BRAM可以设置成简单双端口模式,从而将BRAM 的数据宽度加倍到36bit。简单双端口模式的定义是具有带独立时钟的一个只读端口和一个只写端口。

分离的同步置位/复位引脚,独立控制输出寄存器和锁存器的置位/复位操作。可以更好地和其他FPGA 系列保持兼容。

18bit 或36bit 宽的端口有不同的写允许信号,此功能常用于对片上微处理器的接口连接。

根据写使能(WE)引脚的状态,所有输出均具有读功能或边写边读功能。边写边读输出具有先写WRITE_FIRST 、先读READ_FIRST 和不变化NO_CHANGE 三种操作模式。

写操作需要一个时钟。

读操作需要一个时钟。

所有输出端口均有锁存。输出端口的状态在端口再次执行读或写操作之前保持不变。默认的BRAM 输出是采用锁存器模式。

输出数据通路有一个可选内部流水线寄存器。强烈建议使用该寄存器模式,这样可使BRAM 工作时钟速率较高,但会增加一个时钟周期的延迟。

Spartan-6的BRAM同其他Xilinx FPGA BRAM类似,支持写/读同步操作,两个端口对称且完全独立,共享数据,每个端口根据需要可以改变其位宽和深度。存储器内容可在配置比特流时进行清除或设置。

Spartan-6中的BRAM配置十分灵活,如表2-10至表2-13所示。BRAM配置为完全双口模式时,每个端口都支持写或读操作;BRAM配置为简单双端口模式时,A口只支持写操作,B口只支持读操作。

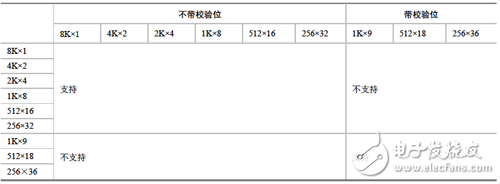

表2-10 9Kbit BRAM的简单双口配置

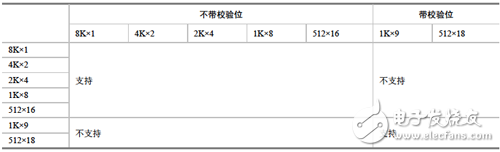

表2-11 9Kbit BRAM的全双口配置

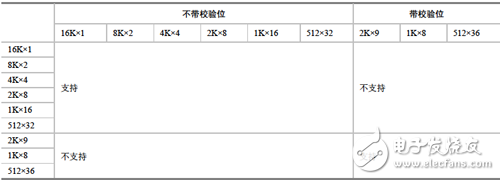

表2-12 18Kbit BRAM的简单双口配置

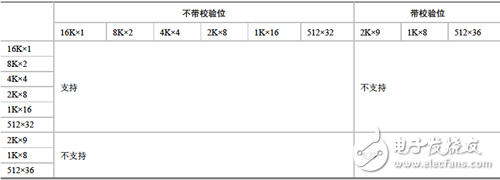

表2-13 18Kbit BRAM 的全双口配置

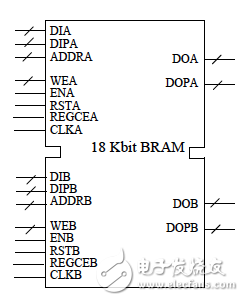

每个BRAM可以配置成完全的双口RAM,有18Kbit的存储空间和两个完全独立的访问口:A口和B 口,结构对称,A 口B 口有独立的地址、数据输入、数据输出、时钟、时钟允许和写允许信号。数据可以写入其中的一个口或者两个口,也可以从一个或者两个口读出,如图2-30所示。

图2-30 全双口RAM

需要注意的是,当两个端口同时对同一个地址操作时,由于双端口RAM 内部没有专门的监控逻辑,因此需要用户监控,以免冲突。两个端口同时对同一个地址的操作不会损坏该物理空间。读写的详细时序请参考用户指南。

每个9Kbit 或者18Kbit BRAM 都可配置成简单双口RAM,区别在于A 口是写操作,B口是读操作,读写都可同时发生。

全双口RAM 和简单双口RAM 的原语见表2-14 所示,可以在HDL 代码中直接例化。

-

Xilinx可编程逻辑器件的高级应用与设计技巧绝版教程2012-02-27 0

-

可编程逻辑器件2014-04-15 0

-

PLD可编程逻辑器件2021-07-22 0

-

可编程逻辑器件设计2006-03-25 1021

-

可编程逻辑器件基础及应用实验指导书2010-03-24 629

-

什么是PLD(可编程逻辑器件)2009-06-20 26248

-

EDA技术与应用(可编程逻辑器件)2012-05-23 915

-

Xilinx可编程逻辑器件的高级应用与设计技巧(孙航)2012-11-28 1383

-

可编程逻辑器件学习(共10篇文档)2016-09-02 1155

-

可编程逻辑器件(书皮)2022-07-10 455

-

可编程逻辑器件原理、开发与应用2017-09-19 782

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 1429

-

可编程逻辑器件的结构2023-03-24 1182

-

可编程逻辑器件测试2023-06-06 683

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 2841

全部0条评论

快来发表一下你的评论吧 !