Xilinx可编程逻辑器件设计与开发(基础篇)连载14:Spartan

FPGA/ASIC技术

描述

2.1.5 DSP 模块XtremeDSP

为了适应越来越复杂的DSP运算,Spartan-6在Spartan 3A DSP模块DSP48A 基础上,不断进行功能扩展,推出了功能更强大的DSP48A1 SLICE。

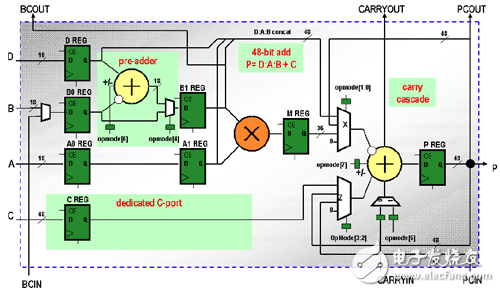

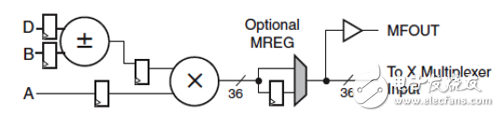

图2-31所示为DSP48A1功能框图,算术部分包含18位预加器、2个48位数据输入的多路复用器(输出X 和Z)、18×18 位二进制补码乘法器,跟随一个48位宽的符号可扩展的后加法器/减法器/累加器。

图2-31 DSP48A1功能框图

DSP48A1的数据和控制输入连接到算术和逻辑部分。A和B输入通道上有两级流水线寄存器。其他数据和控制输入通道也有一级流水线寄存器。在使用流水线寄存器情况下最高运行速率为250MHz(在最低速度等级器件中)。

该结构适应DSP应用中的众多功能,其可编程流水结构、48位内部总线、易于实现两级DSP48A1的级联的特性,增强了它的功能。

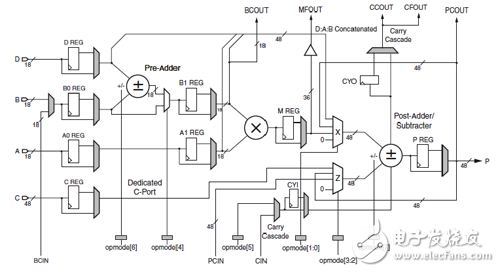

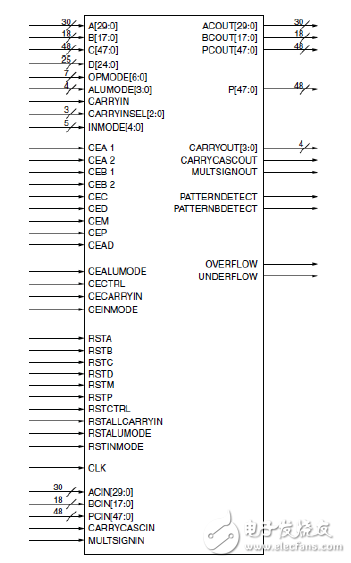

图2-32所示为DSP48A1的详细框图,DSP48A1主要由以下几部分组成。

一、 端口

(1) A、B、C、D、M 和P 端口逻辑。

DSP48A1有4个输入数据通道(A、B、C 和D)和一个数据输出通道(P),A、B 和D 口为18 位宽,C 口为48 位宽,P 口为48 位宽。DSP48A1 还有一个级联数据输入通道(B cascade)和一个级联数据输出通道(P cascade),提供相邻DSP48A1 之间的输入和输出级联功能。B cascade 是一个专用资源,可以设置其属性B_INPUT,作为相邻DSP48A1 的B 口输入。DSP48A1 还具有CIN 输入和CARRYOUT 输出,它主要用于实现相邻DSP48A1 的并行乘累加运算。级联数据输入PCIN 也是一个同相邻DSP48A1 相连的专用资源,通过ZMUX(OPMODE 3:2)动态选择。

图2-32 DSP48A1详细框图

M口是乘法器的36位原始输出,也可选择直接和FPGA逻辑相连,适应多种DSP运算。

18位的D和B口可作为18位预加器的输入,可以旁路预加器,也可以设置OPMODE[4],将预加器的输出连接到乘法器的输入。

18位的A和B口提供18×18乘法器输入,D、A和B可以旁路乘法器,作为X多路复用器的输入。48位C口用于Z多路复用器的通用输入,完成加或减运算。

A口的25位和B口18位数据是25×18乘法器输入。每个DSP48A1都能完成乘加、乘减等操作。A口和B口可以合并跳过乘法器作为X多路复用器的输入。

多路复用器由配置位控制,设置信号的直通、寄存器输入或者级联输入。数据端口寄存器允许用于在增加时钟频率与数据延时之间平衡。乘法器和加法器之间的流水线寄存器为M寄存器。

INMODE[3:0]是DSP48A1里新增的控制位,这些位控制A和D输入寄存器与预加器的函数。

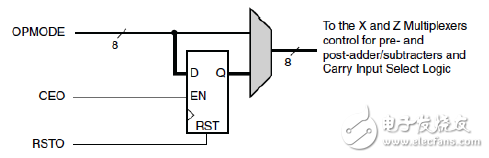

(2) OPMODE端口。

OPMODE端口(见图2-33)支持两种输入方式,直通或者通过寄存器pipeline。使用寄存功能,可以提高DSP48A1的性能。

图2-33 OPMODE端口

(3) X和Z多路选择器。

OPMODE提供了动态改变DSP48A1功能的方法,OPMODE的控制位对应X和Z多路选择器的选择位。多路选择器的输出作为后加法器/减法器的操作数。

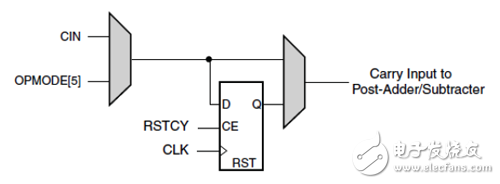

(4) 进位输入逻辑。

进位输入逻辑是OPMODE[5]和CIN的函数。

可能的进位输入在X和Z多路复用器的输出之前“会合”,在某种意义上,X和Z多路复用器函数复制了进位输入信号到进位逻辑。

OPMODE和CARRYINSEL必须正确设置,确保正确选择进位输入(CIN)。图2-34中有两个输入,通CARRYINSEL位选择CIN或OPMODE[5]。CIN为上级DSP48A1的进位输出,OPMODE[5]由FPGA逻辑控制。

图2-34 CARRYINSEL信号逻辑

二、 算术功能

(1) 预加器。

预加器/预减器的输出是OPMODE[6]和B、D数据的函数。OPMODE[6]为1定义为减法操作。

(2) 乘法器。

如图2-35所示,二进制补码乘法器输入为18位的二进制补码,产生36位补码输出。输出可以通过逻辑右移17位,级联成更宽位数的乘法器。

将输入操作数的最高位设置成0,则乘法器就能实现无符号算术运算。

寄存器MREG是乘法器的输出寄存器,可以在增加一个时钟周期延时的情况下,增加乘法器性能。乘法器的36位输出可以作为X多路复用器的输入,或者通过M口(MFOUT[35:0])与FPGA内部逻辑相连。

乘法器的36位输出可以进行符号扩展,达到48位,作为加法器/减法器的输入。

图2-35 DSP48A1内的乘法器

(3) 加法器/减法器/累加器。

加法器/减法器/累加器的输出是OPMODE和输入数据的函数,由OPMODE[3:0]选择哪个输入到X/Z多路复用器,再到加法器/减法器/累加器功能块。

加法或者减法操作由OPMODE[7]控制,OPMODE[7]为1代表减法。X多路选择器的输出与CIN相加,产生的结果与Z的输出相加/减。

分析DSP48A1结构后,我们知道,用它可以完成非常复杂的DSP功能,如FIR滤波器等,极大地提高了数字处理的能力。

Xilinx工具提供了DSP48的原语,可以在HDL中例化,如图2-36所示。还可以通过Core Generator工具调用。

图2-36 DSP48的原语

- 相关推荐

-

Xilinx可编程逻辑器件的高级应用与设计技巧绝版教程2012-02-27 0

-

可编程逻辑器件2014-04-15 0

-

PLD可编程逻辑器件2021-07-22 0

-

可编程逻辑器件设计2006-03-25 1021

-

可编程逻辑器件基础及应用实验指导书2010-03-24 631

-

什么是PLD(可编程逻辑器件)2009-06-20 26377

-

EDA技术与应用(可编程逻辑器件)2012-05-23 917

-

Xilinx可编程逻辑器件的高级应用与设计技巧(孙航)2012-11-28 1387

-

可编程逻辑器件学习(共10篇文档)2016-09-02 1157

-

可编程逻辑器件(书皮)2022-07-10 455

-

可编程逻辑器件原理、开发与应用2017-09-19 782

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 1435

-

可编程逻辑器件的结构2023-03-24 1186

-

可编程逻辑器件测试2023-06-06 686

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 2845

全部0条评论

快来发表一下你的评论吧 !