《Reuse methodology manual》读书笔记:RTL编程指导

FPGA/ASIC技术

描述

(转)在《Reuse methodology manual》第五章,主要收集了一些HDL代码的规范和指导。遵照这些规范或者指导的目的是让你的代码更加的具有可读性、可修改性、可重用;这个应该是所有语言所追求的;而针对HDL代码,还要使代码适合综合和仿真。

注:下面所说的不是什么金科玉律,但是如果能够遵循的话,一定可以增加编程的效率和提高设计的质量。

1. 一般的命名规范

原则:设计自己的命名规范,并对该规则编写文档;在以后的设计中也需要保持一致。

建议:

用小写字母表示所有的信号(signal),变量(variable)和端口(port)名字;

用大写字母表示常量(constant)和用户自定义的类型(type);

用有意义的名字来表示信号,端口,函数或者参数,例如ram_addr用来表示RAM address bus.

用一致的名字表示时钟信号(clock signal);如CLK;

用一致的名字表示复位信号(reset signal);如RST;

低电平有效的信号,名字末尾添加”_b” 或者”_n”;如复位信号低电平有效,可表示为:rst_n;

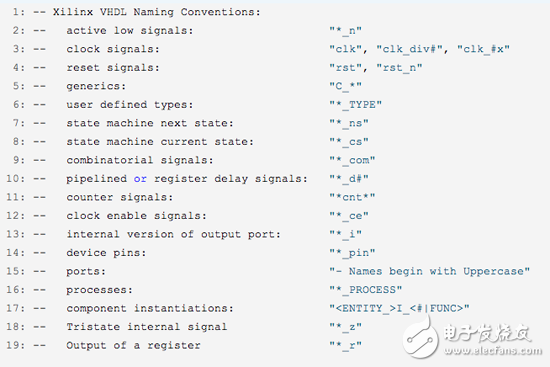

参考如下:

用一致的顺序表示总线,如VHDL中统一用(x downto 0),Verilog HDL统一用[x:0];

合理的注释,对VHDL来说,在代码中合理描述process,function,type和subtype等

为了方便阅读,尽量保持每行不超过72个字母的长度。

用缩进的方式改善代码的可读性,谨慎使用TAB键缩进,因为不同的编辑器有不同缩进的定义,4个或8个字符。

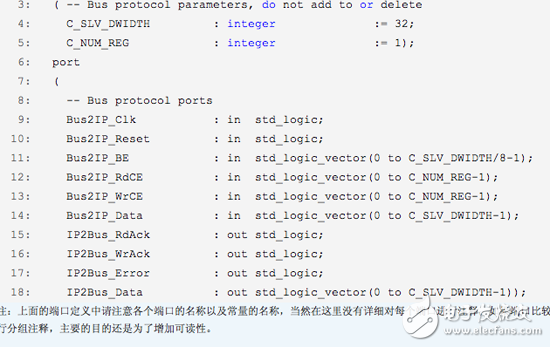

端口的定义顺序,每行只定义一个端口,先input port,后output port;顺序可以为:clk,rst,enable,other control signals,Date and address signals

参考如下:

注:上面的端口定义中请注意各个端口的名称以及常量的名称,当然在这里没有详细对每个端口进行注释;如果端口比较多且容易分组的时候,请对端口进行分组注释,主要的目的还是为了增加可读性。

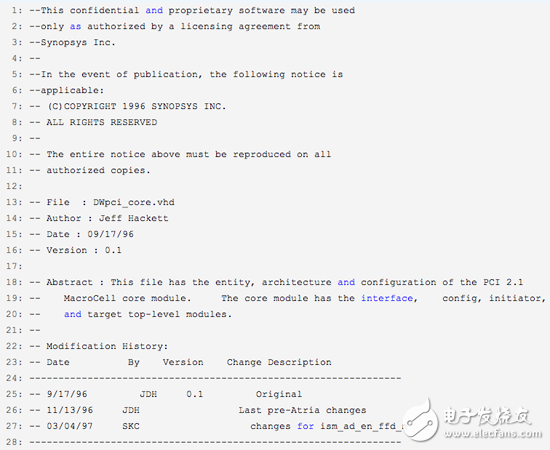

2. 源文件头信息的内容(Informational Headers)

每个源文件都应该包含该文件的相关信息,以便读者或者将来自己的更新,所以头信息必须包含一下内容:

法律声明:保密性,版权,复制品的限制等

文件名

作者

功能描述和模块的关键属性列表

文件创建日期

修订的历史:日期,修订者,修改的表述

头文件参考如下:

3.时钟和复位信号的设计

尽量在设计中避免同时使用上升沿和下降沿触发器,如果无法避免最好将两种触发器放到不同的模块中;

避免手动例化时钟缓冲器,综合工具会自己动添加;

避免门控时钟(Gated Clock),意思说:时钟信号通过一个门威廉希尔官方网站 到达触发器的时钟输入端口,这样给时钟带来一些不确定的因素,产生抖动或者延迟;

避免内部产生时钟信号,内部产生的时钟信号会限制设计的在线测试;

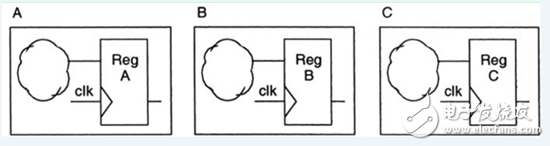

跨时钟域的数据传输,例如:single-bit同步器的设计,见下图;

Multiple-bit 同步器可以用可靠的握手威廉希尔官方网站 或者multibit coding scheme(这个不是很懂)

4. 综合

在设计中避免任何锁存器的出现

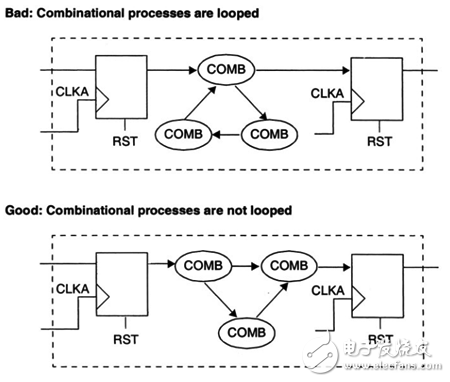

避免组合逻辑中的反馈

定义完整的敏感信号列表,VHDL: process(sensitive list);Verilog:always(sensitive list);

5. 模块划分(Partitioning)

一个好的模块划分有以下优点:

更好的综合结果

缩短编译运行时间

可以用简单的综合策略来满足时序的要求

建议:

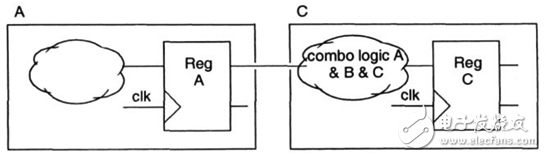

寄存所有模块的输出

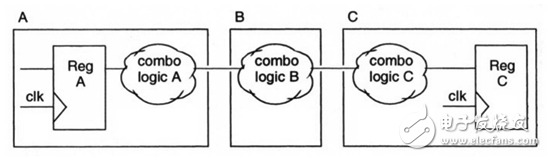

将相关的组合逻辑放到一个单一模块

例如:

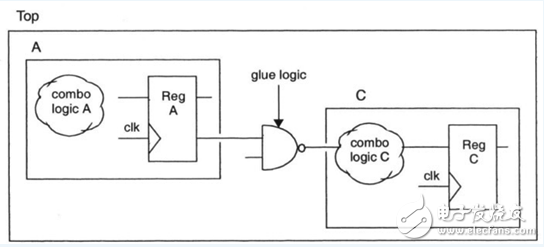

Bad example:

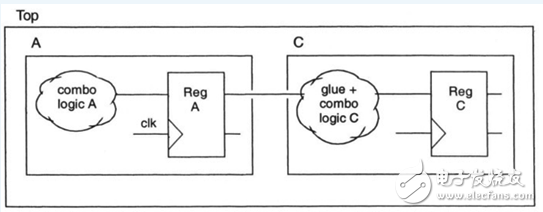

Good example:

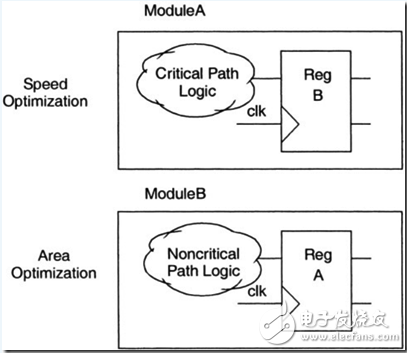

如果两个模块(module)有不同的设计目标,一个要求面积,一个要求速度,最好将这两个模块分开设计,见下图

杜绝在顶层设计中例化一个门级逻辑,例如:

Bad example:

Good example:

6.总结

林林总总说了这么多,杂乱无章,内容基本上都是从书中摘录下来,没有很细的地方,只说了点怎么做,但是绝对没有说到为什么这么做。以上都是书中的经验之谈,话说经验还是自己经历了,遇到了,体会才会深刻。边实践边学习,边思考边总结,经验总会有的,体会总会有的,思想深度也会提高的。

-

AHB总线规范读书笔记2012-08-16 0

-

《C Primer Plus》读书笔记——存储类、链接和内存管理2017-02-07 0

-

嵌入式操作系统UCOSII读书笔记分享!2019-07-18 0

-

计算机系统结构的读书笔记2021-07-29 0

-

测试驱动的嵌入式C语言开发读书笔记分享2021-12-15 0

-

《现代CPU性能分析与优化》——读书笔记2023-04-24 0

-

设计复用的RTL指导原则2011-12-24 591

-

读书笔记2016-05-13 437

-

用骆驼祥子读书笔记来解答ZBLOG博客写作的3个技巧[图]2018-07-11 302

-

读书笔记常用的5款思维导图软件,你正在用哪款?2021-08-30 9449

-

《C嵌入式编程设计模式》读书笔记2021-11-03 927

-

《现代电力电子学与交流传动》读书笔记(二)2021-11-09 357

-

LPMM阅读笔记——第4章 电源门控概述2022-01-11 434

全部0条评论

快来发表一下你的评论吧 !