FPGA实战开发技巧(6)

FPGA/ASIC技术

描述

5.3.3.2 提高时序性能的手段

时序性能是FPGA 设计最重要的指标之一。造成时序性能差的根本原因有很多,但其直接原因可分为三类:布局较差、逻辑级数过多以及信号扇出过高。下面通过时序分析实例来定位原因并给出相应的解决方案。

1.布局太差及解决方案

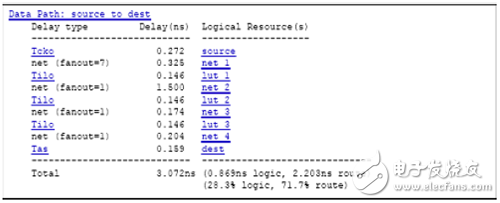

图5-13 所示时序报告,其中附加的周围约束为3ns,实际周期为3.027ns,逻辑时间只有0.869ns,而布线延迟竟达到2.203ns,很明显失败的原因就是布局太差。

图5-13 布局太差的时序报告示意图

相应的解决方案有:

1) 在ISE 布局工具中调整布局的努力程度(effort level) ;

2) 利用布局布线工具的特别努力程度(extra effort) 或MPPR 选项;

3) 如果用户熟悉区域约束,则利用Floorplanner 相对区域约束(RLOC),重新对设计进行布局规划。

2.逻辑级数过多及解决方案

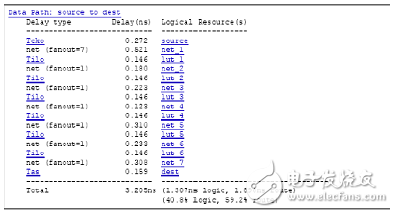

在FPGA 设计中,逻辑级数越高,意味着资源的利用率就越高,但对设计工作频率的影响也越大。在图5-5所示的例子中,附加的周围约束为3ns,实际周期为3.205ns,逻辑时间为1.307ns,已经对设计的实际性能造成了一定的影响。对于这种情况,ISE 实现工具是没有任何改善的,必须通过修改代码来提高性能,相应的解决方案有:

1) 使用流水线技术,在组合逻辑中插入寄存器,简化原有的逻辑结构;

2) 检查该路径是否是多周期路径,如果是,添加相应的多周期约束;

3) 具备良好的编码习惯,不要嵌套if 语句或if、case 语句,并且尽量用case 语句代替if 语句。

图5-14 逻辑级数太多的时序报告示意图

3.信号扇出过高及解决方案

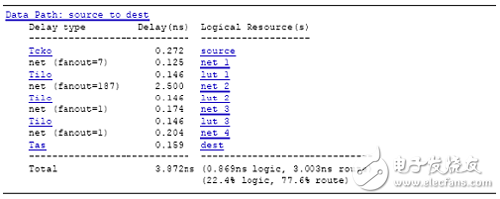

高扇出会造成信号传输路径过长,从而降低时序性能。如图5-15 所示,附加的周期约束为3ns,而实际周期为3.927ns,其中网线的扇出已经高达187,从而导致布线时延达到3.003ns,占实际时延的77.64%。这种情况是任何设计所不能容忍的。

图5-15 扇出太高的时序报告示意图

相应的解决方案有:

1) 通过逻辑复制的方法来降低信号的高扇出,可在HDL 代码中手动复制或通过在综合工具中设置达到目的;

2) 可利用区域约束,将相关逻辑放置在一起,当然本方法仅限于高级用户。

-

FPGA应用开发实战技巧精粹2013-08-05 0

-

《FPGA开发实战手册》2015-10-26 0

-

LabVIEW入门与实战开发100例2016-02-18 3395

-

FPGA开发全攻略实用教程精粹-技巧篇2016-03-29 432

-

FPGA设计实战2016-04-20 818

-

[图灵电子与电气工程丛书].FPGA设计实战2016-05-04 581

-

FPGA II实战演练V1.02016-11-05 873

-

FPGA实战手册2016-11-05 407

-

FPGA电子系统设计项目实战2021-03-23 1019

-

arduino开发实战指南2022-02-22 726

-

Python项目开发实战2022-06-13 478

-

基于Xilinx ZYNQ7000 FPGA嵌入式开发实战指南2024-12-10 160

全部0条评论

快来发表一下你的评论吧 !