Xlinx FPGA的DSP设计工具和设计流程

FPGA/ASIC技术

描述

因为手上有一块Xilinx的Spartan--3E开发板,前些日子陆陆续续学习了ISE的一般工程开发,熟悉了Xilinx ISE 10.x的软件操作和开发板的使用。近来没有事情,于是乎,又把那开发板拿出来把弄把弄,开始学习Xilinx的FPGA的DSP开发设计。在这里先介绍一下Xlinx FPGA的DSP设计工具和设计流程。

近年来,随着多媒体技术和无线通信技术的迅猛发展,信息技术领域对DSP应用的需求不断增长,传统的DSP处理器(现在用得最多的当属IT的DSP,种类多,功能强大,软件技术也很成熟)虽然时钟速率很高,当DSP处理器在运行时按指令顺序执行,因而资源利用率不高,数据的吞吐量较低,难以实现高速率,高复杂度的设计。而FPGA拥有大量可编程逻辑资源,比如专用的DSP块,乘法器、双端口RAM、LUT、寄存器和DCM等,同时配合嵌入式处理器,像Altera的NiosII核、Xilinx的MicroBlaze和PowerPC405等处理器软核或硬核,可以轻松实现高数据率的数字信号处理设计,而且性能原声与传统的DSP处理器,具有可裁剪,灵活性大等特点,正越来越被人们所重视。

使用FPGA进行DSP算法设计时,传统方式下,设计者首先要进行浮点数的算法验证和仿真,然后再将其转换为定点数程序;其次将定点数算法编写成HDL代码,通过反复的功能仿真,后仿真验证程序的正确性,最终生成比特流。Xilinx公司推出的系统建模工具System Generator简化了整个DSP设计流程。设计者只需要根据设计要求咱Simulink下进行系统建模,使用System Generator工具即可自动生成可执行比特流、测试文件等,去掉繁琐的仿真、对比和验证过程。由于提供了适合硬件设计的数字信号处理(DSP)建模环境,加速、简化了FPGA的DSP系统级硬件设计。

关于System Generator的下载和安装过程,我在此就不详细说明了,在google上搜索一下就能找到的。关于System Gnenrator的使用说明我在此向大家推荐一本很好的教材--《Xilinx ISE Design suite 10.x FPGA开发指南》(人民邮电出版社、田耕 胡彬 徐文波等著)我是在学校图书馆借到的这本书,写得很详细,相当不错。我写这篇文章的之前做的实验也是参考上面做的。下面我进入正题,具体介绍我在用SystemGenerator工具完成DSP设计后使用Xilinx ISE 10.x 调用Modelsim SE 6.5进行仿真验证时遇到的的若干问题及其解决方法。

下图为我设计的用Matlab Simulink工具设计DSP工程。

在用System Generator进行FPGA的DSP模块设计是以下几点值得特别注意:

①设计的的FPGA DSP模块的全局输入和输出数据(也就是在非Xilinx库提供的数据源或者数据显示、测量终端,比如下面设计中的Step信号源和Scope示波器等)必须经过Xilinx提供的Gateway In和Gateway OUT进行采样,进而得到FPGA内部能够处理的定点数。

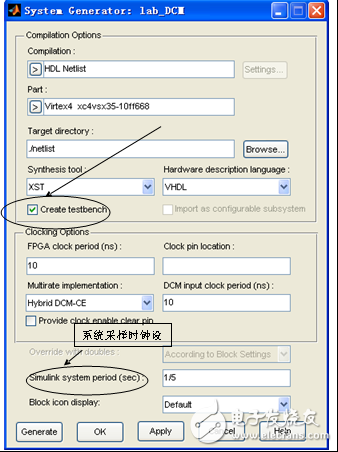

②每个设计中至少要包含一个System Generator图标,因为它是联系MATLAB设计与Xilinx FPGA 硬件实现的主要桥梁,通过它可以实现FPGA实现属性的设置和修改,双击该图标会出现如图-2所示的对话框。

③由于在System Generator中进行设计是需要对外部数据进行采样,所以设计中各个Gateway In和Gateway Out模块都有一个采样周期和采样后所得定点数精度的设置,另外在整个系统也必须有一个系统采样设置,多数情况下就对应着FPGA实现设计是的全局时钟,其设置在 图-2中的Simulink System Clock(sec)。这里需要特别注意,系统设置必须是整个FPGA的最高时钟,而Gateway In和Gateway Out模块的采样周期都必须是它的整数倍,否则系统会报错,设计失败。

下图为System Generator的系统设置,请注意其中勾选了Create testbench选项,这样在点击Generator以后,系统才会自动生成勇于Modelsim仿真的测试文件,十分方便。

当一切设计好之后,点击图-2中的Generator按钮,系统就会自动调用ISE工具进行综合并产生所以需要的设计文件和仿真文件。

接下来,运行ISE,打开Open Project,将路径切换至MATLAB的work工作目录文件下找到netlist文件,进入就会看到一个已经生产的<工程名>_dcm_mcw.ise的ISE工程文件如图-3示,点击打开.

接着,设置ISE调用Modelsin进行仿真的路径:

点击ISE窗口的Edit---->Prefrence,出现图-4窗口,点击展开ISE General--->Intergrated Tools,如下所示,在Model Tech simulator项选择你的Modelsim安装路径完成设置。另外ISE也提供利用其他综合工具进行设计综合的软件接口,如Synplify 或者Synplify Pro。

图-4 点击ISE窗口的Edit---->Prefrence

然后,回到ISE工程界面,在source窗口选择Source for 切换至Behavior Simulation,此时在Sources窗口就能看见刚才System Generator自动生成的testbench测试文件了以<工程名>-dcm_mcw_tb-structure形式命名。如图-5示:

接下来的一步是决定ISE能否成功调用Modelsim SE6.5进行仿真工作的关键。我遇到的问题也大都在于此。如果此时,你和我一样迫不及待的想看到仿真的结果而草草的点击图-6中Process窗口的Simulate Behavioral Model的话,一连串的问题也就随之出现了。

如图-6所示,Modelsim的命令窗口输出了以下错误信息

# ** Error: lab_dcm.vhd(41): Library xilinxcorelib not found.

# ** Error: lab_dcm.vhd(43): VHDL Compiler exiting

# ** Error: D:/modeltech_6.5/win32/vcom failed.

# Error in macro ./pn_behavioral.do line 9

# D:/modeltech_6.5/win32/vcom failed.

# while executing

上面的信息提示://没找到 Library xilinxcorelib所以编译器不能对当前工程进行编译和仿真,所编译器退出。

看到如此的信息,当时很茫然,这到底是怎么回事呢?从 xilinxcorelib来看似乎是Modelsim里面没有Xilinx的仿真库呀!

到google上面一查才知道,原来用Modelsim进行仿真时,先要对设计中调用的元件库进行编译,也就是compile,通过之后才能进行波形仿真(simulate)。而Modelsim 的SE版本属于通用版,仅集成(也就是自带的)一般的库,比如ieee库,Verilog库和标准库std等。不像其专业版,如跟Altera设计的ModelSim-Altera版就自带了AlteraFPGA的全部设计库。

另外,Modelsim在启动时,会调用一个非常关键的初始化文件--Modelsim.ini,这个文件决定了本次Modelsim软件启动后所具备的库的多少和映射关系。在知道了这一点后,我就在电脑上搜索Modelsim.ini,结果惊讶的发现了在我的电脑上面居然有好几个Modelsim.ini文件。如图-7所示:

看到上面的搜索结果,我才想起以前曾经使用过Modelsim,但都是FPGA软件安装包配套的版本,有ACTEL的FPGA设计软件Libero8.3自带的专业许可的Modelsim版本和Altera 的FPGA设计软件Quartus9.0自带的ModelSim-Altera 6.4a (Quartus II 9.0) Starter Edition版本,在使用的时候由于是专业版,都安装好了各自FPGA厂商的设计库,在用FPGA软件调用Modelsim是从未遇到过此类数据库lib方面的问题。

由此,我也发现EDA工具在生成Modelsim测试文件时会根据FPGA的设计环境生产一个Modelsim.ini文件,用于调用Modelsim软件仿真时初始化Modelsim的启动环境。该初始化文件一般都包含在各自的工程设计文件目录下。如图-8所示。

我打开我当前的设计工程目录:D:\Program Files\MATLAB\R2007a\work\my_lab\netlist下的Modelsim.ini文件,发现其中的库设置内容如下:

[Library]

others = $MODEL_TECH/../modelsim.ini

;vhdl_psl_checkers = $MODEL_TECH/../vhdl_psl_checkers // Source files only for this release

;verilog_psl_checkers = $MODEL_TECH/../verilog_psl_checkers // Source files only for this release

;mvc_lib = $MODEL_TECH/../mvc_lib

上面语句的意思是每个库的名称及其映射路径,从上面并没有发现错误中所提到的xilinxcorelib这个库及其映射路径。所以出错也就理所当然啦!

另外从上面的语句还可以看出,Modelsim在启动时首先调用的是当前工程设计目录下的modelsim.ini文件,其他它通过others = $MODEL_TECH/../modelsim.ini还会调用modelsim安装目录下的初始化文件,进行库的映射。

好了,在打开modelsim安装目录下的初始化文件modelsim.ini文件发现其库映射设置如下:

[Library]

std = $MODEL_TECH/../std

ieee = $MODEL_TECH/../ieee

verilog = $MODEL_TECH/../verilog

vital2000 = $MODEL_TECH/../vital2000

std_developerskit = $MODEL_TECH/../std_developerskit

synopsys = $MODEL_TECH/../synopsys

modelsim_lib = $MODEL_TECH/../modelsim_lib

sv_std = $MODEL_TECH/../sv_std

mtiAvm = $MODEL_TECH/../avm

mtiOvm = $MODEL_TECH/../ovm-2.0.1

mtiUPF = $MODEL_TECH/../upf_lib

mtiPA = $MODEL_TECH/../pa_lib

floatfixlib = $MODEL_TECH/../floatfixlib

;vhdl_psl_checkers = $MODEL_TECH/../vhdl_psl_checkers // Source files only for this release

;verilog_psl_checkers = $MODEL_TECH/../verilog_psl_checkers // Source files only for this release

;mvc_lib = $MODEL_TECH/../mvc_lib

中也就是我们在图-6的modelsim软件界面的library栏所见到的所有库了。

继而,我又在google上进一步搜索ISE调用modelsim进行仿真方面的问题。看到一些william hill官网

的回帖中谈到,用Modelsim进行Xilinx FPGA设计的仿真时安装Xilinx库的各种方法。我将它们都一一试了一遍,问题依旧啊!特别是其中用ISE的compxlibgui.exe工具(安装路径\Xilinx\10.1\ISE\bin\nt\compxlibgui.exe)进行自动的Xilinx库编译时,由于选择了全部的库进行编译,用了近3个小时才完成。于是,我很不甘心就这样失败了。

回想整个工程,我又在电脑上搜索modelsim.ini文件,发现此时在ISE的安装目录下多了一个该文件(见图-7所示),于是迫不及待的打开,发现如下:

[Library]

others = $MODEL_TECH/../modelsim.ini

;vhdl_psl_checkers = $MODEL_TECH/../vhdl_psl_checkers // Source files only for this release

;verilog_psl_checkers = $MODEL_TECH/../verilog_psl_checkers // Source files only for this release

;mvc_lib = $MODEL_TECH/../mvc_lib

UNISIMS_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\unisims_ver

UNIMACRO_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\unimacro_ver

UNI9000_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\uni9000_ver

SIMPRIMS_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\simprims_ver

XILINXCORELIB_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\XilinxCoreLib_ver

SECUREIP = C:\Xilinx\10.1\ISE\verilog\mti_se\secureip

AIM_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\abel_ver\aim_ver

CPLD_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\cpld_ver

UNISIM = C:\Xilinx\10.1\ISE\vhdl\mti_se\unisim

UNIMACRO = C:\Xilinx\10.1\ISE\vhdl\mti_se\unimacro

SIMPRIM = C:\Xilinx\10.1\ISE\vhdl\mti_se\simprim

XILINXCORELIB = C:\Xilinx\10.1\ISE\vhdl\mti_se\XilinxCoreLib

AIM = C:\Xilinx\10.1\ISE\vhdl\mti_se\abel\aim

PLS = C:\Xilinx\10.1\ISE\vhdl\mti_se\abel\pls

CPLD = C:\Xilinx\10.1\ISE\vhdl\mti_se\cpld

奇迹般的发现了XILINXCORELIB = C:\Xilinx\10.1\ISE\vhdl\mti_se\XilinxCoreLib

于是,欣喜万分。将上面的全部粗体语句全部copy到当前工程目录下的modelsim.ini文件中,再在ISE下面重复上面的过程,奇迹终于出现啦!

My God!所有的Xilinx库都出现了,仿真波形也出来了!

这里再附上我上传在本网站上的Modelsim SE 6.5的完整版下载链接和利用ISE的compxlibgui.exe工具进行Xilinx库编译的流程截图。希望对大家有帮助。Modelsim SE 6.5的完整版下载链接:如果未能找到,请在搜索栏中搜Modelsim SE 6.5就可以看见了,全部11个压缩包,共202M

。

大家点击附件也可以查看完整版本。

胡恩伟

写于2010年3月15日于重大A区一舍

Xilinx ISE 10.x 调用Modelsim SE 6.5仿真的若干问题及其解决方法 843 KB

-

DSP设计流程有哪几个步骤?2021-04-30 0

-

可支持任意流程的微机电系统设计工具技术2009-11-16 485

-

基于DSP Builder数字信号处理器的FPGA设计2010-11-22 1045

-

FPGA设计工具浅谈2009-10-10 472

-

FPGA设计全流程工具FPGA Advantage培训班2011-03-15 1059

-

Altera推出业界第一款基于模型的FPGA浮点DSP工具2011-09-15 966

-

Altera演示业界首款FPGA的浮点DSP设计流程2011-09-15 687

-

Alter FPGA的设计流程以及DSP设计2012-03-16 985

-

FPGA设计指南:器件、工具和流程_部分22016-04-26 521

-

FPGA设计指南:器件、工具和流程_部分12016-04-26 495

-

FPGA设计工具的重要性 DSP设计基本流程2018-05-19 1302

-

Vivado不是FPGA的设计EDA工具嘛?2018-09-20 9907

-

FL7732 设计工具流程(反激式)2022-11-14 228

-

FL7733A 设计工具流程(反激式)2022-11-15 288

-

FL7701 设计工具流程2022-11-15 226

全部0条评论

快来发表一下你的评论吧 !