7000 芯片Linux下的SPI接口与驱动配置

FPGA/ASIC技术

描述

本文将介绍如何利用Vivado和petalinux开发Zynq7000系列芯片的SPI外设接口。

开发环境:

Vivado 2015.4

Petalinux 2015.4

一、 硬件工程的搭建

1. 打开vivado开发环境,新建工程,并选择你所使用的芯片型号(本文使用xc7z045ffg900-2这款芯片);

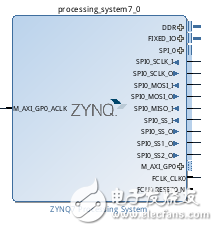

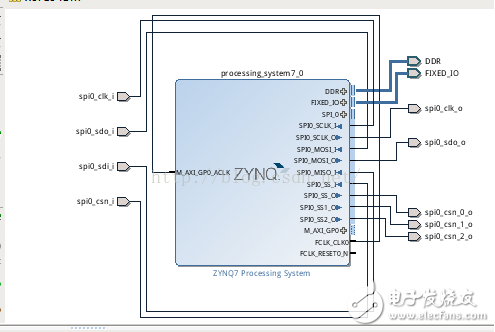

2. 点击“CreateBlock Design”创建一个新的工程桌布,在其中添加IP,将ZYNQ7芯片IP添加进来;

图1 ZYNQ7 IP

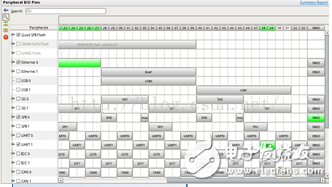

3. 双击ZYNQ7芯片IP,点击界面左边的Peripheral I/O Pins对芯片的引脚进行配置,分别点击“Quad SPI Flash”、“Ethernet”、SPI0最右边的“EMIO”和“UART1”对这些外设引脚进行使能;

图2 外设引脚配置

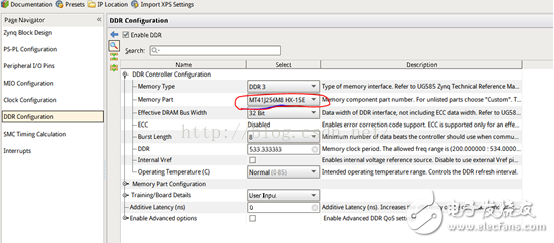

4. 打开“DDRConfiguration”页面,点击“DDR Controller Configuration”,然后点击下拉菜单,选择你所使用DDR类型,本文选用MT41J256M8 HX-15E这款DDR芯片,如图所示;

图3 DDR配置

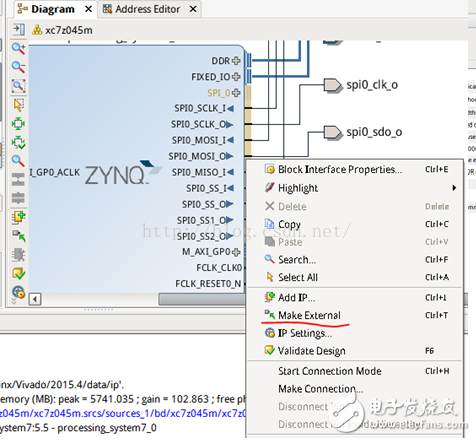

5. DDR配置完成后,退出ZYNQ配置界面,点击ZYNQ7 IP中的SPI引脚,选择相应的IO端口,右键点击并选择Make External将引脚向外引出。

图4 向外引出引脚

6. 所有SPI相关引脚引出后,如下图所示,点击auto connetcion将DDR与FIXED两个引脚引出;

图5 配置DDR和FIXED引脚

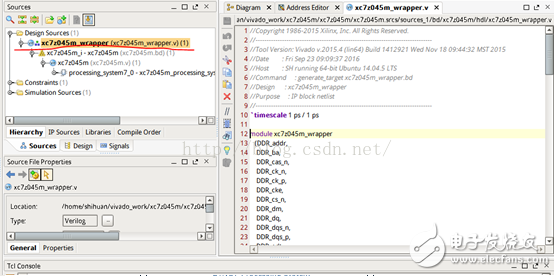

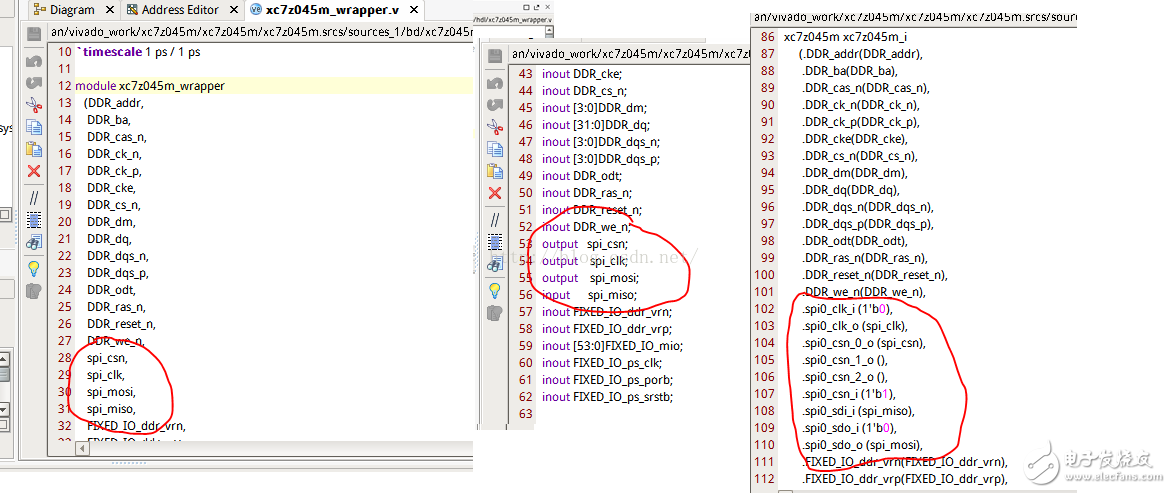

7. 引脚配置完成后,在顶层文件中对ZYNQ7这个IP进行例化,在“source”界面栏中双击顶层文件,打开硬件代码编辑器;

图6 顶层代码

8. 在右边的顶层.v代码中添加spi相关的端口和例化代码,添加的代码如下所示(由于本例中只使用到了spi的四个接口,因此在例化spi接口时,只用到了其中的四个,其它的悬空或直接输入高低电平);

图7 添加接口和例化代码

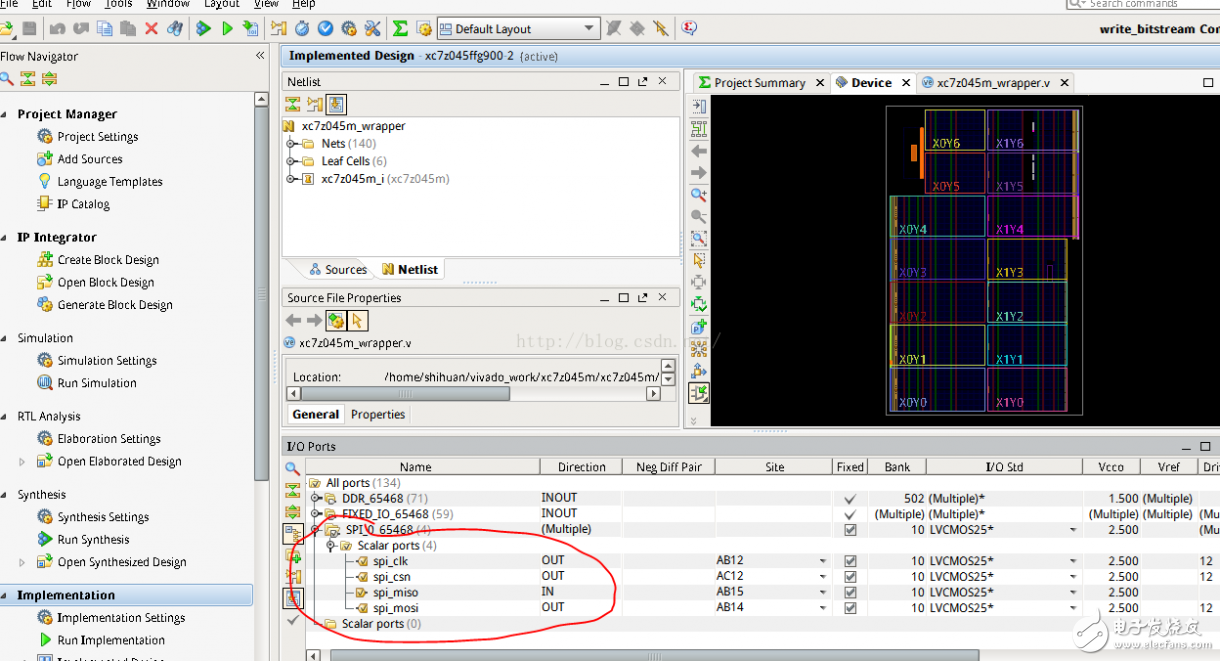

9. 代码添加完成后,对工程进行综合(synthesis)和布局(implementation),综合和布局通过完成后,对管脚进行约束,点击“open implementation”打开布局结果,点击最上方的“Windows”选中“I/O Ports”,对SPI的外部接口进行约束(根据原理图中接口的连接,选中对应的硬件管脚);

图8 管脚约束

10. 管脚约束完成后,重新对工程进行Implementation;

11. 最后点击“GenerateBitstream”生成bit文件;

12. 点击“File”—“Export”——“Export Hardware”导出硬件工程;

二、 硬件工程的搭建

1. 在Linux中,利用petalinux创建一个Zynq工程;

2. 利用petalinux-config–get-hw-description命令将刚才vivado下所生成的硬件工程.hdf文件导入到软件工程中;

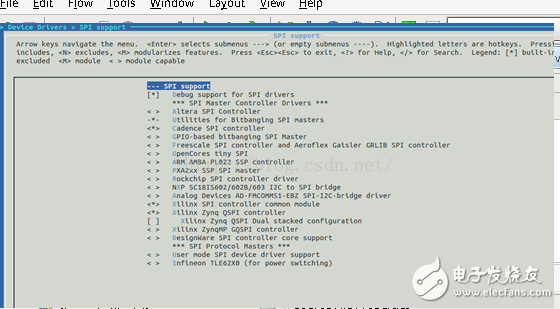

3. 利用petalinux-config–c kernel对内核进行裁剪,选中驱动中的SPI驱动如图;

图9 勾选上SPI驱动

4. 利用petalinux-build工具编译整个工程,然后利用petalinux-package生成BOOT.bin文件;

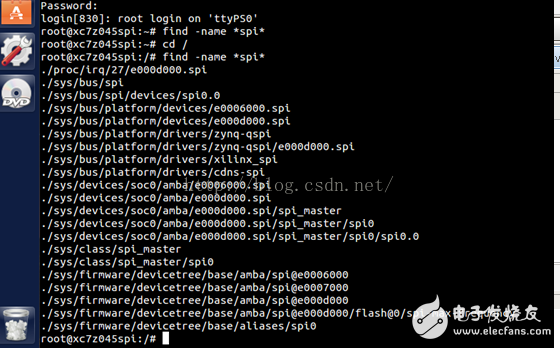

5. 利用硬件平台或QEMU启动Linux系统,即可在系统中看到spi驱动

图10 Linux下的SPI驱动

-

数字温度传感器DS1621在Linux下的IIC接口驱动设计2011-02-12 1849

-

在linux下使用spi接口连接ADS7947芯片完成数据的采样,求相关驱动程序和应用程序示例2024-12-25 0

-

SPI接口 配置问题2015-06-15 0

-

如何配置Linux SPI驱动程序mcp251x?2018-12-05 0

-

Linux环境下USB的原理、驱动和配置2010-01-16 936

-

如何在Zynq 7000平台上使用Linux spidev.c驱动2017-03-21 6413

-

揭开Zynq Z-7000从SPI接口挂载的flash启动的神秘面纱2018-01-10 14702

-

Linux下spi驱动技术分析2018-04-12 3084

-

嵌入式Linux系统的驱动原理和使用ARM Linux实现SPI驱动程序的说明2019-11-14 982

-

嵌入式Linux SPI驱动2021-11-01 492

-

PIC单片机SPI接口配置2021-11-16 811

-

Linux驱动开发-编写VS1053芯片音频驱动2022-09-17 4631

-

Linux驱动-spidev驱动使用方法2023-04-07 5169

-

SPI驱动源文件目录在哪2023-07-25 783

-

SPI控制器驱动层功能介绍2023-07-25 1217

全部0条评论

快来发表一下你的评论吧 !