在NI FlexRIO中使用DRAM

FPGA/ASIC技术

描述

许多高性能仪器使用动态随机存取存储器(DRAM)作为本地存储器,DRAM是一种高密度、高带宽的存储器。选择具有DRAM的NI FlexRIO FPGA模块, 您便可自由地将此类本地存储纳入您的应用。典型的DRAM采用从为基于记录的采集/生成提供的简单本地存储到用于通道仿真应用的长延迟链。本文将探讨NI FlexRIO中DRAM的实现,学习如何在NI LabVIEW FPGA模块使用强大的DRAM抽象和接口。

1. 使用DRAM

本地LabVIEW FPGA接口通过内存连接DRAM。该接口简化了与模块上物理DRAM通信、DRAM资源的竞争请求仲裁以及内存分段(以最大化使用灵活性)的底层复杂性。因此,该接口可帮助用户轻松地读写DRAM。

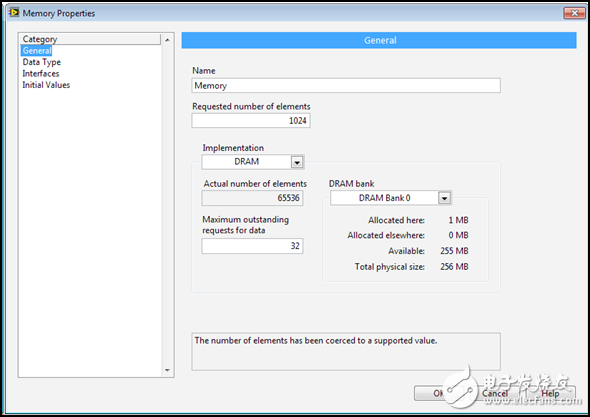

DRAM内存项可在全局项目视图中以与块内存或查询表相同的方式创建。如要创建DRAM内存项,请右击您希望为其创建新内存项的目标,然后选择“新建»内存”。接着选择“DRAM”。每个内存项对应一个DRAM库(bank),如果没有其他内存项分配给选定的DRAM库(bank),该内存项可以覆盖整个库(bank)。

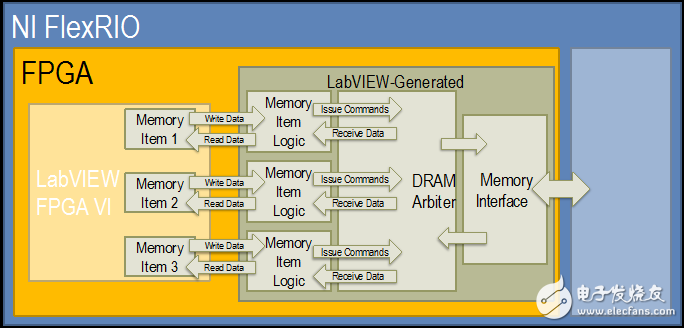

通过内存项,您可以将完整的DRAM空间分割成多个小内存块,这样每个小内存块可以通过LabVIEW FPGA代码的不同部分进行独立访问。 LabVIEW创建仲裁代码,使所有对应接口可均等地访问DRAM。下图是LabVIEW生成的逻辑,提供了特定DRAM库的访问。

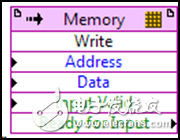

2. 写入方法

下图中的写入方法非常直接明了。写入时需要指定一个地址以便输入数据。当Input Valid的输入为真时,写入命令便会进入接口。Ready for Input端口指示接口是否准备就绪,如果端口的值为假,则数据将被忽略。为了避免信息损失,只有在确保Ready for Input的值为真时才能将数据添加到写入方法中。

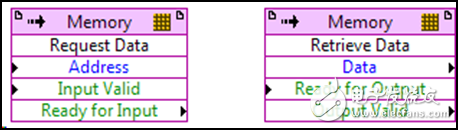

3. 读取方法

内存读取接口采用两种方法:请求数据和检索数据。第一种方法—请求数据首先接收目标数据的地址,然后通过内存控制器请求该地址上的数据。但请记住DRAM接受仲裁和非确定性事件(如DRAM刷新)请求后会存在较长的延迟。因此,数据并不是立即可用的。相反,所有请求根据接收的顺序排队和进行处理。经过一定时间后,检索数据方法显示接下来要请求的数据,并确定Output Valid的输出值以指示该数据是否可用。只有当Ready for Output端口的值设置为真时,数据才会显示,这向内存接口传递的信息是:将使用该数据的逻辑已经准备好接收数据。

4. 其他资源

了解在NI FlexRIO中高效使用DRAM的三个步骤,优化NI FlexRIO的DRAM访问

了解更多关于NI FlexRIO

了解NI射频和无线测试产品与解决方案

了解NI自动化测试平台资源

-

使用NI FlexRIO时我们应当了解和注意的十大点2017-11-18 6343

-

FPGA DRAM数据错位2018-11-07 0

-

如何利用NI FlexRIO模块去满足自动化测试需求?2021-05-06 0

-

NI宣布NI FlexRIO产品线增加新成员2010-03-02 873

-

NI FlexRIO系列产品将PXI Express技术引入2010-03-02 558

-

NI M系列DAQ中使用的新技术2010-04-20 1515

-

全新NI FlexRIO FPGA适配器模块基于PXI平台扩2011-01-11 543

-

NI推出软件定义的无线电模块,用于最先进的5G无线研究2012-12-27 1581

-

NI FlexRIO适配器模块系列总数增至20个以上2013-07-23 1070

-

基于Xilinx Kintex UltraScale FPGA的FlexRIO模块介绍2018-07-05 3136

-

基于FPGA的单原子反馈控制与LabVIEW和NI FlexRIO的介绍2017-10-15 615

-

NI FlexRIO设备的FGPA模块和适配器模块分析2017-11-18 1881

-

基于Xilinx Kintex UltraScale 技术的全新PXI FlexRIO架构介绍2018-06-30 2770

-

NI推出全新的FlexRIO收发器,以满足高带宽雷达系统的原型验证和测试需求2018-10-12 519

-

NI计划将PXI Express引入基于FPGA的设备中2019-12-19 906

全部0条评论

快来发表一下你的评论吧 !