基于FPGA的并行CRC算法的UART控制器

FPGA/ASIC技术

描述

摘要:基于串行异步收发器(UART)的通信中经常用到循环冗余校验(CRC),常见的CRC校验威廉希尔官方网站 多为串行校验, 校验所需时钟周期较多, 基于查找表或输入矩阵转换的并行算法,需要存储余数表,占用大量的硬件资源。该文利用输入和校验多项式的逻辑关系,成功地将基于字节的并行CRC校验算法运用于UART控制器中,在Xilinx公司的可编程门阵列(FPGA)芯片上验证通过,可实现连续多个字节校验。校验一个bit需要1/8时钟周期,降低了校验所需时钟频率,提高了通信的效率,保证了通信的可靠性。

UART 广泛应用于工业通信控制领域。在通信过程中经常需要在数据末尾加入CRC 校验码,保证数据传输的可靠性。CRC 校验码是一种有效但很简单的编码技术, 由于其检出概率高和易于硬件实现,在移动通信、计算机、USB 等领域得到了广泛应用,传统的硬件实现方式是采用串行移位的方式对接收到的每个bit 依次进行校验,校验每个bit 需要8 个时钟周期。CRC 校验的并行算法有查找表法和基于查找表法而导出的一些方法,但这些方法均需要存储长度较大的CRC 余数表,其性能较低。直接利用输入字节数据和多项式的逻辑关系, 推导出CRC 的逻辑表达式,方法直接、简洁[2]。将并行字节CRC 校验机制引入到基于UART 的数据通信中,实现了基于字节的CRC 并行校验, 校验每个bit 需要1/8 时钟周期。目前此方案已成功运用于采集和监控系统中。

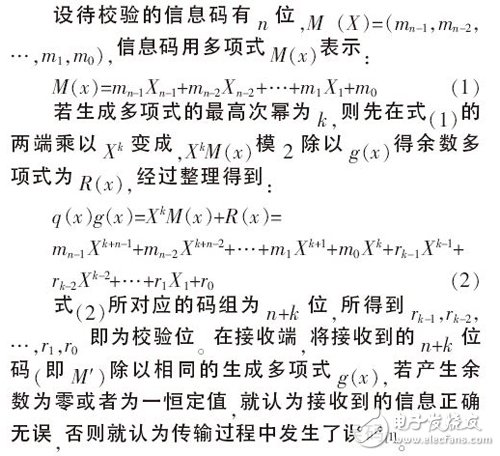

1 CRC 校验原理

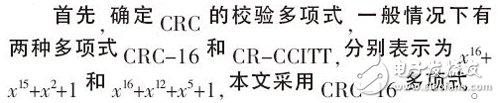

2 基于字节CRC-16 并行校验算法的实现步骤

CRC 并行算法是由LFSR (线性反馈移位寄存器)推导出来的。其基本原理如下:

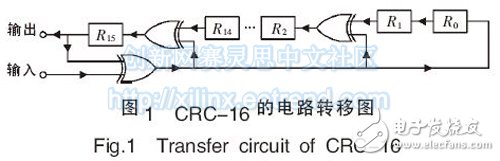

再次,确定威廉希尔官方网站 形式,将CRC 多项式根据LFSR(线性反馈移位寄存器) 转换成威廉希尔官方网站 转移图形式[3]。如图1 所示。

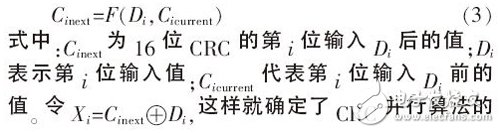

最后,代入输入数据,对每一位引入寄存器,依次将数据中的每一位引入到LFSR 的输入端, 最终得出所有位输入后,CRC 结果中每一位的逻辑表达式,即:

表达式。

3 UART 控制器

异步通信有如下特点:字符帧的传输格式使发送方在字符之间可按应用要求插入不同的时间间隔,即每一个字符的发送是随机的,这是异步通信的主要特点[4]。

每一个字符的传输开始总是以一个起始位为准,然后接收方与发送方保持同步(格式的统一)。通信双方可按应用需要随时改变通信协议,即改变数据位、奇偶校验位和停止位长度和数据传输率。

在异步通信的数据流中,一个字符看作一个独立的信息单元,并且字符出现在数据流中的相对时间是任意的,接收端预先并不知道,每个字符一经发送, 收发双方则以预先固定的时钟速率传送各位。因此,要有效进行异步通信,在CPU 与外设通信之前,必须统一字符格式和波特率。

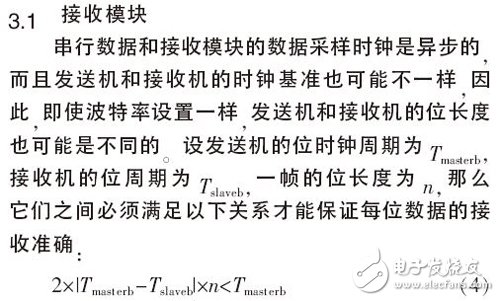

由上式可以看出, 不考虑FPGA 芯片内时钟的建立和保持时间和传输过程所受的干扰,当n 一定时,波特率越高,位周期误差越小,累计误差越小,数据传输的出错率越小。

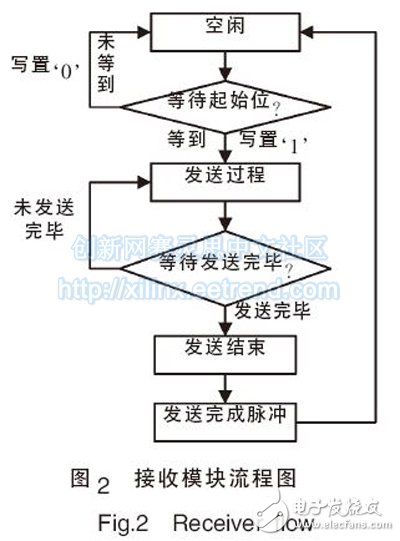

Rxd(输入引脚)从‘1’变为‘0’代表了起始位,为了消除毛刺的干扰, 一般采用16 次过采样的方法,保证正确接收每一位数据,将每一位数据的中间采样作为采样结果,可以把后续数据位检测的累计误差降到最小。因此,计数到8 时标志起始位的中心,每隔16 个采集周期采集一次数据,直到所有数据位采集完成,最后检测停止位,随后输出接收完成标志脉冲。软件流程图如图2 所示。

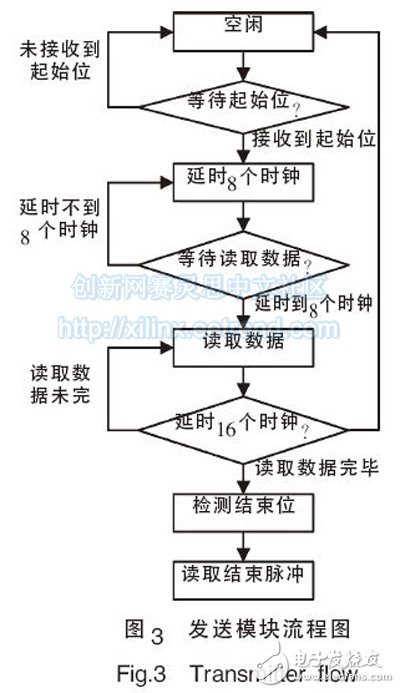

3.2 发送模块

发送模块的时钟频率即波特率时钟周期,发送模块无需考虑时钟误差问题,只需按照发送周期将每一位发送出去,为了使发送器每次发送一个字节,采用了上升沿触发启动发送任务,发送完一帧后自动停止,因此,当检测到发送使能引脚上升沿时,在发送时钟驱动依次输出开始位、数据位和停止位。软件控制流程如图3 所示。

3.3 总体控制

读写控制模块是两个独立的控制模块,但是在本系统中是半双工模式,即收到命令帧时再根据协议内容发送数据,通过信号机制实现两个模块进程的相互通信, 设trans_over 为发送的状态信号,receive_over 为接受的状态信号,接收模块先处于工作状态,当接收完一帧数据时receive_over 置‘1’并等待发送模块发送完成后trans_over 置‘1’,发送模块首先将trans_over 置‘0’, 等待receive_over 置‘1’,发送完数据后trans_over 置‘1’ 并且等待receive_over 置‘0’。通过这两个信号,协调发送和接收模块的工作。

4 实验结果

4.1 软件波形仿真

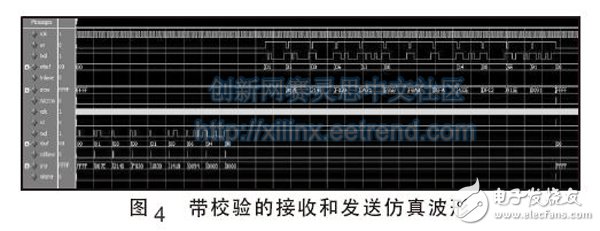

实验以Xilinx 公司的XC3S400 为FPGA 芯片,实验数据和功能仿真波形如图4 所示,串口波特率为9600,8bits 数据位,无校验位,1 个停止位。起始位,停止位不参与CRC 校验。

为了与实际中多数的上层协议软件版本的CRC-16 校验保持一致,将输入数据先进行反转,复位时寄存器的值都置为‘1’;接收时CRC 字节参与校验,通过判断结果是否为0x0000 确定数据传输是否正确。

发送时先发送CRC 的低8 位, 再发送高8 位。发送过程中本文采用将CRC 结果也参与校验,发送完数据后直接发送两次CRC 结果的低8 位,实现了高8 位和低8 位自动交换。

4.2 硬件测试结果

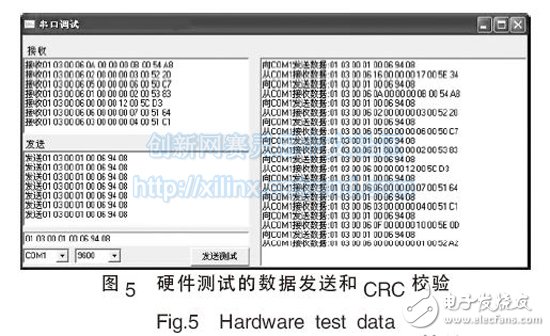

将程序下载到FPGA 芯片中进行测试,采用PC端串口控制软件进行UART 通信实验,其部分数据如图5 所示。

硬件威廉希尔官方网站 的核心板为XC3S400(TQ144 封装),串口芯片采用Max3232, 基本的协议是如果接收的数据校验正确返回相应字节长度的数据, 本例中0x01,0x03 为帧头,0x00,0x01 是地址,0x00,0x06为数据长度。经过重复实验,收发系统保持了非常高的传输可靠性。

标志脉冲延迟输出:当接收一个字节数据完成时,如果数据的锁存和标志脉冲同步,那么第一个校验的字节是空闲时的CRC-16 模块输入端数据,因此为了保持每一次校验都是本次接收到的数据,CRC 校验接收完成标志正脉冲应该稍有延时,这样数据先更新,校验脉冲紧随其后,保证了CRC-16 模块连续字节数据输入校验的正确。本文采用将标志正脉冲通过一个D 触发器,实现了脉冲的延时输出。

4.3 软件仿真与硬件实测结果分析

通过图4 和图5 可看出,仿真的结果与实测结果相同, 说明基于FPGA 实现的并行CRC 算法的UART 控制器,数据传输正确,达到了设计的目的。

5 结语

在进行较多的数据传输时串行CRC 威廉希尔官方网站 所需时钟周期较多,CRC 并行算法能够有效地降低校验的时钟频率,本文将并行CRC 算法应用于UART 的通信中,减少了校验所需的时钟周期,保证了数据传输的可靠性,取得了良好的效果,具有重要的实用价值。目前已应用于实验室的多路高压数据采集监控仪器上,工作稳定可靠。

-

求 基于FPGA的uart控制器的设计和仿真2013-04-04 0

-

如何使用微控制器读取FPGA配置CRC2020-06-10 0

-

CRC算法原理及C语言实现2009-09-23 721

-

基于FPGA的HDLC协议控制器2011-07-20 1150

-

并行CRC在FPGA上的实现研究2011-08-15 533

-

基于DSP与FPGA的运动控制器研究2012-10-26 993

-

基于SATAⅡ协议的CRC32并行算法的研究2012-11-07 2054

-

在FPGA上实现CRC算法的程序2016-06-07 937

-

一种基于矩阵的并行CRC校验算法2017-10-30 991

-

如何使用FPGA实现HDLC协议控制器2020-11-04 1085

-

使用FPGA实现高速CRC并行算法的设计研究2021-03-23 839

-

并行CRC威廉希尔官方网站 HDL代码的快速生成2021-03-28 950

-

USB数据传输中CRC校验码的并行算法实现2021-03-28 839

-

CRC校验码并行计算的FPGA实现2021-03-28 1425

-

fpga报告crc故障是什么意思2024-01-04 1474

全部0条评论

快来发表一下你的评论吧 !