Zynq SoC构建LTE小型蜂窝基站的设计基础

FPGA/ASIC技术

描述

采用赛灵思Zynq-7000 All Programmalbe SoC能让毫微微、微微以及其他小型蜂窝基站设计的集成度、灵活性和低功耗达到全新的高度。

小型蜂窝属于低功率无线基站,运行于授权频谱范围内,并由移动网络运营商进行管理。小型蜂窝基站的类型囊括毫微微(Femtocell)、微微(Picocell)、微蜂窝(Microcell)和多载波基站(Metrocell),覆盖范围从一百米到数百米不等。如今,小型蜂窝系统的电子核心组件包括FPGA、DSP器件以及网络和主机处理器,这些组件都要满足不断发展演进的无线标准要求。然而,新一代小型蜂窝系统正在快速高度集成化,将以上这些元件集成到单个片上系统(SoC)内。

电信运营商可利用小型蜂窝扩大家庭、企业以及城市和乡村公共场所的蜂窝网络的覆盖范围和容量。无论在家还是单位,越来越多的客户希望随时随地使用移动电话,即便有固网的情况下也是如此。另外他们还希望覆盖范围能够无处不在,并通过足够的带宽享受创新的移动数据服务。

大部分而且是越来越多的数据使用都发生在室内,但宏蜂窝在室内的覆盖效果却很差。因此,小型蜂窝在弥补覆盖范围和容量需求方面能够起到重要作用。小型蜂窝不仅能减少断线次数,提高数据速率,改善最终用户的使用体验,同时还能降低运营商的资本支出和运营支出,进而减少场地租金、维护和用电成本。

赛灵思Zynq®-7000 All Programmable SoC将处理器的软件可编程性与FPGA的硬件可编程性完美结合在一起,实现了无与伦比的系统性能、灵活性与可扩展性,并在降低功耗、削减成本和加快上市进程方面获得了显著的系统优势。由于Zynq SoC同时具备软/硬可编程功能,因此与传统的SoC处理方案相比,能够为客户提供无与伦比的可编程功能和差异化能力。标准SoC仅具有软件可编程性,极大地限制了设计灵活性和差异化,而且不利于有效地适应不断发展演进的无线标准。

ZYNQ SoC是LTE小型蜂窝基站的理想选择

Zynq SoC的高性能可编程逻辑和ARM处理器可让客户打造出能够满足当前及新一代无线设备不断提高的传输带宽需求的设计方案。设计团队可在Zynq SoC的处理系统中实现协议栈,并观察其运行情况。如果太过缓慢,可利用Vivado®设计套件高层次综合(HLS)工具将代码转换为Verilog或VHDL格式,以便在Zynq SoC可编程逻辑中运行。这样可以将一些功能代码的运行速度提高700倍,同时释放处理器以更快地执行其他任务,从而提升整体系统性能。

很多小型蜂窝基站必须在无制冷风扇的条件下运行,因此对散热提出了较高要求。Zynq SoC的功耗极低,这样不仅可在系统中避免使用风扇,而且也不必安装昂贵的散热片。

很多小型蜂窝基站必须在无制冷风扇的条件下运行,因此对散热提出了较高要求。Zynq SoC的功耗极低,这样不仅可在系统中避免使用风扇,而且也不必安装昂贵的散热片。赛灵思还提供用来提高功率放大器效率的无线IP,这种IP有助于设计团队进一步降低小型蜂窝基站的耗电量。

异构网路(HetNet)需要连接大量采用不同操作系统和协议的计算机和设备,为此,赛灵思推出了极富吸引力的All Programmable器件组合。这些产品具备最大的设计灵活性,仅单个可重配置器件即可满足HetNet的多标准与多频带需求。无论客户设计的是小型蜂窝还是传统的宏蜂窝架构,都可以找到合适的赛灵思器件。赛灵思的Zynq SoC器件相对于任何其他器件而言,能够提供更高的系统集成度,因此特别适用于小型蜂窝HetNet系统。双核ARM® Cortex™-A9处理器能够实时处理任务。其中的一个Cortex-A9处理器运行实时操作系统并负责处理L1控制任务,而另一个Cortex-A9则运行部分或全部更高层功能。

重负荷用户层处理任务最好在硬件中完成。与多核SoC相比,结合使用赛灵思丰富的最佳LTE基带功能集,集成的7系列FPGA架构能够以更低的功耗实现卓越的实时性能。FPGA架构还可用来加速L2用户层功能,从而减轻ARM处理器的负载,这样设计人员就能够灵活地加速架构中的硬件,从而提高更高层的性能。该架构还允许集成数字上变频和下变频(DUC/DDC)、可选峰值因数抑制(CFR)以及数字预失真(DPD)等数字前端(DFE)功能。这种高集成度可进一步降低功耗,并有助于减少LTE基站设计中非常重要的整体端对端时延问题。

小型蜂窝基站的灵活性

赛灵思提供一个与赛灵思LET基带配套的基于Zynq SoC的LTE小型蜂窝基站参考设计,当然客户也可以集成自己的LET基带。另外,赛灵思还提供包括LTE协议栈、RAN安全、回程IPSec、时序与同步以及稳健报头压缩(RoHC)等在内的综合而全面的软件解决方案。

Zynq SoC支持PCIe®协议,这样设计人员就能够在基于SoC的LET小型蜂窝基站设计中轻松集成Wi-Fi功能。Zynq SoC的高性能处理功能和I/O,让其理想适合用于带集成无线回程的高性能小型蜂窝基站设计。此外,对JESD204B的支持使基于SoC的LET小型蜂窝基站可以轻松连接到任何业界领先的RF收发器。

针对低容量和中等容量的小型蜂窝基站,赛灵思采用Zynq SoC实现了一款具备集成物理层的高集成度解决方案。该物理层包括在可编程逻辑(PL)中实现的无线电+L1基带,以及在处理系统(PS)中实现的更高层协议栈、回程传输管理和物理层时序与控制。可编程逻辑还可以为一些更高层功能提供硬件加速,从而使容量最大化(这是与同类竞争产品拉开距离的重要因素)。Zynq SoC系列通过单芯片实现方案可满足多种部署情况。

考虑到目前Zynq SoC系列的处理能力,对于很高容量的小型蜂窝基站而言,赛灵思建议在可编程逻辑中实现无线电+L1基带,在处理系统中实现相关时序与控制。可以采用辅助处理器来处理更高层协议栈和回程传输管理任务。

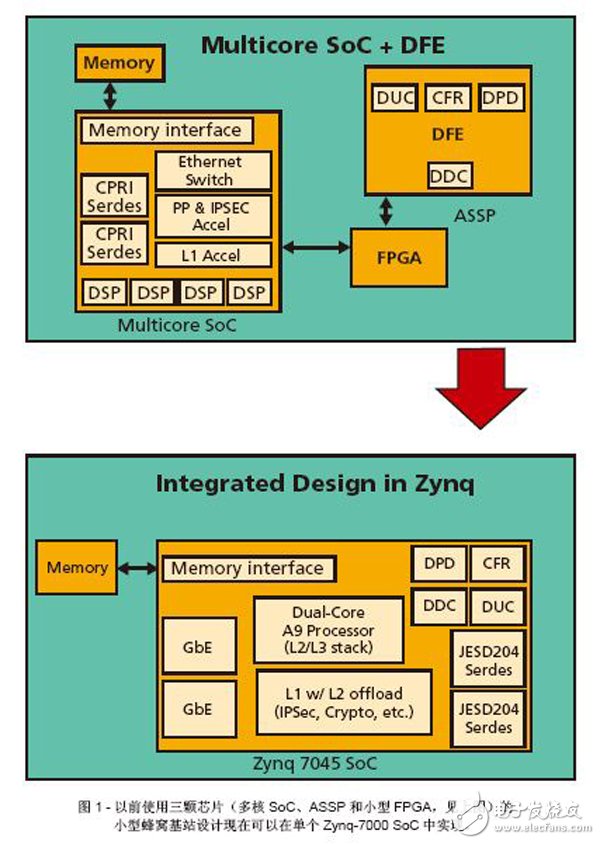

图1中的上图是典型的2X2 (2T2R) LTE小型蜂窝基站设计。此类设计的典型材料清单(BOM)一般包含三颗芯片:多核SoC、ASSP(用于数字前端)和小型FPGA(用于剩余的逻辑和存储器)。下图将这些芯片都集中到了单个Zynq SoC器件中(例如Z-7045),其中双核ARM Cortex-A9负责运行LTE L2/L3协议栈。LTE L1被集成到FPGA架构中,并为L2提供硬件加速,以分担IPSec、加密和RoHC等处理任务。FPGA架构还包含数字前端(DPD、DUC、DDC、CFR)。采用单芯片设计不仅能降低芯片间时延,实现最佳包处理能力,而且还可将材料成本降低25%,系统性能提高一倍,总功耗降低35%。

LTE小型蜂窝基站设计要求实现低成本、低功耗、高集成度和高可靠性。全集成、可扩展性和灵活性是实现上述目标的关键。Zynq-7000 All Programmable SoC具备双核ARM处理器子系统、高系统性能和低功耗可编程逻辑,是一款能够满足当前及未来小型蜂窝基站需求的低成本解决方案。

-

小型蜂窝基站长期演进软件中的挑战2018-09-04 0

-

适用于小型蜂窝基站开发平台具有DPD反馈路径的收发器2018-12-12 0

-

TD-LTE毫微微蜂窝基站的帧结构2019-05-31 0

-

小蜂窝基站在LTE网络中有什么大作用2019-06-19 0

-

小型蜂窝基站的实现2019-06-19 0

-

数字无线电前端策略为小型蜂窝基站带来改变游戏规则的优势是什么?2021-04-19 0

-

小蜂窝基站在LTE网络中有什么作用?2021-05-21 0

-

小型蜂窝基站面临的挑战2022-11-17 0

-

TD-LTE微微蜂窝基站测试2010-04-09 1113

-

针对LTE小型蜂窝系统用户的路线图2010-12-03 982

-

德州仪器推出面向小型蜂窝基站及宏基站的多标准SoC2012-04-13 773

-

TI基于KeyStone的SoC系统助力PureWave高性能小型蜂窝户外基站2012-05-28 747

-

LTE小型蜂窝系统验证测试方案2012-07-25 1132

全部0条评论

快来发表一下你的评论吧 !