基于FPGA的高速嵌入式通信系统的设计与实现

FPGA/ASIC技术

描述

摘要:针对CPCI 架构通用信号处理平台上利用系统自身以太网络接口实现数据传输效率低、扩展性差等问题, 提出一种采用高速Link 口基于FPGA 上硬核Pow erPC405 的嵌入式千兆以太网通信实现方案, 详细说明了以太网通信板卡的硬件和逻辑的实现, 并分析了TCP/ IP 性能最大化的技术。

传统基于CPCI 架构通用信号处理平台, 由于其并行CPCI 总线物理传输速率的限制, 加上存在以太网协议系统消耗, 造成通过主板网络接口数据传输效率很低, 远远不能满足雷达、声纳等复杂系统对网络通讯带宽的需求。

采用新型高性能FPGA 芯片, 利用高速Link 口4GByte/ s 传输带宽, 开发新的千兆以太网通信板, 实现以太网和高速Link 口数据的交互, 解决通用CPCI 架构信号处理平台之间数据传输的IO 瓶颈问题. 千兆以太网通信板是满足CPCI 规范的一个功能模块, 可以灵活的应用到模拟器、信号处理和数据采集等实际CPCI 架构系统中, 从而满足武器装备系统网络化、通用化、一体化、模块化的要求。

1 基于FPGA 的千兆以太网通信板的系统应用

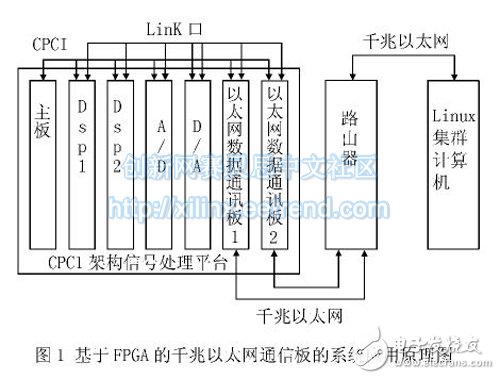

基于FPGA 的千兆以太网通信板在CPCI 架构通用信号处理平台上实现声纳模拟系统应用时实现框图如下图1 示, 模拟的声纳信号需要通过以太网传送给Linux 集群计算机。

在基于FPGA 的千兆以太网通信卡的信号处理平台上, DSP 板、A/ D 板、D/ A 板和千兆以太网通信板之间的高速、大容量数据交换是通过高速Link 口来实现的. 系统间的数据交互是通过千兆以太网实现的, 利用高速Link 口, 通过千兆以太网数据通信板,实现系统高速Link 口和千兆以太网的无缝衔接, 从而能够解决CPCI 总线带宽问题, 实现数据的和Linux 集群机等其他应用系统的共享和交互. CPCI 总线( 32 bit x 33 Mhz)主要用于实现系统主板和功能板卡( DSP板、A/ D 板、D/ A 板或千兆以太网通信板) ,以及功能板卡间数据互连, 完成系统控制、配置和低速数据传输等功能。

在CPCI 架构通用信号处理平台和Linux 集群计算机之间实现高速网络数据交互的实现主要工作是开发Link 链路口到以太网通信的CPCI 架构板卡。

2 基于FPGA 的千兆以太网通讯板卡的开发

本设计采用了基于Pow erPC405 处理器的SOPC 解决方案, 实现了基于FPGA 的高速嵌入式通信系统板卡, 数据通过千兆以太网实现系统间互连与共享, 主要介绍硬件和逻辑开发方面工作。

2. 1 通讯板硬件开发

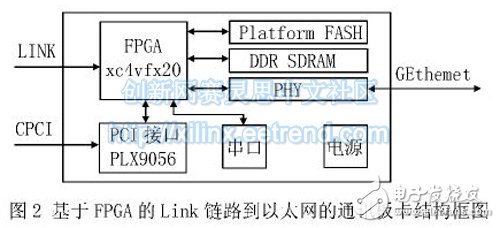

设计的千兆以太网通信板卡符合CPCI 架构U6 板卡标准, 是基于Xilinx XC4VFX20 系列FPGA, 内部集成了PowerPC405 处理器, 1 000 M 以太网MAC 模块, 运行频率高达300 MHz。

FPGA 实现Link 链路口数据到以太网MAC 层数据的转换. PCI 接口芯片本地总线的接口逻辑, 系统控制等功能. PLX9056 实现了CPCI 接口逻辑. 在板上扩展了两片MICRON 公司的256 Mb DDR 内存, 作为上电时操作系统的加载和运行空间. 采用Marvell 公司的千兆以太网PHY 芯片88 E1111 和带隔离器的RJ45 接口, 加上FPGA 中的MAC IP 核实现网络数据的传输功能. Plat form Flash 用于存储FPGA 配置文件和系统文件. 本设计扩展了1 个RS422 串行接口用于嵌入式软件的调试. 整个系统的硬件功能原理结构框图如图2 所示。

在进行威廉希尔官方网站 设计时, 要特别注意作为威廉希尔官方网站 核心器件FPGA 各个引脚的连接. 重要快速的时钟信号必须接到全局时钟引脚上; 和DDR、PHY 芯片连接引脚所在的BANK 需要提供电压参考要考虑DDR、PHY 芯片的工作电压; DDR 布线时, 数据和地址线要等长走线, 数据线之间误差控制在10 Mil 内, 地址线误差要控制在20 Mil 以内, 时钟也需要走差分等长线, 长度应大于地址线。

2. 2 FPGA 中逻辑开发

开发采用Xilinx 公司的EDK10. 1 和ISE10. 1 工具软件, EDK 称为嵌入式开发工具包, 由XPS( Xilinx Plat form Studio) , SDK( Softw are development Kit ) , Creat-Import peripheral 和Bash shell 组成. 开发者可以调用上述所有工具, 来完成整个的嵌入式系统开发. 在XPS 环境下添加所需的IP 核, 生成硬件系统框架;调用Platg en 生成嵌入式处理系统的网表文件( . NGC 文件) , 通过软件描述文件( . MSS 文件) 来设置系统软件配置, 并调用Libgen 生成驱动层和库; 在XPS 工程中添加应用软件项目并编写应用软件, 把EDK 中编写好的工程作为一个模块, 加入到ISE 工程中, 然后统一编译, 然后调用处理器对应的编译器编译并和硬件综合后生成的. bit 文件合成后下载到目标板便可以进行调试了。

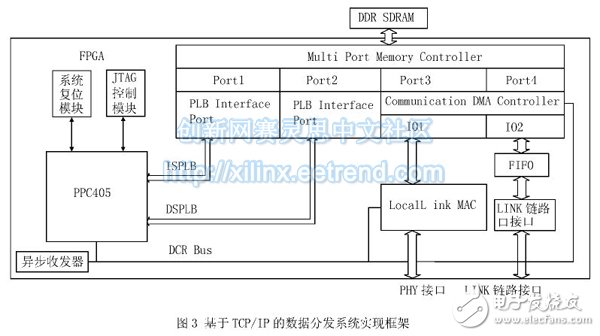

基于FPGA 的嵌入式千兆以太网的通讯功能实现逻辑如下图3 所示。 FPGA 中逻辑开发参考Xilinx 公司的GSRD 参考设计方案。 Virtex4 FPGA 芯片中嵌入了PowerPC405 处理器是针对嵌入式处理器开发应用推出的一种32 位嵌入式处理器内核, 它是一种硬核结构, 提供了相应的总线架构, 丰富的IP 核资源, 以及方便、高效的设计开发工具, 简单但灵活性强, 在目标器件中可以任意配置. 多端口存储器控制器( MPMC)有效分配了Pow erPC 指令/ 数据PLB 接口与一个通信用直接存储器访问控制器( CDMA C) 间的可用存储器带宽. CDMA C 通过Xilinx 标准Local Link 流线接口提供两个连接到外设的DMA 双向通道( 以太网接口数据通路和LINK 链路口通路)。 CDMAC 实现了数据重排, 用于支持存储器中的分组缓冲器的强制排列. Local Link 千兆位级以太网MAC( LLGMAC) 外设整合了经过U NH 测试的Xilinx LogiCORE 1-Gigabit 以太网MAC, 可以提供1 Gbps 1 000-BASE-X 以太网接口. LLGMAC 实现了发射通路和接收通路上的校验和卸载功能, 从而实现了最优的TCP 性能. 使用的是UartLite 模块, 设置需要的波特率和校验类型, 来实现异步收发器功能。

3 性能优化

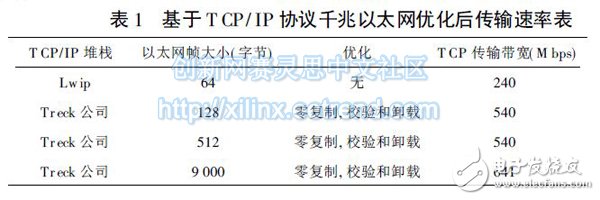

硬件确定好后, TCP/ IP 协议的系统消耗成为提高系统网络带宽的主要因素. 下面从单位字节、单位包的处理成本和系统架构三方面讨论实现千兆位以太网TCP/ IP 性能最大化的技术。

3. 1 TCP/ IP 单位字节处理成本

产生单位字节处理成本的两个最常见的操作是缓冲区复制和TCP 校验和计算. 可以引入零复制软件API 函数, 并将校验和计算利用FPGA 逻辑结构实现, 将有助于减少单位字节处理成本. Linux 和其他操作系统提供了类似的零复制特性, 已经引入了用于此目的的软件接口, 这些软件特性允许消除用户应用程序与TCP/ IP 栈或操作系统之间的缓冲区复制。

校验和卸载是以太网外设的一种特性. 它允许当以太网帧在主存储器与外设的硬件FIFO 之间传输时,在FPGA 结构中进行TCP 有效载荷的校验. 这些系统特性消除了代价较高的缓冲区复制与处理器校验和操作, 让处理器专心执行协议操作和用户功能. 可以在下面的实验数据中得到验证。

3. 2 TCP/ IP 单位包处理成本

包中断、硬件接口和头处理等数据发送与接收操作构成单位包处理成本, 特别是在传输小包时, 中断处理成本对处理器和存储器子系统构成相当大的负担. 利用NAPI 结合巨帧传输技术用来减少中断处理成本。

3. 3 系统架构

存储器带宽对高性能网络连接应用来说是一个重要考虑事项. 利用了多端口DDR SDRAM 存储器控制器, 在PowerPC 处理器本地总线( PLB) 接口与两个数据端口间分配存储器带宽. 每个数据端口连接到一个直接存储器访问( DMA) 控制器, 从而允许硬件外设对存储器进行高带宽访问。

系统的分散-收集与校验和卸载特性为零复制功能提供了所需的硬件支持. 分散-收集特性是DMA 控制器的一种灵活性, 它允许软件缓冲区位于任意字节偏移处. 这避免了处理器复制未对齐或碎片化的缓冲区。

对于需要使用嵌入式操作系统的应用, 可提供MontaVista Linux 端口和来自T reck 的商业独立TCP/IP 栈, 以满足具有最高带宽要求的应用。

4 性能测试

测试环境:

系统板卡: PPC405 Clock-300 MHz

MPMC/ DDR Clock-300 MHz

PLBv46 Clock-100 MHz

XPS_LL_T EMA C Clock-300 MHz

测试主机: Pentium( R) Clock-1 600 MHz

内存768MB

千兆以太网卡

Windows xp SP3

iPerf 网络测试软件

从测试的结果看, 利用经零复制, 校验和卸载优化过的Treck 公司的TCP/ IP 协议栈, 采用9000 Byte 巨帧可以实现高达641 Mbps 的传输速率。

5 结 论

通过开发的基于FPGA 的Link 口到以太网的通信板, 利用优化后的TCP/ IP 协议栈, 解决了原来CPCI架构信号处理平台上利用PCI 总线进行数据分发和转存的IO 瓶颈问题. 基于FPGA 的Link 链路到以太网的通信板已经成功应用于某型声纳信号模拟器上, 并且作为一个通用以太网数据分发模块可以应用于CPCI架构雷达、声纳信号处理和数据采集等系统应用领域。

-

如何利用FPGA中的高速串行I/O去实现嵌入式测试?2021-04-13 0

-

如何用FPGA实现嵌入式系统2009-04-02 7724

-

基于CPLD和嵌入式系统的高速数据采集系统的设计与实现2009-10-15 740

-

基于OpenBus系统的FPGA嵌入式设计与实现2012-11-26 823

-

基于FPGA技术实现对嵌入式系统的在线监控2014-07-22 2675

-

FPGA实现嵌入式系统2016-05-10 496

-

基于嵌入式Linux和FPGA的数据通信系统设计_陈鑫旺2017-03-16 707

-

在FPGA中实现嵌入式TCP/IP通信协议栈2017-11-17 8132

-

AltiumDesigner基于FPGA嵌入式系统设计2021-07-30 779

-

基于ARM的FPGA嵌入式系统实现2021-07-30 913

-

ARM11嵌入式系统实时网络通信和PWM波输出控制的实现2021-07-30 797

-

fpga与嵌入式的区别 嵌入式和fpga开发有什么关系2024-03-14 6896

-

fpga是嵌入式吗2024-03-14 2312

-

嵌入式fpga是什么意思2024-03-15 1256

全部0条评论

快来发表一下你的评论吧 !