通过FPGA器件和RS编码器实现前向纠错系统的设计方案

FPGA/ASIC技术

描述

1、引言

目前,无线产品的广泛应用使无线音频和视频的高质量传输成为可能。蓝牙、无限局域网等无线传输设备比较复杂,成本较高,急需开发一种简便的、仅用于流媒体的无线传输平台,将音频数据实时地发送到移动终端。由于音频数据的实时性,不宜采用反馈重传等造成很大时延的差错控制方式。前向纠错码(FEC)的码字是具有一定纠错能力的码型,它在接收端解码后不仅可以发现错误,而且能够判断错误码元所在的位置并自动纠错。这种纠错码信息不需要储存,不需要反馈,实时性好,故可选择前向纠错来实现差错控制。

设计的系统指标如下:

●当信道误码率为3x10-3时,经过前向纠错,误码率降到10-7以下;

●数据源使用的是S/PDIF民用数字音频格式标准;

●信号时延远小于人的分辨能力(40ms);

●芯片资源耗用不超过20万门;

RS码即里德-所罗门码,它是能够纠正多个错误的纠错码,具有同时纠正突发性错误和随机性错误的能力,而且编解码相对简单。考虑到系统的误码率和资源耗用,拟采用RS码作为前向纠错码。

在无线信道中,比特差错经常成串发生,这是由于持续时间较长的衰落谷点会影响到几个连续的比特,而信道编码仅在检测和校正单个差错和不太长的差错串时才最有效。为了纠正这些成串发生的比特差错及一些突发错误,可以运用交织技术来分散这些错误,使长串的比特差错变成短串差错,从而可以用前向码对其纠错。

用本系统传输数据时,在发端先对数据进行RS编码(外码),再进行交织处理,最后再进行RS编码(内码)。收端次序和发端相反,先进行内码解码,接着进行去交积处理完成错误分散,最后进行外码解码,纠正内码未能纠正的错误。通过这种2维的RS编解码,可以充分利用RS码纠错能力强的特点,降低系统的误码率。也可考虑使用迭代译码。若1次2维译码的效果无法满足需求,则将译码后的数据反馈回译码器,进行1次迭代译码。迭代次数的增加会带来相应的资源开销和时延的增加。

2、系统结构及实现

纠错编码使用2维RS码。内码采用(10,8)Rs码,q=4,每个码字含32bit数据。外码采用(20,16)RS码,q=8,每个码字含128个数据。交织器大小为1 280bit。以1 280bit为1帧,帧之间预留信息时隙。

下面详细介绍交织器,解交织器和(20,16)RS编码器,解码器模块的原理及FPGA实现。(10,8)RS编码器,解码器的原理与(20,16)RS编码器,解码器基本相同。

2.1(20,16)RS编码器

RS码是BCH码的重要子类。由于具有同时纠正突发性错误和随机性错误的能力,且纠正突发性错误更有效,因而被广泛地应用。

(20,16)RS编码器完成RS编码功能,每输入16个码元,延迟1个时钟原样输出,并在其后添加4个校验码元,构成20个码元的输出码字。因此数据输入16个码字后应预留至少4个码字的空隙,避免数据丢失。

(20,16)RS是(255,251)RS的缩短码,它是在有限域GF(28)上运算得到的,把(255,251)RS的前235个码元都当作0就得到(20,16)RS码。码参数如下:

码长N=20,信息位个数K=16,校验位N-K=4,纠错能力T=2,码距D=5;

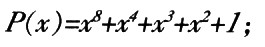

本原多项式:

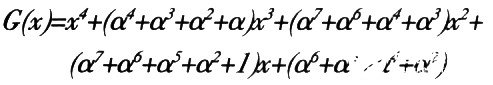

生成多项式:

其中,α是(20,16)RS的本原域元素。

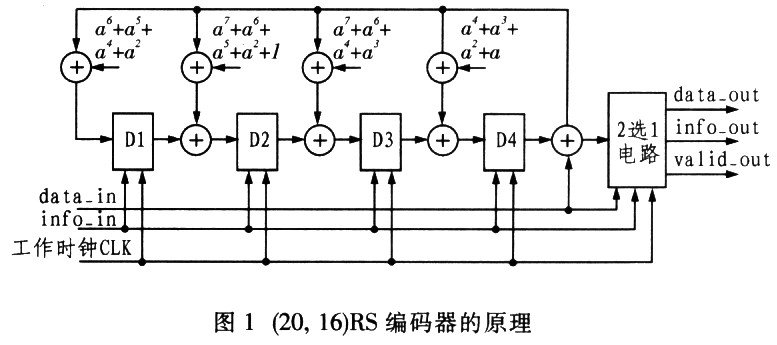

编码采用除法方式实现,其原理如图1所示。

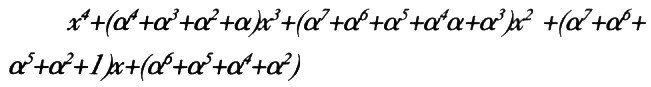

整个威廉希尔官方网站 实际上是GF(28)的除法威廉希尔官方网站 。图中乘单元的系数是生成多项式G(x)的对应项系数,对应的除法威廉希尔官方网站 的除数是

被除数的系数是输人数据的8bit码元,按照输入顺序进行降幂排列。第1个输入码元是x19的系数,最后1个输入码元是x4的系数。系数都是本原多项式P(x)生成的二元扩域GF(28)中的元素。在16个码字都输入后,寄存器D1-D4中保存的数据分别是常数项,x项,x2项和x3项的系数,它们就是所得到的校验码。数据选择威廉希尔官方网站 用来对不同数据进行选择输出。前16个时钟,输人数据按照顺序输出,后4个时钟输出计算得到的校验码。所有输出数据较之输入数据都要延迟1个时钟周期,时钟上升沿同步输出。威廉希尔官方网站 中的主要部分就是GFf(28)中的乘法单元和模加单元。

2.2(20,16)RS解码器

该威廉希尔官方网站 完成(20,16)RS码的解码工作,将20个8bit码元解码为16个8bit的码元。同时输出码字起始信号、数据有效信号和校验位有效信号。解码器的原理如图2所示。

RS码时域译码法主要有P-G-z法、B-M法和欧氏法。由于P-G-Z法要求解有限域上的逆矩阵,不利于实现,因此工程上很少使用。B-M法和欧氏法都是快速递归法,二者等效,易于硬件实现,因此得到广泛使用。在本次设计中,采用的解码算法是B-M算法。

RS码时域译码由以下几步组成:

(4)误码元错误幅度计算威廉希尔官方网站 。此模块的功能是当数据有错时(由s进行判断)计算错误码元的错误幅度。e是计算得到的错误幅度与相应码元相异或得到的值,可消除错误。如果当前码元无错,那么e=0。

(5)输入数据缓存FIFO。此模块的功能是将原始码字延迟一定周期输出,以便与错误幅度的输出同步。由双端口RAM构成的可复位。FIFO实现此功能。

(6)纠错威廉希尔官方网站 。此模块完成最后的纠错功能,通过与误码错误幅度e异或来实现。data_temp是从FIFO输出的数据。data_out即为纠正错误后的数据输出。以上整个纠错过程有43个时钟的延时。

(7)数据输出威廉希尔官方网站 。此模块主要完成2项功能:生成纠错失败信号fail和输出最终数据。fail信号的生成过程其实就是再求1次伴随式s。的过程。若计算出的s1不为0,则说明纠错不成功,将原始输入数据原样输出,同时fail信号输出高电平。否则,说明纠错成功,将纠错后的码字输出,。fail保持低电平。本过程有20个时钟的延时。

上面设计的解码威廉希尔官方网站 的关键就是GF(28)域中乘除法单元的硬件实现[6]。基于FPGA存储器资源丰富的特点,设计中采用了查:ROM表的办法来实现乘除功能。

整个威廉希尔官方网站 系统都在同一系统时钟CLK下工作,高电平复位。

2.3交织器组

本设计中,外编码器的输出按行进入1280bit的交织器,1个交织器存储32个外码码字,然后对交织器的内容按列读出。根据交织器的特性,需要将数据完全装入后才能读出。在读出时,不能向交织器内写数据。数据的输入是连续的,需要具有缓存功能的模块对数据进行缓存。采用1组2个交织器轮流读写的方法来保证数据的连续性。2个交织器的输出也是轮流进行的,当1个交织器填充完毕进行输出时,来自外码编码器的数据将被存储到另1个交织器中。交织器组的架构如图3所示。

本设计中,交织器的大小是1280bit,这主要是基于以下几方面的考虑。

(1)交织器不宜过大。由于必须完全写满后再读出,数据通过交织器的延迟与交织器大小成正比。因此,较大的交织器会影响整个系统的延时。所以,在保证效果的前提下,交织器要设计得尽量小。

(2)交织器的大小存在下限,即交织器有交织深度的最小限制[7]。以本设计为例,接收时第1级解码为(20,16),第2级为(10,8),则第2级的每个码字中不应有2个码元来自于第1级解码器的输出。否则,如果第1级解码器有未成功的解码(多于2个错误码元),则第2级解码器的输入码元中存在多于1个的错误码元的概率大大增加。因此,在本设计中,交织器的下限为第1级解码器的输出码字的10倍,也就是160字节。设计采用的交织器大小恰为下限。

3、系统验证及结论

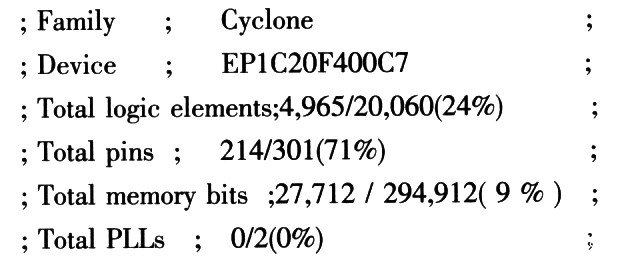

系统的整体实现与时序验证均使用Altera0uartusIl4.2和Modelsim5.7完成。FEC系统中各个模块及顶层控制部分全部使用VerilogHDI。设计。实现时选择的目标器件是Altera Cyclone公司的EPlC20F400C7。

对整个测试系统的编译结果如下:

在各种信道误码率和不同频率下进行了威廉希尔官方网站 测试,测试结果如表1所示。

根据以上分析,本设计达到了性能指标。当误码率适当降低时,纠错效果的提升非常明显。该系统在对S/PDIF格式的音频数据进行编码和解码时共延时3ms。若工作于更高频率,则延时可按比例减小。采用双相标识码串行输入作为数据来源时,数据吞吐量最大可达到32Mb/s,若采用其他数据来源,数据吞吐量最大可达178Mb/s。因此,此系统不仅可对音频信号进行前向纠错编解码,还可应用于数据量更大的视频信号等的其他数据传输。

责任编辑:gt

-

采用路径搜索的并行RS编码器IP自动生成方法2010-04-22 0

-

采用FPGA增量式编码器实现接口设计2019-06-10 0

-

如何实现CDMA2000系统前向链路卷积编码器?2019-08-27 0

-

RS通信编码器怎么进行优化设计?2021-05-06 0

-

汉明纠错编码器实例(VHDL源代码)2009-05-27 572

-

符合中国数字电视地面广播标准的前向纠错码编码器设计2009-12-13 397

-

RS连续编码器的FPGA设计与实现2011-09-02 864

-

基于FPGA增量式编码器的接口设计2011-11-03 773

-

用FPGA实现纠错编码的一种方法2011-11-10 906

-

LDPC码编码器的FPGA实现2016-05-09 739

-

RS编码的实现方法与基于FPGA的RS编译码器的设计2017-10-17 2805

-

一种改进的高速链路前向纠错编码2017-11-21 868

-

5 FPGA的杜比数码专业编码器(Xilinx)2018-10-24 480

-

基于FPGA的EnDat接口编码器数据采集设计2019-01-01 2223

-

如何使用嵌入式FPGA实现RS-CC的级联编码器设计2021-02-01 644

全部0条评论

快来发表一下你的评论吧 !