闲话Zynq UltraScale+ MPSoC(连载2)

FPGA/ASIC技术

206人已加入

描述

作者:Hello,Panda

Zynq UltraScale+ MPSoC架构

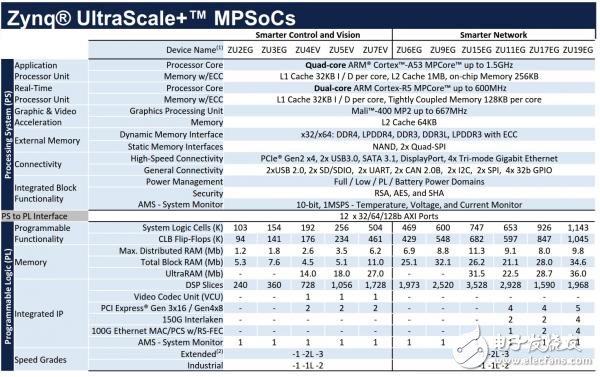

Xilinx新一代Zynq针对控制、图像和网络应用推出了差异化的产品系,这在Xilinx早期的宣传和现在已经发布的文档里已经说得很清楚了。她的产品系如图2所示。

图2 产品表

从图2看到,这个系列的Zynq算是8核(或9核)异构产品:四核的ARM-CortexA53 CPU、双核的Cortex-R5 RPU、Mali-400 GPU(一个Geometry核,两个像素核)、PL逻辑以及视频编解码器Codec核。

在表2中,ZU2E、ZU3E为针对控制类应用,逻辑和Block RAM资源较少,没有Video Codec和高速收发器。ZU4E、ZU2E和ZU7E针对视频类应用,有内部的UltraRAM资源、Video Codec和GTH高速收发器。其他型号针对网络应用,除了Video Code没有外,其它高大上的东西都有,比如更高速的收发器GTY,还有150G Interlaken和100G Ethernet MAC/PCS/RS-FEC等。

熊猫君是做图像的,下面的描述都是针对图像版的Zynq UltraScale+而言的。

因为PS部分的资源是固定的,大家都一样,在后面一起说就行。PL部分因为有这三个东西,将使设计如虎添翼:

a)大量的Block RAM和Ultra RAM资源,小20Mb的内部RAM资源,对分块处理图像,那应该会带来不少的便捷;

b)Video Code:这个东西是集成在PL侧的硬核,有了它,图像压缩和解压缩都不用愁了;

c)GTH:PL端集成的GTH收发器,对SDI、DP等图像接口接入那是十分的方便,当然也可以做PCIe咯。

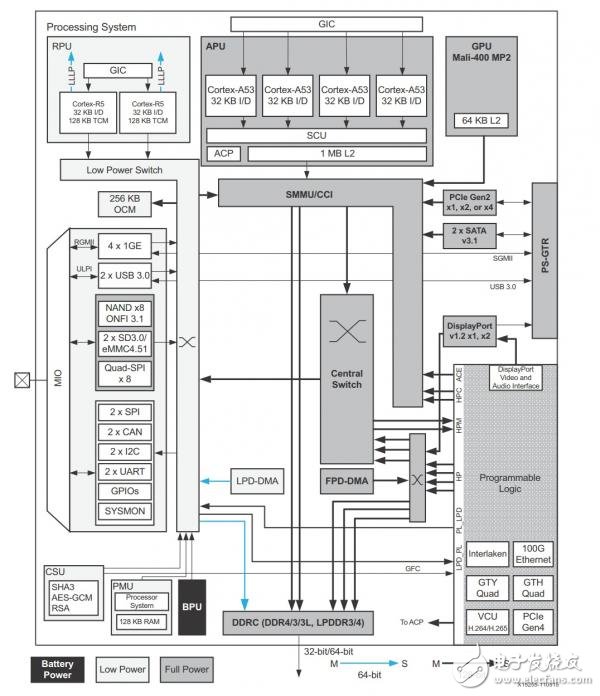

不多说了,熊猫君从Xilinx官方文档UG1085上截一个图来表示这个高大上通用SoC的系统级架构,也就是下面的图3啦。

图3 Zynq UltraScale+ MPSoC系统架构图

当初刚看到这个架构的时候,可高兴坏熊猫宝宝了,一连吃了好几框竹笋才勉强压了惊。冷静之余,还让熊猫君慢慢道来。

什么16nm级工艺的先进性啊什么什么各种先进技术的应用之类的咱不聊,那是Xilinx的事儿,咱就重点闲掰扯一下这货怎么用。目前熊猫君打算就以下几个方面入手:

(1)关于硬件设计的:

a) 电源系统和上电时序;

b) 启动加载;

c) IO资源;

d) 系统整体性能汇总(根据Xilinx提供的官方资料整理)。

(2)内部互联结构

可不要小看了这一部分,这是SoC的核心内容,所以单独拿出来。

(3)关于软件设计的

好吧,熊猫君也没有拿到试用版的开发套件,只能根据自己的认识+官方文档聊聊了。 附件大小

ok-chan_pin_biao_.jpg 61.32 KB

ok-xin_pian_xi_tong_tu_.jpg 67.76 KB

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

-

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器2021-01-07 0

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 0

-

闲话Zynq UltraScale+ MPSoC(连载1)2017-02-08 740

-

闲话Zynq UltraScale+ MPSoC(连载5)2017-02-08 729

-

闲话Zynq UltraScale+ MPSoC(连载4)2017-02-08 420

-

闲话Zynq UltraScale+ MPSoC(连载3)2017-02-08 502

-

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞2018-06-28 2674

-

Zynq UltraScale+ MPSoC的发售消息2018-11-27 3599

-

米尔科技Zynq UltraScale+ MPSoC技术参考手册介绍2019-11-18 3202

-

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?2021-02-23 1344

-

米尔电子zynq ultrascale+ mpsoc底板外设资源清单分享2022-01-07 616

-

Zynq UltraScale+ MPSoC中的隔离方法2023-09-13 371

-

Zynq UltraScale+ MPSoC的隔离设计示例2023-09-13 298

-

Zynq UltraScale+ MPSoC验证数据手册2023-09-15 328

全部0条评论

快来发表一下你的评论吧 !