FPGA学习之CRC校验

FPGA/ASIC技术

描述

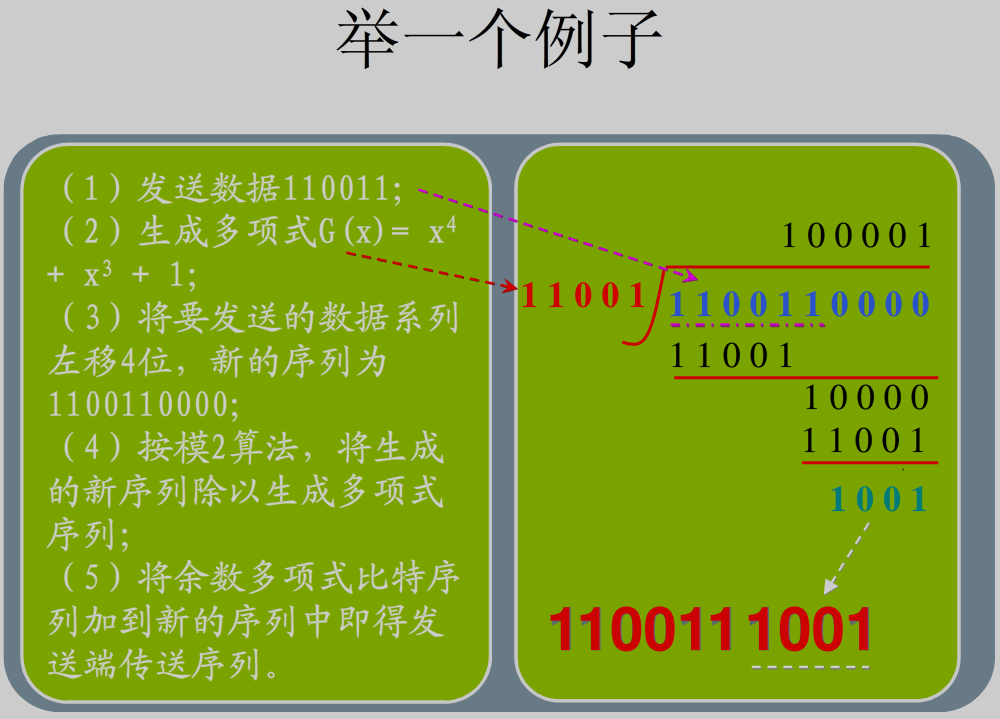

一、CRC原理。

CRC校验的原理非常简单,如下图所示。

其中,生成多项式是利用抽象代数的一些规则推导出来的,而模2加(也就是异或),是对应于有限域的除法。

二、CRC算法。

那么在FPGA当中,也有好几种算法。

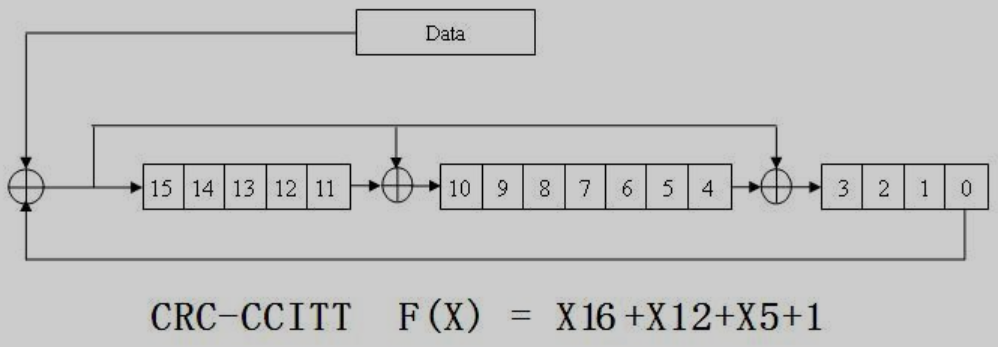

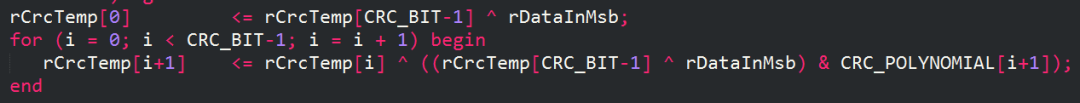

1、比特型算法。

这种算法,跟手算的差不多,一个时钟周期处理一个bit,速度慢,但消耗的面积小。

可能你会有疑问,本来是第15位(对应于x^15),再移位就是第16位,怎样把第16位转化成低于16位的数?

利用生成多项式就可以了,crc16 :1+x^2+x^15+x^16,类似于小学数学的约分。

下图为关键的代码。

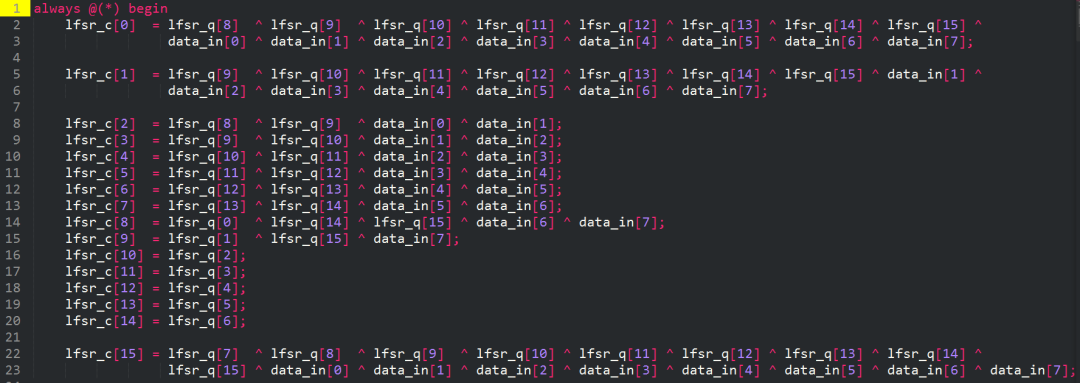

2、字节型算法。

原理是把上面比特型的算法展开,一次性把8个bit的情况都列出来,化简,如下图所示(只列出关键的代码)。

字节型算法的使用方法跟比特型类似,只是一次处理8个bit,算出来的crc,也要留在寄存器里面(LSFR)。

3、查表法。

跟字节型算法类似,把所有情况都算出来,存在一个表里,来一个byte查一次表。

三、常用工具。

介绍几个常用的crc工具(前4个为在线工具),除了可以计算crc以外,有的还可以自动生成c、verilog、vhdl代码。

1、CRC calculation

2、CRC Generator

3、On-line CRC calculation

4、Easics

5、CRC计算器

6、格西计算器

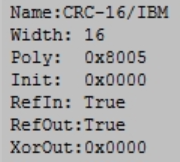

四、CRC参数模型。

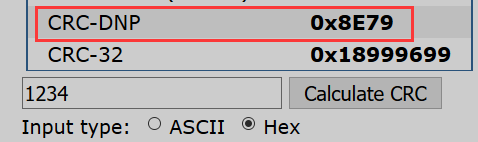

从上面两张图,可以看出来,这个CRC-DNP算出来的结果不为0(跟我们常识中的CRC不一样)。

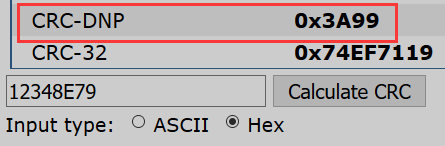

其实,这只是有少量改动的CRC而已,于是得到CRC的参数模型,如下图所示。

Name:CRC名称。

Width:CRC寄存器的位宽。

Poly:生成多项式(这里用16进制表示)。

Init:CRC寄存器初始值(图中为全0)。

RefIn:True代表每个输入的字节都倒置(原本是bit0的,换成bit7;原本是bit1的,换成bit6)。False代表不倒置。

RefOut:True代表在输出CRC结果之前,把CRC寄存器倒置。False代表不倒置。

XorOut:执行完RefOut之后,异或全0或者全1,(图中为异或全0)。

好了,搞懂CRC参数模型,才算是真正搞懂CRC,而不像书本上说的那么肤浅。

其中有的CRC寄存器初始值设置为全1,如以太网的CRC32,目的就是为了能检测出数据前面的0的个数。1234算出来的CRC,跟01234算出来的,不一样,这就能应对前面带0的数据了。

此外,CRC的生成多项式,也有可能倒置,所以必须以参数模型中Poly的值为准。

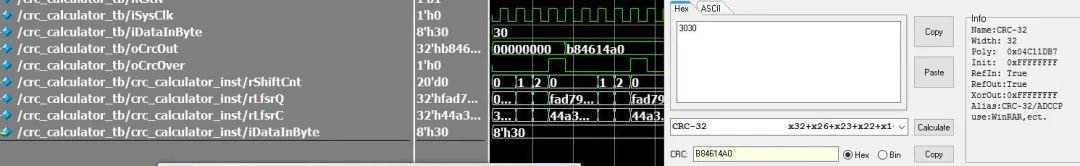

五、Verilog/VHDL的仿真和综合。

如下图所示,输入2个0x30,算出来的CRC32结果跟工具的一样。

关键的地方,在于倒置。

仿真器和综合器,支持的语法不同,所以在写倒置的时候,可能要尝试各种不同的写法(试出来),如果你使用工具不支持的语法,出来的结果可能是未知。

以下给出几种,可以尝试的写法。

1、reg [7:0] A;

reg [0:7] B;

assign A=B;

2、reg [7:0] A,B;

assign A = {B[0],B[1],B[2],B[3],B[4],B[5],B[6],B[7]};

3、reg [7:0] A,B;

assign A[0] = B[7];

assign A[1] = B[6];

assign A[2] = B[5];

assign A[3] = B[4];

assign A[4] = B[3];

assign A[5] = B[2];

assign A[6] = B[1];

assign A[7] = B[0];

4、reg [7:0] A,B;

integer i = 0;

for (i = 0; i <= 7; i = i + 1) begin

A[i] <= B[7-i] ^ 1'b1; // RefIn为False时,使用A[i] <= B[7-i];

end

不管是把输入数据倒置,还是把CRC寄存器倒置,原理都是一样的。

上面第三点的常用工具所生成的代码,都没做这一步的功能。使用时,请注意。

此外,在使用逻辑分析仪,查看CRC寄存器的数据时(比如,我这里是32位的reg变量oCrcOut),直接看oCrcOut结果是错误的,但是看下一模块的输入端口,却是正确的(中间有综合器生成的威廉希尔官方网站 )。

六、其它。

利用CRC算出来的值,不一定要为0才能使用,不为0也一样使用的(发送端跟接收端算出来的结果一样即可)。

一般,书上写的CRC参数模型初始值为全0,RefIn和RefOut为False,XorOut为全0。这样,接收端算出来的CRC结果为0。

更多的参数模型,可以下载第三点,常用工具的第5个工具,此工具包含21个CRC参数模型。

审核编辑 :李倩

-

FPGA实现CRC校验问题,求解答2014-12-03 0

-

FPGA实现CRC校验2015-01-05 0

-

请问FPGA怎么实现CRC校验?2019-05-21 0

-

CRC校验源码学习2010-08-13 1526

-

crc校验基本原理2011-12-21 4711

-

crc校验原理_怎样修复crc校验错误2012-09-05 34808

-

crc校验错误_crc校验错误怎么解决2017-12-05 47684

-

PIC24F系列参考手册之可编程循环冗余校验(CRC)2018-06-25 842

-

荐读:基于FPGA 的CRC校验码生成器2018-06-13 6506

-

CRC校验 、STM32中CRC计算单元、 CRC应用2020-03-04 6109

-

CRC校验码并行计算的FPGA实现2021-03-28 1426

-

CRC校验原理及实现2022-01-26 907

-

奇偶校验和crc校验的区别 CRC校验和奇偶校验之间有什么关系?2023-10-17 3406

-

fpga报告crc故障是什么意思2024-01-04 1485

-

CRC(循环冗余校验)应用举例2024-05-16 1211

全部0条评论

快来发表一下你的评论吧 !