功率和成本减半 Achronix交付先进22nm Speedster22i 系列FPGAs

FPGA/ASIC技术

描述

Speedster22i FPGA采用最先进的半导体工艺技术打造

2013年2月21日,中国深圳- Achronix Semiconductor公司宣布将其业界领先的22nm Speedster22i HD1000系列FPGA发运给客户,实现了又一个重大里程碑。22nm Speedster22i HD1000是Speedster22i FPGA产品家族的首个成员。该器件采用英特尔领先的22nm 3D Tri-Gate晶体管技术,其功耗是竞争对手同类器件的一半。

Speedster22i FPGA主要针对高性能有线通信、测试和高性能计算(HPC)等各种高带宽和低延迟的应用

Speedster22i FPGA充分采用了英特尔先进的22nm工艺特点,加上内嵌的嵌入式硬核IP,使得该器件相关应用方案广泛应用于包括测试测量、通信、数据中心等众多领域。

“Speedster22i FPGA主要针对高性能有线通信、测试和高性能计算(HPC)等各种高带宽和低延迟的应用,”Achronix总裁兼首席执行官Robert Blake说,“Speedster22i FPGA中的嵌入式硬核IP不仅简化了高带宽应用的设计,而且显著降低了解决方案的功耗和成本。”

Intel副总裁兼可定制晶圆代工技术与制造事业部总经理Sunit Rikhi指出:“我们很高兴Achronix能够成为我们的首家英特尔晶圆代工客户。首批Speedster22i FPGA的发货成为我们与Achronix多年战略伙伴关系的一个重要里程碑。”

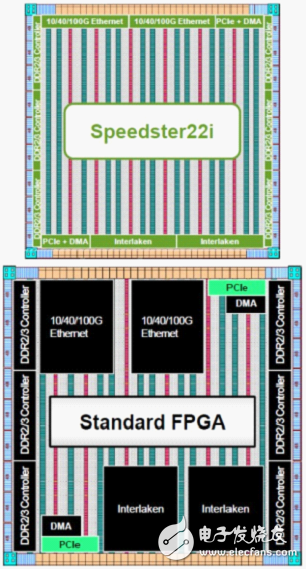

上图为Achronix公司Speedster22i与传统标准FPGA内核架构的对比。很明显,Speedster22i无论是在芯片总体设计尺寸和IP内核架构布局,均优于传统标准FPGA内核架构

22nm Speedster22i HD1000作为Speedster22i FPGA的首位成员。它包含了超过100万个查找表(LUT),包括70万个用户可编程查找表和30万个IP硬核的等效查找表。该器件还集成了86Mb的RAM、960个可编程IO以及64对12.75 Gbps的高速收发器。

功率和成本减半 均优于竞争对手的FPGA

Achronix在其FPGA中集成了高带宽和连接通信技术硬核IP。使用硬核IP的客户将可以节省一部分FPGA资源,否则该部分资源必须用来实现通信协议功能。这意味着在用以实现这些高带宽功能的Speedster22i器件中,其片芯面积要大大小于一片可完成相同功能的等量Altera或Xilinx器件。因此,Speedster22i器件相比于Altera和Xilinx的FPGA,可以实现功率和成本均减半。此外,Speedster22i器件中的硬核IP消除了这些高带宽功能的设计周期挑战,这也意味着整体的设计时间是在Altera或Xinlinx FPGA中构建同样功能的一半。

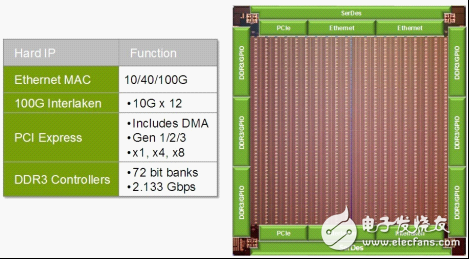

Speedster22i器件中用于10/40/100G以太网、100G Interlaken、PCI Express Gen3x8和2.133 Gbps DDR3的硬核IP

智能电网和智慧城市均有两个独立的部分:基础设施设备和终端应用。Achronix的高端FPGA将被用于构建高带宽数据传输的基础设施设备。这些应用都需要40G和100G以太网连接以及其它高带宽互联功能。HD 1000专为这些类型的设计而优化,带有了用于10/40/100G以太网、100G Interlaken、PCI Express Gen3x8和2.133 Gbps DDR3的硬核IP。根据Achronix公司高层透露,Achronix产品并不适用于终端应用。

关于Achronix Semiconductor公司

Achronix Semiconductor公司是一家总部位于加利福尼亚州的圣克拉拉的无晶圆厂半导体公司,它开发的针对应用的现场可编程门阵列(FPGA)产品以及ACE设计工具,它是首家英特尔可定制化晶圆代工的客户。如需了解更多信息,敬请访问Achronix Semiconductor公司网站:http://www.achronix.com。

-

高端FPGA市场明争暗斗 Altera为何选择英特尔?2013-03-07 3646

-

锐成芯微宣布在22nm工艺上推出双模蓝牙射频IP2023-02-15 0

-

联电宣布22nm技术就绪2019-12-03 5013

-

北斗22nm芯片用途是什么?2022-06-27 3183

-

台积电又跳过22nm工艺 改而直上20nm2010-04-15 989

-

Achronix全新Speedste r22i系列FPGA直接面向目标应用2012-04-24 1079

-

英特尔22nm 3D晶体管工艺,Achronix公布全新Speedster22i系列FPGA细节2012-04-25 1307

-

Achronix首款22nm技术工艺FPGA诞生2012-05-25 1624

-

Achronix全球首款22nm FPGA,瞄准高端通信市场2013-01-16 1589

-

Achronix开始交付其22纳米Speedster22i系列FPGA2013-02-21 1366

-

22nm和28nm芯片性能差异2022-06-29 9956

-

北斗星通22nm芯片先进吗?2022-06-29 3083

-

22nm芯片应用在哪些地方?2022-06-29 2154

-

22nm芯片是什么年代的技术?2022-06-29 5758

-

22nm平面工艺流程介绍2023-11-28 12764

全部0条评论

快来发表一下你的评论吧 !