最近在做一个项目时,我不得不对几组电子电线进行重新布线,让它们远离越野车的发电机,因为电容耦合产生的噪声可从发电机进入电线。这个项目让我想起了在通过电线、带状线缆或板对板连接器路由相互之间相邻信号时所遇到的类似情况。

2015-04-03 11:06:48 5011

5011

电源输出电容一般是100 nF至100 μF的陶瓷电容,它们耗费资金,占用空间,而且,在遇到交付瓶颈的时候还会难以获得。所以,如何最大限度减小输出电容的数量和尺寸,这个问题反复被提及。

2022-03-18 11:14:52 2472

2472

STPOWER MDmesh K6 新系列超级结晶体管改进多个关键参数,最大限度减少系统功率损耗,特别适合基于反激式拓扑的照明应用。

2021-10-26 11:53:38 823

823

模式2所产生的噪声电压Vn。R为电阻,C为电容,M为互感,Vs为噪声源电压,Is为噪声源电流。在这里请记住,平行的布线间会发生串扰。顺便提一下,如果布线是正交结构,则杂散电容和互感都会显著减少。关键

2018-11-29 14:29:12

之间产生 10 至 50 pF/ft 的电容,如下图 1 所示。图1. 带状线缆中相邻电线间的电容由于信号会相互干扰,两条信号线之间的电容会引起信号延迟、噪声耦合或瞬态电压。图 2 是电缆电容在通用双线

2018-09-19 10:55:31

解决方案,以最大限度地减少电源驱动设备的功耗、电压尖峰和过热。产品营销和应用经理Allen Chen表示:“我们依赖这些价值不菲的小装置中的电池可靠性,并尽可能长时间保持充电。您绝对不想让无人机在湖上

2019-08-09 04:45:04

请问如何最大限度的减小在汽车环境中的EMI?

2021-04-13 06:57:09

双ISP camera 芯片Android的应用软件一般情况下会用到其中的一种或者几种硬件,功耗主要来源于硬件,通过以下几种方式说明如何最大限度的降低应用软件的功耗。应用软件与可穿戴设备,例如智能

2018-09-19 18:11:19

随着现代微控制器和SoC变得越来越复杂,设计者面临着最大化能源效率,同时实现更高水平的集成。最大限度地提高能量在低功耗SoC市场中,多个功率域的使用被广泛采用。在

同时,为了解决更高级别的集成,许多

2023-08-02 06:34:14

DN249-LTC1628-SYNC最大限度地减少多输出,大电流电源中的输入电容

2019-06-17 08:42:47

PCB设计中如何处理串扰问题 变化的信号(例如阶跃信号)沿

2009-03-20 14:04:47

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且

2018-08-29 10:28:17

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号

2020-06-13 11:59:57

?对串扰有一个量化的概念将会让我们的设计更加有把握。1.3W规则在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。如(图1

2014-10-21 09:53:31

6mil,线间距为12mil,满足3W原则。图7为当RT=0.3ns 各个威廉希尔官方网站

的串扰图形。攻击线1V的驱动信号,受害线中微带线最大近端串扰为11mv,微带线最大远端串扰为12mv,带状线最大近端串扰为

2014-10-21 09:52:58

。将功率 MOSFET 并联时,设计人员必须更密切地注意如何最大限度降低这些影响,因为器件之间的电流分配不均会影响性能。例如,在开关瞬变过程中,在并联中增加一个器件会使 di/dt 倍增,从而可能导致

2022-03-24 18:03:24

模式2所产生的噪声电压Vn。R为电阻,C为电容,M为互感,Vs为噪声源电压,Is为噪声源电流。在这里请记住,平行的布线间会发生串扰。顺便提一下,如果布线是正交结构,则杂散电容和互感都会显著减少。关键

2019-03-21 06:20:15

串扰的概念是什么?到底什么是串扰?

2021-03-05 07:54:17

什么是串扰?互感和互容电感和电容矩阵串扰引起的噪声

2021-02-05 07:18:27

DN186- 优化的DC / DC转换器环路补偿最大限度地减少了大输出电容器的数量

2019-08-06 07:09:13

使用DMM和交换机系统时最大限度地缩短总体测试时间的技术

2019-08-15 14:35:47

相互作用时就会产生。在数字威廉希尔官方网站

系统中,串扰现象相当普遍,串扰可以发生在芯片内核、芯片的封装、PCB板上、接插件上、以及连接线缆上,只要有临近的铜互连链路,就存在信号间的电磁场相互作用,从而产生串扰现象

2016-10-10 18:00:41

DN247- 双相高效移动CPU电源,可最大限度地减小尺寸和热应力

2019-07-29 11:00:26

描述 此项 25W 的设计在反激式拓扑中使用 UCC28740 来最大限度降低空载待机功耗,并使用 UCC24636同步整流控制器来最大限度减少功率 MOSFET 体二极管传导时间。此设计还使用来

2022-09-23 06:11:58

在数字无线通信产品测试中最大限度地降低电源瞬态电压......

2019-08-19 07:42:24

在设计fpga的pcb时可以减少串扰的方法有哪些呢?求大神指教

2023-04-11 17:27:02

的电容,如下图 1 所示。图 1. 带状线缆中相邻电线间的电容由于信号会相互干扰,两条信号线之间的电容会引起信号延迟、噪声耦合或瞬态电压。图 2 是电缆电容在通用双线开漏通信总线中引起大量瞬态电压的实例

2022-11-23 07:51:41

电源输出电容一般是100 nF至100 μF的陶瓷电容,它们耗费资金,占用空间,而且,在遇到交付瓶颈的时候还会难以获得。所以,如何最大限度减小输出电容的数量和尺寸,这个问题反复被提及。输出电容造成

2022-06-14 10:19:20

电源输出电容一般是100 nF至100 μF的陶瓷电容,它们耗费资金,占用空间,而且,在遇到交付瓶颈的时候还会难以获得。所以,如何最大限度减小输出电容的数量和尺寸,这个问题反复被提及。 输出电容造成

2022-03-21 14:42:45

在测量电源噪声中我们会面临各种挑战,包括RF干扰和信噪比(SNR),接下来我们来看如何在测量中实现高带宽,同时最大限度地减少DUT上的电流负载?鉴于DUT是电源轨,我们不希望从它汲取太多电流。但是

2021-12-30 06:19:45

大家好, 昨天我刚刚得到了stm8s-discovery board。我不知道如何最大限度地利用它。因为我不知道用于stm的编译器来构建代码和关于STM的其他信息,直到今天我对AVR很熟悉请不要

2019-01-25 12:03:32

最大限度提高Σ-Δ ADC驱动器的性能

2021-01-06 07:05:10

如何最大限度的去实现LTE潜力?

2021-05-25 06:12:07

如何在密集PCB布局中,最大限度降低多个isoPower器件的辐射?请参考以下几个要点:*最大程度降低每个通道的电源要求*在多个PCB层上构建拼接*采用尽可能多的PCB层切实可行*在各参考层间使用最薄的电介质*在相邻域之间进行连接*确保内部和外部爬电距离仍然符合要求*电缆连接上提供过滤

2018-10-11 10:40:15

1394物理层所具备的优势是什么?如何采用1394技术最大限度地优化安全摄像头网络?

2021-05-25 06:25:20

在嵌入式系统硬件设计中,串扰是硬件工程师必须面对的问题。特别是在高速数字威廉希尔官方网站

中,由于信号沿时间短、布线密度大、信号完整性差,串扰的问题也就更为突出。设计者必须了解串扰产生的原理,并且在设计时应用恰当的方法,使串扰产生的负面影响降到最小。

2019-11-05 08:07:57

布局电源板以最大限度地降低EMI:第3部分

2019-08-16 06:13:31

布局电源板以最大限度地降低EMI:第1部分

2019-09-05 15:36:07

布局电源板以最大限度地降低EMI:第2部分

2019-09-06 08:49:33

许多高速数据采集应用,如激光雷达或光纤测试等,都需要从嘈杂的环境中采集小的重复信号,因此对于数据采集系统的设计来说,最大的挑战就是如何最大限度地减少噪声的影响。利用信号平均技术,可以让您的测量

2019-07-03 07:01:20

消除串扰的方法合理的PCB布局-将敏感的模拟部分与易产生干扰的数字部分尽量隔离,使易产生干扰的数字信号走线上尽量靠近交流地,使高频信号获得较好的回流路径。尽量减小信号回路的面积,降低地线的阻抗,采用多点接地的方法。使用多层板将电源与地作为独立的一层来处理。合理的走线拓朴结构-尽量采用菊花轮式走线

2009-06-18 07:52:34

在我的应用程序中,HSPDM 触发 EVADC 同时对两个通道进行采样。

我应该如何配置 EVADC 以最大限度地减少采样抖动并最大限度地提高采样率?

在用户手册中,它提到 SSE=0,USC=0

2024-01-18 07:59:23

外部之间的干扰,不得不说,串扰让线缆结构越来越复杂。在工程施工中,如何提高串扰呢?首先,在原材料上把好关。要对购买的整箱双绞线进行验货,只有通过验货测试,我们才能避免购买不合格的线缆或假线。而在验货环节

2018-01-19 11:15:04

,发送时间11ms左右,发现LDO的输出总是有5ms 0.3V压降,看手册,TPS2830可以提供150mA的电流。请问有什么办法可以最大限度的消除这个压降吗?谢谢!

2019-07-31 10:28:47

DN468- 通过精心的IF信号链设计最大限度地提高16位,105Msps ADC的性能

2019-09-04 14:09:04

DN371- 高效率2相升压转换器可最大限度地降低输入和输出电流纹波

2019-08-15 07:27:09

可能出现在威廉希尔官方网站

板、连接器、芯片封装以及线缆上。本文将剖析在高速PCB板设计中信号串扰的产生原因,以及抑制和改善的方法。

串扰的产生

串扰是指信号在传输通道

2018-08-28 11:58:32

数值比较接近。从图4中的仿真结果我们可以得出在上述实例中差分过孔间的串扰起主要作用。差分过孔间串扰的优化了解了此类问题产生串扰的根源,优化差分过孔之间串扰的方法就比较明确了。增加差分过孔之间的间距

2020-08-04 10:16:49

最大限度地减少组件的

2009-04-25 11:00:05 702

702

最大限度地减少组件的

2009-05-05 11:13:30 483

483

最大限度地减少组件的

2009-05-07 09:13:49 612

612

笔记本最大限度延长电池的使用寿命

本文将讨论如何有效地使用电池,以及最大限度地延长电池的使用寿命。本文将只讨论最新的XTRA这几个使用了锂电池的系列,对于较

2010-04-19 09:20:34 851

851 机器监测:通过性能测量,最大限度提高生产质量。

2016-03-21 16:34:53 0

0 Plunify®基于机器学习技术的现场可编程门阵列(FPGA)时序收敛和性能优化软件供应商,今天推出了Kabuto™,可最大限度地减少和消除性能错误。

2018-07-04 12:24:00 2657

2657 如果你是一名负责搭建嵌入式系统(或软件、设备、网络等)的工程师或开发者,那么你排在最高优先级之一的事情是(或应该是)鉴别并最大限度的减少潜在的数据安全漏洞。要想有效的实现这个目标,你需要了解系统是如何被黑客入侵的,最终要理解如何“像黑客一样思考”。

2018-07-13 14:54:00 878

878 放大器级的设计由两个彼此相关的不同级组成,因此问题变得难以在数学上建模,特别是因为有非线性因素与这两级相关。第一步是选择用来缓冲传感器输出并驱动ADC输入的放大器。第二步是设计一个低通滤波器以降低输入带宽,从而最大限度地减少带外噪声。

2019-07-29 11:29:37 1497

1497

在新冠肺炎疫情防控期间,要最大限度阻止病毒传播,关键是减少人与人之间的接触。旨在解决“最后一公里”配送问题的各大电商平台和无人配送公司纷纷加入战“疫”,无人配送车、无人机、配送机器人轮番上阵,在疫情

2020-03-13 08:53:07 3224

3224 对于高层建筑物来说,在消防设计中充分考虑建筑物的火灾事故隐患,最大限度的减少火灾事故造成的人员伤亡和财产损失,是一项及其重要的任务。高层建筑物一旦发证火灾事故,对人员生命威胁最大的是大量的有毒有害

2020-11-09 15:03:24 415

415 理想二极管桥控制器最大限度地减少整流器发热量和电压损失

2021-03-19 09:54:08 3

3 最大限度地减小汽车 DDR 电源中的待机电流

2021-03-20 17:22:52 1

1 LTC3555 - 开关模式 USB 电源管理器和三路降压型稳压器,可实现更快速的充电并最大限度地减少热量

2021-03-20 20:02:20 1

1 LTC3567 - 集成 1A 降压-升压型稳压器和 I2C 接口的开关模式USB 电源管理器最大限度延长电池工作时间并减少热量

2021-03-20 23:11:14 6

6 LTC3556 - 具开关模式 USB 电源管理器、一个降压-升压型稳压器和两个降压型稳压器的 PMIC 最大限度延长电池工作时间和减少热量

2021-03-21 08:17:26 9

9 DN468-精心设计IF信号链,最大限度提高16位、105Msps ADC的性能

2021-04-14 09:56:02 6

6 DN186优化的DC/DC变换器环路补偿最大限度地减少了大输出电容器的数量

2021-04-30 09:20:03 3

3 蓄能电池管理系统中最大限度提高电池监测精度和数据完整性

2021-05-18 11:08:07 4

4 DN468-精心设计IF信号链,最大限度提高16位、105Msps ADC的性能

2021-06-18 10:27:30 4

4 电子发烧友网站提供《最大限度地提高高压转换器的功率密度.doc》资料免费下载

2023-12-06 14:39:00 308

308 电线、带状线缆或板对板连接器路由相互之间相邻信号时所遇到的类似情况。

正如采用绝缘体隔离的任何其它导体一样,任何相邻布线的两条电线都会在其之间产生电容。根据所用的线规和绝缘体材料,大部分标准带状线缆

2021-11-21 16:30:13 1935

1935

每年消耗 25 万亿千瓦时的电力,其中 53% 是由传统电动机消耗的。因此,在减少碳足迹的同时最大限度地提高效率是一项强制性任务。

2022-08-04 17:22:02 2337

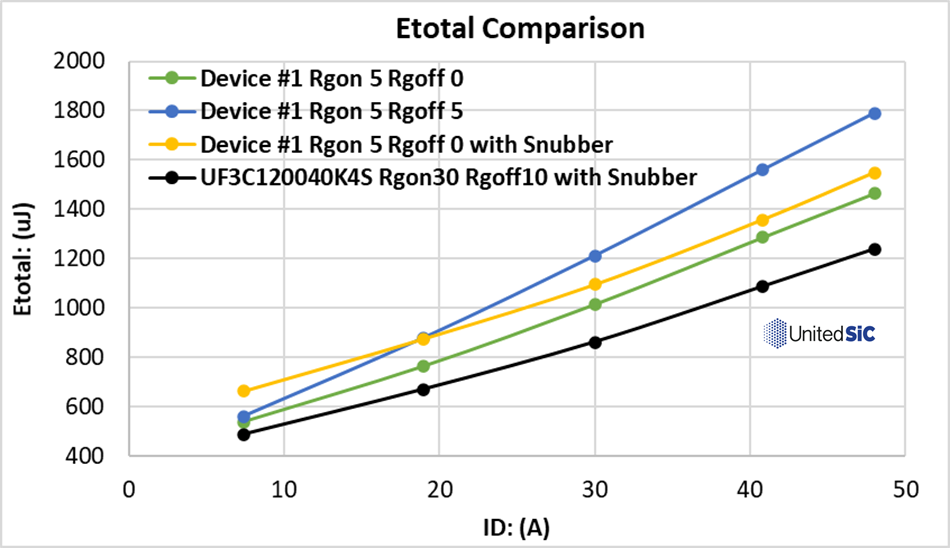

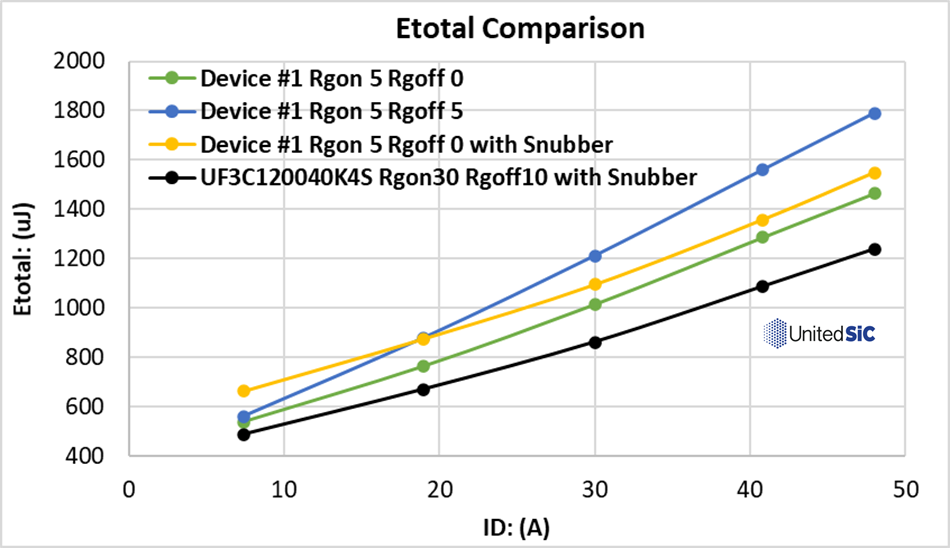

2337 SiC FET 速度极快,边缘速率为 50 V/ns 或更高,这对于最大限度地减少开关损耗非常有用,但由此产生的 di/dt 可能达到每纳秒数安培。这会通过封装和威廉希尔官方网站

电感产生高电平的电压过冲和随后

2022-08-04 09:30:05 729

729

智慧家庭系列文章 | 如何最大限度地减少智能音箱和智能显示器的输入功率保护

2022-10-31 08:23:54 0

0 一次性按钮开关帮助最大限度延长闲置时间

2022-11-04 09:52:06 0

0 时钟采样系统最大限度减少抖动

2022-11-04 09:52:12 0

0 如何最大限度减少线缆设计中的串扰

2022-11-07 08:07:26 1

1 AN2014_设计者如何最大限度使用ST单片机

2022-11-21 17:07:41 0

0 如何最大限度地提高电子设备中能量收集的效率

2022-12-30 09:40:14 616

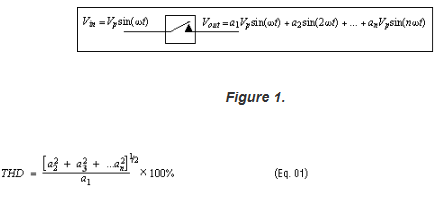

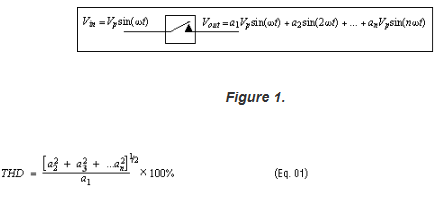

616 THD规格在确定通过音频系统或由音频系统生成的音频信号的质量或保真度方面起着至关重要的作用。因此,在设计音频系统时,必须重视选择合适的元件和威廉希尔官方网站

板布局,以最大限度地降低THD。

2023-01-16 15:55:45 1273

1273

使用直角齿轮电机最大限度地减少机器占地面积

2023-03-09 15:16:36 865

865

电子发烧友网站提供《最大限度地利用太阳能让您的家保持温暖.zip》资料免费下载

2023-06-13 15:20:06 0

0 电源输出电容一般是100 nF至100 μF的陶瓷电容,它们耗费资金,占用空间,而且,在遇到交付瓶颈的时候还会难以获得。所以,如何最大限度减小输出电容的数量和尺寸,这个问题反复被提及。

2023-06-16 10:25:19 372

372

开关稳压器,使用户能够在短短几分钟内查看大多数开关稳压器的波形。 精密的图形用户界面 LTspice是一种易于理解的电子威廉希尔官方网站

模拟器,它使用户不仅可以查看数值数据,还可以查看模拟结果的图形波形。 通过与LTspice 链接最大限度地减少设计重新设计并加速您的仿真 Quadcept允许用户为

2023-06-26 16:04:18 623

623

电子发烧友网站提供《最大限度地提高数据库效率和性能VMware环境使用32G NVMe光纤渠道.pdf》资料免费下载

2023-08-07 10:10:18 0

0 电子发烧友网站提供《使用端到端HPE StoreFabric Gen 5 16GFC光纤通道最大限度地发挥所有闪存的潜力.pdf》资料免费下载

2023-08-30 17:05:39 0

0 电子发烧友网站提供《切换以最大限度地利用SAN.pdf》资料免费下载

2023-09-01 11:23:25 0

0 最大限度地减少SIC FETs EMI和转换损失

2023-09-27 15:06:15 236

236

电子发烧友网站提供《最大限度提高∑-∆ ADC驱动器的性能.pdf》资料免费下载

2023-11-22 09:19:34 0

0 最大限度保持系统低噪声

2023-11-27 16:58:00 161

161

如何最大限度减小电源设计中输出电容的数量和尺寸?

2023-12-15 09:47:18 183

183

快充对电池有伤害吗 如何最大限度地减少快充对电池的影响 快速充电(也被称为快充)是一种可快速给手机电池充电的技术。虽然快充在我们日常生活中带来了便利,但很多人担心它是否会对手机电池的寿命产生负面影响

2024-02-19 10:01:02 308

308

电子发烧友App

电子发烧友App

评论