新版LabVIEW FPGA 新增特性详解及其带来的系统效率优化

虚拟仪器

描述

相比其它FPGA设计工具,NI LabVIEW FPGA模块可帮助嵌入式设计人员使用更少的工程资源更快速地完成项目。LabVIEW FPGA 2014 中新增多项性能提升,可以帮助您使用最新的技术在更短的时间内开发出高级的嵌入式和测试系统。该模块新增了一些强大的特性,旨在帮助您缩短开发时间,提高应用系统的性能。下面介绍了几个较为突出的新特性。

1. 为NI标准服务项目(SSP)会员提供的LabVIEW FPGA编译云服务

LabVIEW FPGA模块现在包含了LabVIEW FPGA编译云服务,专为拥有有效NI标准服务项目(SSP)会员资格的用户提供。LabVIEW FPGA编译云服务可将LabVIEW FPGA编译任务卸载到云中基于Linux的高性能服务器,从而提供了以下好处:

. 针对NI CompactRIO硬件减少了30%的编译时间,针对NI FlexRIO和矢量信号收发器(VST) 减少了60%的编译时间

. 可并行执行多个编译任务

. 释放开发计算机的资源

. 在编译过程中可随时关闭开发计算机

. 如果您选择不在本地安装Xilinx编译工具,则可节省硬盘空间(请参阅支持文档《何时需要安装Xilinx编译工具》?)

此外, LabVIEW FPGA编译云服务完全无需现场安装和维护。

2. LabVIEW FPGA编译集群工具包

LabVIEW FPGA编译集群工具包现在包含在LabVIEW FPGA模块中。如果您希望将LabVIEW FPGA编译任务卸载到现场工作站集群,而不是将编译任务发送到云端,那么LabVIEW FPGA编译集群工具包可为您提供所需的软件来创建现场服务器,以管理FPGA编译。您可根据需要连接多台编译计算机;中央服务器软件负责管理并行编译和队列之外的集群部署(farming)。为了减少您的FPGA编译时间,该工具包还提供了Linux编译工作站计算机支持。

3. LabVIEW FPGA IP生成器

LabVIEW FPGA IP生成器现在包含于LabVIEW FPGA模块中。LabVIEW FPGA IP生成器通过将高层次综合(HLS)技术与LabVIEW的强大功能相结合,可生成高性能FPGA IP。您可使用LabVIEW FPGA IP生成器来实现:

如需了解更多关于LabVIEW FPGA IP生成器,请查看利用NI LabVIEW FPGA IP 生成器针对FPGA优化和移植VI.

4. LabVIEW FPGA IP生成器优化

LabVIEW 2014 FPGA IP生成器包含了新的编程元素,可助您创建可移植的算法。新功能包括:

. 数组大小延迟检查: 数组可以具有可变的大小,前提是数组大小由生成的代码决定。这样您就可以创建一个可复用子VI来实现算法。同一个子VI可用用于不同的应用。

图1. 用于IP生成器的数组具有可变的大小

. 其他隧道模式:

串连隧道可用于创建IP来处理多维数组。LabVIEW FPGA IP生成器(和LabVIEW FPGA)不支持多维数组。不过,多维数组可以通过IP进行序列化和处理。串连隧道还可实现多维数组的重新组合。

条件隧道适用于多速率算法,比如抽样算法,其中输出端的元素数量与输入端的元素数量不相等。

图2. LabVIEW 2014 FPGA模块中的IP生成器可支持其它隧道模式

. 件禁用结构: T该功能用于创建可在桌面上或IP生成器环境内运行的可移植算法。.

图3. 条件禁用结构可以检测代码是在Windows环境还是在IP生成器环境中执行

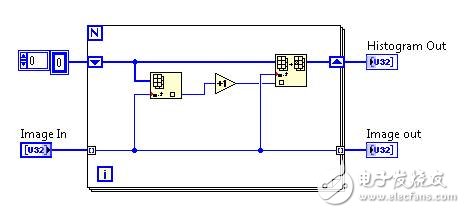

5. 用于LabVIEW FPGA的新视觉IP

NI视觉开发模块2014包含了50多种图像处理函数,可在FPGA上执行以实现最大处理性能,此外该模块还包含了一个用于在CPU和FPGA之间传递图像的API。对于快速原型,您可以使用视觉助手来自动生成FPGA、主机CPU以及两个硬件之间的接口所需的LabVIEW项目和VI。您可以使用LabVIEW FPGA IP生成器修改这个新视觉IP。

图4. 将新视觉IP卸载至FPGA硬件以实现最大处理性能

6. LabVIEW PID工具包

用于FPGA终端的LabVIEW PID工具包现在包含在LabVIEW FPGA模块中。LabVIEW PID工具包可用于在LabVIEW FPGA中实现单通道或多通道比例积分微分(PID)控制算法。所包含的PID(FPGA)Express VI实现了定点PID算法。该PID算法的浮点实现可参考技术白皮书LabVIEW FPGA PID控制器的浮点实现.

图5. LabVIEW FPGA的最新版本包括一个单通道或多通道PID控制算法

7. Kintex-7 LabVIEW FPGA终端的Xilinx Vivado支持

赛灵思公司开发的全新Kintex-7 FPGA和Zynq片上系统(SoC)实现了FPGA芯片时钟速率性能、低功耗、高速I/ O、容量、安全性和可靠性之间的完美平衡。借助LabVIEW 2014,在NI RIO硬件上使用Kintex-7 FPGA或Zynq SoC的开发人员也可受益于赛灵思的最新编译技术。新Xilinx Vivado编译工具提供了几个好处,包括:

. 更可靠、一致的时序收敛

. 提高资源利用率

. 可提高之前使用Xilinx ISE的Kintex-7 FPGA和Zynq SoC硬件(NI cRIO-9068和NI PXIe-7975R)的编译速度

图6. Xilinx Vivado可减少Kintex-7和Zynq SoC硬件的编译时间

如需查看使用Kintex-7 FPGA的所有NI RIO硬件的列表,请参阅支持文章哪些Xilinx FPGA芯片用于NI RIO设备?

8. FIFO的四线握手API

四线握手通常用于高吞吐量数据流应用。而先入先出内存缓存区(FIFO)通常用于这些应用的处理单元之间传输数据。因此,FIFO的新四线握手接口使您能够轻松将FIFO集成到高吞吐量设计中。

图7. FIFO的四线握手API使您能够轻松将FIFO集成到高吞吐量数据流应用中

9. 高性能BRAM

Xilinx块RAM的输出端具有可选的寄存器。通过启用这些寄存器,您可以有效地分配内存和断开关键路径,并以更高的时钟频率合成您的设计。需要注意的是,启用寄存器会增加访问内存的延迟,这时需要添加等于或大于配置的延迟周期的反馈节点。

图 8 充分利用高性能BRAM以更高的时钟频率合成您的设计

-

NI 发布 LabVIEW 2011,将开发效率提升至新的境界2011-08-02 0

-

Labview 下建立dll及其使用方法详解2011-12-05 0

-

Linux系统命令及其使用详解2012-08-20 0

-

《FPGACPLD设计工具──Xilinx+ISE使用详解》2017-11-02 0

-

OpenHarmony 3.0 LTS 新增特性功能2021-09-30 0

-

网络讲坛:实时系统与FPGA-labview视频教程2010-03-26 975

-

NI LabVIEW 8.6 全面简化嵌入式系统原型构造与发2008-08-12 580

-

最新版LabVIEW软件帮助用户高效使用多核、FPGA、无线2008-08-12 531

-

LabVIEW Robotics 2010图形化系统设计软件2011-03-25 1645

-

LabVIEW串口通信详解2016-03-15 2648

-

SVPWM算法优化及其FPGA_CPLD实现2016-04-13 542

-

基于LabVIEW与FPGA的飞行训练弹测试系统设计_刘克轩2017-02-07 558

-

新版LabVIEW FPGA从三个方面优化你的测试系统设计2017-11-18 5857

-

LabVIEW 2015 (32-bit) 官方软件下载2018-04-13 1052

-

如何利用Xilinx成本优化的FPGA和SoC产品组合的最新增强功能2018-11-28 2331

全部0条评论

快来发表一下你的评论吧 !