总体描述:

ADSP-TS201S TigerSHARC处理器是-款超高性能针对大信号优化的静态超标量处理器性能处理任务和通信基础设施。

数字信号处理器结合了非常宽的内存宽度和双重计块一支持浮点(IEEE 32位和扩展40位精度)和定点(8位、16位、 32位和64位)pro ,处理一一设定数字信 号性能的新标准处理器。

TigerSHARC静 态超标量体系结构允许DSP每个周期执行多达四条指令,执行24次定点(16位)运算或6次浮点运算

运营。

四条独立的128位宽内部数据总线,每条总线都包含连接到六个4M位内存组,启用四字

数据、指令和I/O访问,每个提供33.6G字节内存芾宽的秒。

工作在600 MHz ,ADSP-TS201S处理器的内核有-条1.67 ns的指令周期时间。

使用它的单指令多数据(SIMD)特性,ADSP-TS201S处理器可以执行48亿、40位MAC或每秒12亿台80位MAC。

支持硬件和软件的中断控制器ware中断,支持电平或边沿触发,以及支持优先的嵌套中断四条128位内部数据总线,每条总线连接六个4M位存储体片上DRAM (24M位)为主机进程提供接口的外部端口sors.多处理空间(DSP)、片外存储器~映射外设以及外部SR AM和SDRAM一个14通道DMA控制器四个全双工LVDS链路端口两个64位间隔定时器和定时器到期引脚一个符合1149.1 IEEE标准的JTAG测试接入端口

关键特征

最高600 MHz, 1.67 ns指令周期速率

24M位内部片上DRAM存储器

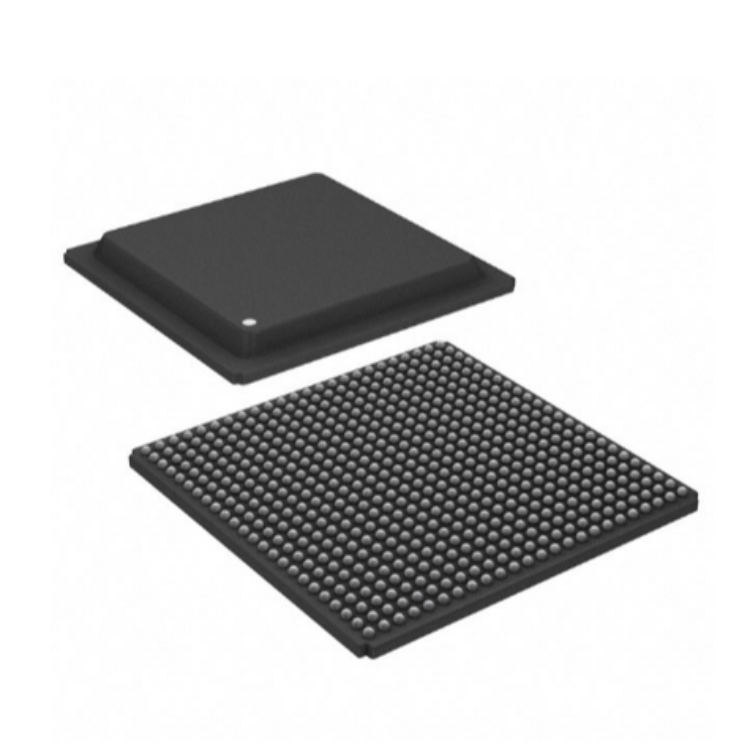

25 mm x 25 mm (576引脚)散热增强型球栅阵列封装

双计算模块一每个模块包含一个ALU. -一个

乘法器、移位器、寄存器文件和通信逻辑单元(CLU)

双整数alu,提供数据寻址和指针操纵

集成I/O包括14通道DMA控制器,外部端口,四个链接端口, SDRAM控制器,可编程系统的标志引脚、两个定时器和定时器到期引脚

综合符合1149.1标准的片内JTAG测试访问端口竞争

单精度IEEE 32位和扩展精度40位浮点数据格式以及8位、16位、 32位和64位定点数据格式.

主要优势:

提供高性能静态超标量DSP运营,针对电信进行优化

基础设施和其他大型、高要求的多处理器DSP应用

在DSP算法和I/O方面表现出色基准

支持内部之间的低开销DMA传输

存储器、外部存储器、存储器映射外围设备,

链接端口、主机处理器和其他(多处理器)DSP

通过极其灵活的指令简化DSP编程

指令集和高级语言友好的DSP体系结构

支持低通信量的可扩展多处理系统

通信开销为无缝多处理提供片内仲裁

ADSP-TS201SYBP-050

ADSP-TS201SABPZ050

ADSP-TS201SABPZ050

ADSP-21488BSWZ-3A

ADSP-21369KSWZ-2A

ADSP-21061KS-133

ADSP-BF533SBBC500

ADSP-21065LCSZ-240

ADSP-21262SKSTZ-200

ADSP-BF561SKBZ600

ADSP-BF537BBC-5A

ADSP-BF524BBCZ-4A

ADSP-TS101SAB1Z100